原子芯片的基本原理、關鍵技術及研究進展*

李沫 陳飛良 羅小嘉 楊麗君 張健

1) (電子科技大學電子科學與工程學院, 成都 611731)

2) (中國工程物理研究院電子工程研究所, 綿陽 621999)

1 引 言

中性原子的冷卻、囚禁、導引等操控技術的發展, 不僅深化了人們對微觀物質基本規律的認識,而且極大地拓展了原子物理學的應用范圍, 構建了一系列具有顛覆性、變革性的測量、傳感與信息處理裝置.傳統的冷原子實驗系統組成非常復雜, 包含激光系統、真空系統和電磁系統等部件, 成為其在體積和重量有嚴格要求的場景中應用的重要制約.受微納加工技術和集成電路發展理念的啟發,人們提出將原子操控裝置微型化甚至實現片上集成來推動冷原子技術走向實用.原子芯片(atom chip)正是依據這一理念, 基于微納加工技術實現的具備特定微結構的原子操控器件, 通過在微尺度條件下產生可調控的光場、電場或磁場來實現對冷原子云、玻色-愛因斯坦凝聚(BEC)或帶電粒子的內部或外部自由度的操控.原子芯片技術始于20 世紀90 年代初, 科學家在實現自由空間冷原子的控制后, 開始探索利用自支撐導線對原子進行導引, 期待獲得與原子德布羅意波長尺度接近的微勢阱并可在芯片上對原子進行有效操控的目的.1995 年,Schmiedmayer 團隊[1,2]率先實現了原子芯片微導線原子勢阱; 1999 年, Reichel 等[3]利用微加工技術實現了芯片上鏡面磁光阱對中性原子的囚禁;2001 年, 德國H?nsel 小組[4]進一步實現了原子芯片上中性原子BEC.自此, 原子芯片引發了科學家們的廣泛興趣, 得到了迅速發展.與宏觀線圈相比,原子芯片具有功耗低、尺寸小、磁場梯度大、束縛強、可以靈活設計不同形狀的勢阱等獨特優勢[5].特別是原子芯片上可以產生閉合導引, 使原子物質波波包能在保持良好相干性的情況下往返運動, 解決自由空間難以形成大面積閉合環路且噪聲干擾大、Raman 分束器的性能受限于雙光子反沖的限制, 這對原子干涉陀螺儀具有極為重要的意義.除在芯片上構造微勢阱、微導引的原子芯片外, 利用MEMS 等微納技術將原子氣室及部分量子光學部件進行片上加工與集成也被認為是芯片級的原子技術.目前, 原子芯片的操控對象已擴展到里德伯原子、冷分子、帶電粒子, 芯片類型從金屬導線原子芯片拓展到超導原子芯片、磁性薄膜原子芯片、光晶格及超表面原子芯片等, 從最初的單一磁阱結構逐步向將光源、探測器、微透鏡、光開關、光波導、微腔等多功能片上集成的方向發展, 內外態操控手段日益豐富與成熟[6-10], 成功地在原子干涉儀、原子重力儀、量子信息處理、芯片級原子鐘、芯片級原子磁力計等場景得到應用, 并有潛力拓展到引力波探測、暗物質探尋等基礎領域, 有望改變傳統量子光學與原子物理實驗裝置復雜、龐大、笨重的限制, 建立一個強大的量子基礎與應用的片上實驗平臺, 為人們開展更多自由度、更復雜精準的宏觀量子研究提供重要的手段.鑒于原子芯片展示出的極大潛力和已經獲得的豐碩成果, 本文將對原子芯片, 特別是載流導線型原子芯片相關的基本原理與關鍵實現技術、國際相關研究布局與主要進展進行綜述, 并且探討該技術面臨的挑戰性問題和未來發展趨勢.

2 原子芯片上原子操控的基本原理

對中性原子冷卻、囚禁、反射、偏轉、準直以及衍射、分束、干涉、導引等可統稱為對中性原子的操控, 其實現方式主要包括電、光、磁3 種, 依賴于電場、光場或磁場與原子感應電偶極矩(或磁偶極矩)的相互作用[11].本文主要介紹采用微納加工技術制作的芯片上載流導線所產生的磁場對中性原子進行操控的相關內容.

2.1 原子芯片上的微勢阱

大部分的宏觀靜磁阱(尺寸為1—100 cm)通過大型通電線圈、超導線圈或永磁體等產生.在芯片上利用微納加工制作出特定結構的導線, 通電后產生的磁場與外部偏置磁場相結合可以構造與宏觀效果類似的微磁阱, 并且得益于襯底對載流導線的優異散熱性能, 可以產生很大的電流密度和磁場梯度, 很容易實現如四極阱[12]和Ioffe-Prichard阱(IP 阱)[13]等靜態阱以及與時間相關的動態阱[14,15].

常見的微磁阱主要有如下幾種構型.

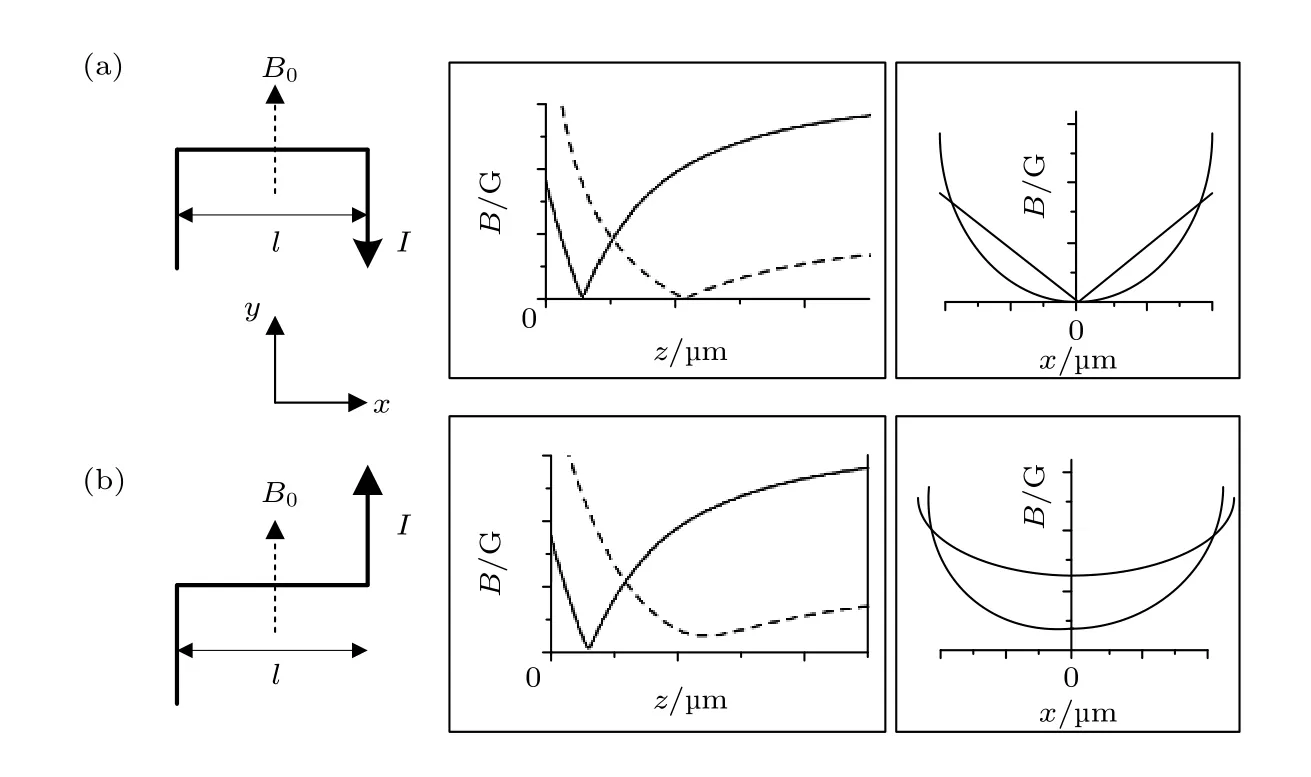

1) 簡單結構的三維微磁阱.將一根直導線彎折成U 形或Z 形, 通電后再輔以外部偏置磁場就可以構成微磁阱, 如圖1 所示.當直導線折成U 形時, U 形兩邊所產生的磁場在阱的中心相互抵消,形成一個零場區域.由于原子在經過磁場零點處可能因為馬約拉納躍遷由束縛態轉變為非束縛態而從磁阱中逃逸, 因此消除磁阱的磁場零點非常重要, 如通過時間軌道平均勢(time-orbiting potential,TOP)的方法來消除[16].當直導線折成Z 形時,Z 形阱的中心磁場是兩個折彎的部分產生的磁場的疊加, 是一種沒有零點的靜磁IP 阱[17].計算U形和Z 形阱的磁場性質時需要考慮導線的有限尺寸效應及彎曲部分的折向等因素的影響, 對于不同的導線結構所產生的總磁場, 可以通過數值疊加不同部分所產生磁場來獲得[3,18].

圖1 (a)由U 形阱形成的四極磁阱; (b)由Z 形阱形成的IP 阱[3]Fig.1.(a) Quadrupole trap by U configuration; (b) Ioffe-Pritchard trap by Z configuration[3].

2) 基于交叉導線結構的表面微磁阱.在垂直于側邊導引的導線方向加上一根直導線, 會在導線交叉位置上方形成dimple 阱[19,20], 如圖2(a)所示.在y 方向電流較弱的情況下, dimple 阱可以認為是一個由x 方向導線形成的四極阱和y 方向導線形成的磁場的疊加, 形成的雪茄型阱的方向取決于偏置場方向.此時額外添加一根載有相同大小電流的導線即可得到兩個磁場極值, 這種結構被稱為H 形阱, 如圖2(b)所示[20].對應于y 方向兩根導線的相對電流的方向(平行或者反平行)的不同, H形導線結構也可以實現四極阱或IP 阱.

圖2 (a) Dimple 阱; (b) H 形阱[20]Fig.2.(a) Dimple trap; (b) H-type trap[20].

3) Weinstein-Libbrecht 阱.1995 年, Weinstein和Libbrecht[21]巧妙地提出了實現IP 阱的平面載流導線設計方案, 圖3 為幾種典型結構[21,22]: 圖3(a)由3 組同心半環組成; 圖3 (b)由兩組同心半環和一個外加偏置磁場組成; 圖3 (c)由一個半環、一個圓環和一個偏置磁場組成, 基本結構與圖3 (b)類似, 不同之處在于其軸線的磁場梯度更大而徑向的磁場梯度更弱, 這意味著相同的電流強度可以得到更深的勢阱; 圖3 (d)由兩個圓環、一個偏置磁場和額外的Ioffe 棒組成.

圖3 四種平面Ioffe 阱的方案[22]Fig.3.Four planar Ioffe trap configurations[22].

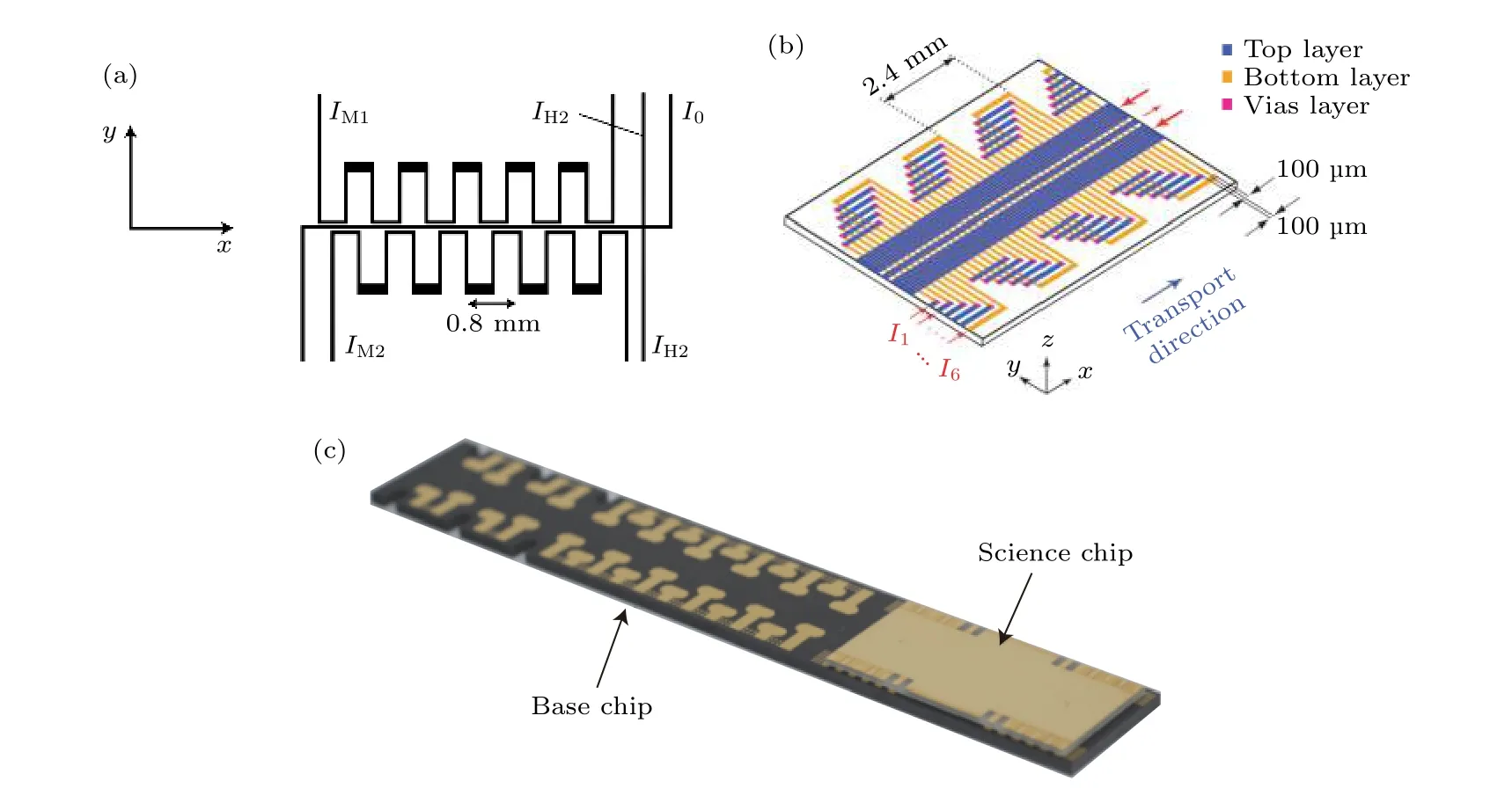

4) 復雜結構微磁阱, 如原子傳送帶.圖4(a)是最早實現的原子傳送帶結構[23].后續研究人員在此基礎上提出改進的雙層原子傳送帶, 可以工作在有偏置磁場和無偏置磁場兩種模式下, 具有6 通道獨立的電流, 通過將單軸線改為3 根平行線來代替外部偏置磁場的作用, 顯著提升了傳送的性能, 原子的線性傳送距離為6 cm, 總傳送距離可達24 cm, 如圖4(b)所示[24].近期科研人員提出了基于氮化鋁(AlN)基底的原子傳送帶結構, 如圖4(c)所示.該結構包括兩個部分, 其中science chip 部分包含利用金導線制作的Z 形阱、U 形阱和mirror-MOT, base chip 部分則是多陣列銅導線的原子傳送帶結構.87Rb 冷原子團在該傳送帶中以40 mm/s的速度運動, 比前期文獻報道[25]的原子運動速度5.3 mm/s 幾乎提高了1 個數量級.

除上述的幾類勢阱外, 還有一類相對復雜的雙勢阱.如華東師范大學印建平等[26,27]提出了雙Z 形和雙U 形載流導線的微磁阱.雙Z 形磁阱由一個Z 形載流導線、一根載流直導線和一個偏置磁場構成, 調節Z 形載流導線和直導線中電流的相對強度可以實現從微磁雙阱到單個阱的演化, 用于雙樣品BEC 的制備以及BEC 干涉實驗的研究.雙U 形微磁阱由兩根U 形載流導線組成, 它們載流方向相反, 通過調節電流的大小可以實現單磁阱到雙磁阱的轉變.

圖4 多種原子傳送帶結構[23-25]Fig.4.Multiple configurations of atom conveyor belts[23-25].

圖5 基于(a)金字塔結構[29], (b)光柵結構[33]的芯片微MOTFig.5.Micro-MOTs chip based on (a) micro-paramide arrays[29] and (b) gratings[33].

原子芯片上微磁阱產生的勢阱深度有限, 且距離芯片表面一般很近, 很難直接從真空囚禁原子,因此一般首先用磁光阱(MOT)將原子冷卻和囚禁, 然后轉移裝載至芯片微磁阱中[28].傳統的MOT需要3 對互相垂直的激光束, 在原子芯片上應用需要發展新的方法, 避免芯片對激光的遮擋.H?nsch小組[3]最早提出了微型mirror-MOT 方案, 他們將U 形金載流導線刻蝕在氧化鋁陶瓷基底上, 用濺射技術鍍一層200 nm 厚的銀膜提高對激光的反射率, 成功將6 束激光系統簡化為4 束激光系統, 實現了87Rb 原子的表面囚禁.后續國際上提出了一系列微型mirror-MOT 或相似的方案, 如反射鏡金字塔結構或者光柵結構, 都實現了冷原子的囚禁, 比傳統的光學系統體積降低了接近100 倍, 功耗降低了近1/10, 如圖5(a),(b)所示[29-33].最近南方科技大學聯合英國伯明翰大學等單位利用介質超構表面光學芯片實現了對原子的囚禁和冷卻, 俘獲的原子數約為107個, 原子溫度約35 μK,通過進一步的蒸發冷技術有望實現芯片上的BEC[34].

2.2 原子芯片上的導引

嚴格意義上講, 原子導引和原子波導有一定區別: 原子導引是指原子導管的橫向尺寸遠大于原子的波長, 原子在導管內以粒子的形式存在, 其運動軌跡可用射線光學來處理; 原子波導是指原子導管的橫向尺寸約等于原子的波長, 原子在導管中以物質波的形式存在, 屬于波動原子光學的內容[11].一般文獻中沒有對二者進行特別區分, 本文統一使用原子導引這一表述.

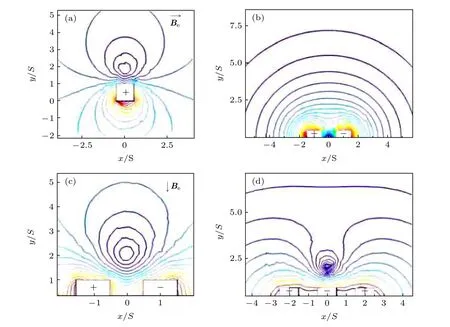

圖6 (a) 側邊導引; (b) 共面成對同向載流的側邊導引; (c) 共面成對異向載流的側邊導引; (d)三線導引.圖中S 為導線間距Fig.6.(a) Side guide; (b) two-wire side with co-propagating currents; (c) two-wire side guide with opposing current directions;(d) three-wire guide.S is the distance between wires.

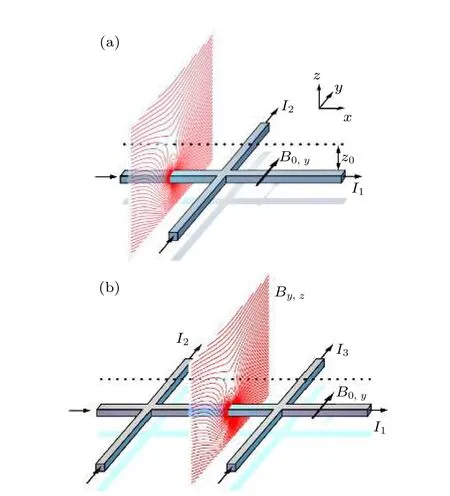

本節仍主要關注基于原子芯片上載流導線的磁導引方案.常見的磁導引如圖6 所示, 包括: 1) 基于單根載流導線產生的磁場與外加偏置磁場的疊加, 如原子繞著載流導線運動的Kepler 導引[1], 以及原子在二維四極場內沿著磁場最小的方向線運動的側邊導引等[22]; 2) 基于兩條平行載流導線所產生的磁場與外置偏置磁場的疊加, 包括共面成對同向載流導引和共面成對異向載流導引[22];3) 基于多條平行導線產生的磁導引[35,36], 其優勢在于可以通過載流導線自身產生偏置磁場, 不需要外加宏觀線圈的輔助[37]; 4) 通過將平行載流導線彎曲成同心環或基于不同復合導線結構實現的環形導引, 具有閉合環路面積大、結構對稱、能夠消除共模噪聲等優點.但該導引往往存在由于電流引線引發的導引缺口.針對于此,有科研人員提出了七線布局的雙層原子芯片、雙相位射頻電流或者綴飾感應勢等結構.此外, 我國上海光機所還提出了基于垂直引線的三環線結構以及阿基米德螺線和TOP 結合等閉合且中心無磁場零點的環形導引方案[38-40].2017 年, 弗吉尼亞大學Horne 等[41]基于微型片上線圈構成的TOP 阱實驗上獲得了BEC環形閉合回路的Sagnac 原子干涉儀, 并于2020 年成功實現對轉動信號的測量, 如圖7 所示.

圖7 弗吉尼亞大學設計的MOT[41]Fig.7.Magnetic trap assembly proposed by University of Virginia[41].

無論何種原子導引, 理想情況下都應具備單模、光滑、無磁場零點、低噪聲和低損耗等特性.單模特性是指物質波只占據基模, 避免物質波耦合到其他橫模上; 光滑是指沒有勢場起伏從而抑制散射和色散; 無零點是為了避免零磁場點導致的原子損失; 噪聲和損耗主要來源于電流噪聲、電場強度起伏、原子自發輻射、Casimir-Polder (C-P)力和范德瓦耳斯力以及表面吸附效應等, 會縮短原子壽命、降低信噪比, 縮短相干長度和相干時間.

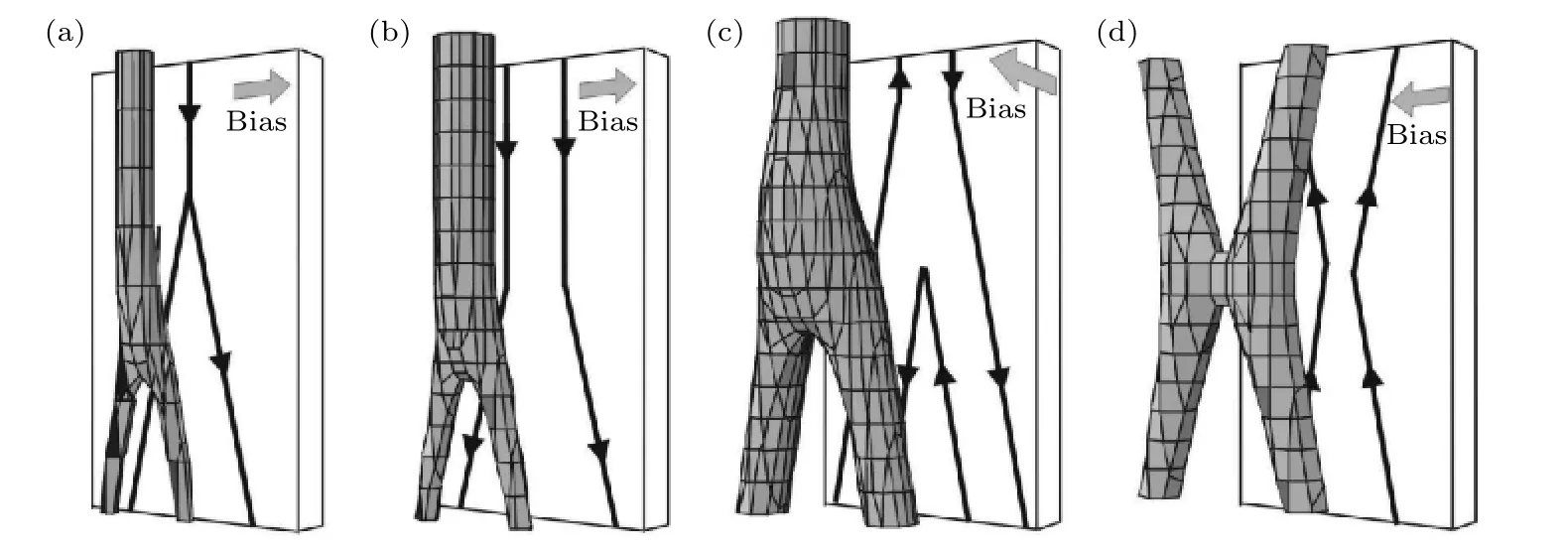

當原子團在導引中傳輸時, 往往還需要對其進行相干分束與合束.最簡單的分束方案是將單勢阱轉變為雙勢阱, 既可在時域中通過動態的改變勢阱形狀來實現, 也可以通過Y 形或X 形導線結構在空間中實現.常見的時域相干分束包括雙線平行分束[18]、五線平行分束[42]以及交叉導線分束等[4,43].基于雙線平行分束Shin 等[44]實現了對BEC 的分束, 該方案結構簡單, 但是對電流漲落和磁場噪聲非常敏感.五線平行分束在實驗上利用穩定的電流驅動裝置以及標準的微加工工藝很容易保證電流漲落變化小于10—4, 對于分束過程中偏置磁場的穩定性要求也大大降低, 目前已經實現了對熱原子團的分束, 并可通過調整外置偏置磁場控制分束后兩個原子團的數目.由于在分束過程中存在明顯的加熱現象, 因此目前還沒有基于此方案實現BEC 分束.交叉導線分束可以實現BEC 沿弱束縛方向(I0方向)的分束, 分束后原子團的距離依賴于垂直于I0方向導線的間距, 目前已有多種交叉導線分束的方案[45,46].此外, Hommelhoff 等[43]提出一種類似交叉導線分束的方案, 他們利用兩個沿I0方向平移的U 形導線來代替交叉導線結構,通過降低I0的強度實現單勢阱到雙勢阱的轉變,最大的勢阱間距約為135 μm, 每個勢阱里裝載500—1500 個原子.

空間中最常見的分束方案主要為X 形和Y 形分束.其中典型的Y 形分束結構如圖8(a)所示,可以按任意比例把原子導引到兩個臂上, 但該方案導引效率不高、原子損失較大[47].改進后的雙線結構Y 形分束器如圖8(b)所示, 其輸入端包括兩根載流導線和一個偏置磁場, 這種結構對磁場和電流漲落非常敏感, 且依然存在原子較強的向后反射的問題.圖8(c)的Y 形導線結構中每個臂中的電流方向相反, 輸入和輸出有完全相同的特性.除Y 形導引外, Cornell 小組用X 形磁波導分束結構獲得了50:50 的分束比, 最大原子數通量達1.5 × 105s—1,其基本原理是利用X 形空心磁管道實現弱場搜尋態的原子導引的磁分束, 如圖8(d)所示[48].

僅利用靜磁阱對冷原子進行相干分束和合束非常困難, 這是因為雙勢阱的間距通常需要在1 μm量級才有好的隧穿和分束保真度, 但是由于芯片襯底噪聲的影響, 目前雙勢阱可以實現的間距與這一水平仍有較大差距.引入射頻場[49]和光場[50]能顯著提高相干分束與合束的性能, 也是目前常見的實驗方式.Zobay 和Garraway[51]在2001 年首次將IP 阱和射頻綴飾勢相結合, 其基本原理是處于靜磁場中的原子會發生塞曼劈裂, 射頻場與劈裂后的能級之間發生強耦合而形成新的綴飾本征態, 此時原子可以被認為處于一個等效的綴飾勢中.射頻綴飾勢對原子團的束縛很強, 原子團可以處于距離芯片表面相對較遠的位置從而避免芯片表面吸附效應和磁場漲落對原子團的影響, 故而可以在較大的導線結構(約500 μm)上實現分束, 如圖9 所示[52].如果采用靜磁場獲得相似的分束效果, 導線尺寸則需要在數微米, 這無疑提高了加工的難度.另外,射頻綴飾勢還可以在實現光滑波導的同時避免磁場零點.

圖8 原子芯片上的Y 形分束和X 形分束[22]Fig.8.Beam splitter for guided atoms using Y-shaped and X-shaped current carrying wires[22].

圖9 原子芯片上基于射頻場的雙勢阱物質波分束[52]Fig.9.Matter-wave beam splitter by dressing RF-fields on chip[52].

基于光場的相干分束可以在保持原子內態不變的情況下只改變原子的外在動量狀態, 最常用的方法是利用激光脈沖駐波對原子云的Raman-Nath衍射或Bragg 衍射實現原子外態分束.為了盡量保證分束后的兩團原子波包的速度和布居數相等實現50∶50 的對稱分束, 可以采用雙頻率Bragg 駐波分束方案或者雙脈沖Raman-Nath 駐波分束[53,54].

3 原子芯片的關鍵實現技術

3.1 原子芯片的設計與制備工藝

如前所述, 通過靜磁場、靜電場、光場等方式均能對原子進行操控.靜磁場原理可以分別采用載流導線、永磁薄膜[55]、軟磁薄膜[56]等方式實現.其中, 永磁薄膜產生的磁場幾乎不產生波動, 引起的自旋反轉躍遷率幾乎為0, 但其磁場強度和結構固定, 很難靈活調整; 軟磁薄膜的磁場穩定且強度可調, 但其磁化容易受外場影響、不易控制; 用微電子工藝可在芯片表面制備出載流導線, 用相對較小的電流即可產生可觀的磁場梯度, 磁場強度和結構形貌可以通過靈活設計載流導線的構型實現, 具有很強的優勢.

載流導線型原子芯片一般通過Z 阱、U 阱等結構實現原子團的轉移, 再輔以用于蒸發冷卻的H 形或W 形導線結構, 根據不同應用目的還需要設計特殊的導引.在設計中需要確定勢阱和導引距芯片表面的高度、磁阱的梯度及導線的載流能力等要素, 結合工藝條件進行迭代修正, 確保芯片具備可實現性.以兩根平行導線為例, 導線間隙與導線間的電阻正相關, 即導線間距越小其電阻越小; 但過小的導線間距會急劇增大剝離或刻蝕工藝的難度, 在制備過程中易產生缺陷導致短路, 故而實際中一般設定導線間隙和導線高度比大于1.

原子芯片的基底和載流導線材質以及適宜的微納工藝技術是決定原子芯片實際性能的重要因素.原子芯片的基底要支撐載流導線、提供導線之間的電絕緣并進行散熱, 因此需要具備良好的熱傳導性和絕緣性, 能承受大的電場, 且在工藝上易于實現高質量、高平整度的材料制備.由于傳統的半導體工藝一般采用硅晶圓, 故而(100)晶向的單晶硅是最常見的芯片基底, 其室溫下的導熱系數為150 W/(m·K), 厚度一般約500 μm, 經過拋光后可獲得光滑的表面.為了確保導線間的良好絕緣,通常會在硅基底上采用等離子體增強化學氣相沉積法(PECVD)或熱氧化法制備一層氧化硅(SiO2),使基片表層電阻率大于1016Ω·cm.雖然PECVD制備效率高, 但生長的SiO2的表面粗糙度會高于熱氧化.由于SiO2的熱導率只有1.5 W/(m·K),所以SiO2通常只生長數百納米[57].AlN, GaAs 等材料也是原子芯片的常用基底.盡管AlN 陶瓷室溫熱導率高達319 W/(m·K), 但它拋光后的表面粗糙度約為40 nm, 不但很難實現高質量大面積制備, 且往往存在微米尺度的缺陷, 對實現小于10μm 的載流導線較為不利.單晶AlN 的表面粗糙度可以到原子級, 但是成本較為昂貴.當在原子芯片上需要構造微MOT 時, 往往還會采用透明原子芯片, 此時常采用對780 nm 激光具有高透過率的碳化硅(SiC)、SiO2或藍寶石(Al2O3)等基底.

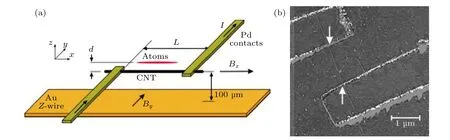

在載流導線制備過程中必須考慮導線的實際載流能力(影響磁阱梯度)、表面平整度(影響激光反射率、電流噪音及勢阱起伏)及與基底的附著力(影響芯片在電流加載后發生熱失配時的可靠性),這些都與導線的材質和制備工藝相關.載流導線一般選用高電導率的Au, Cu 等金屬.Au 結構穩定不易氧化但成本較高且會對Rb 原子產生吸附;Cu 成本相對較低且在硅通孔(TSV)工藝中已較為成熟, 但Cu 相對容易氧化, 如長期暴露在氧環境下則需制備防氧化的介質層, 此舉也有助于防止堿金屬原子污染金屬層降低其反射率, 避免導線之間短路.為了實現緊束縛的單模原子導引往往要提高導線承載的電流密度, 這通常意味著減小導線的線寬或者增大電流(常常需要在10—20 s 的時間內承載幾個安培的電流), 均意味著在材料電導率不變的條件下電流密度增大(>107A/cm2)[36]、熱效應增強, 超出了Cu 導線的耐受范圍[58].載流導線還應具備良好的光滑性和均勻性, 以盡量減少橫向電流導致的磁阱起伏和冷原子團碎片.因此,探尋大電流耐受性強、質量優秀的新導線材料, 對實現高品質的原子導引具有重要的價值.碳納米管(CNT)是一種潛在候選, 具有高達109A/cm2的載流密度(比普通金屬高2—3 個數量級)和超高的熔點[59], 因能實現電子彈道輸運所以可忽略電子散射造成的電流起伏, 有望滿足原子載流導線所需要具備的低噪聲和弱C-P 力等性能.以色列本古里安大學等單位較早開展了基于CNT 的導線型原子芯片研究, 如圖10 所示.他們實驗展示了基于CNT 的雙層原子芯片, 提出了將超冷原子從傳統的磁阱轉移到CNT 阱中的理論方法, 認為基于CNT 的原子芯片表面隧穿、熱噪聲引起的自旋翻轉以及熱效應等勢阱損耗都得到了良好的抑制,論證了CNT 材料是一種非常有前景的原子導引材料[60,61].此外, Cu 的電導率為5.7 × 107S/m, 而CNT 的電導率隨手性變化, 通常在106—107S/m之間, 如果實現CNT 與Cu 復合材料的載流導線,既可獲得接近于Cu 的電導率, 還可以實現比Cu,Au 高近兩個數量級的載流容量(>108A/cm2)[62].本課題組近年來開發了CNT 紡絲陣列與Cu 復合致密材料的制備技術, 單根導線載流能力大于107A/cm2, 并且有望繼續提高一個數量級以上滿足緊束縛導引的需求[63].盡管CNT 材料展示出良好的潛力, 但目前還未真正用于芯片上原子導引的問題在于: CNT 包含單壁和多壁, 既有半導體型又有金屬型和半金屬型, 還有不同的手性, 很難實現CNT材料均勻、可控的制備, 未來實用必須解決CNT沿既定方向高一致性、大面積、高可控制備這一難題.超導材料具有極好的導電性和極低的磁噪聲,且整體工作于低溫條件下使得超導材料附近的噪聲得到了極大抑制, 因此將其用于原子芯片提升原子壽命也得到了廣泛的關注.Hohenester 等[64]分析, 在1 μm 超導導線勢阱中冷原子壽命可達5000 s, 而相同結構的金屬磁阱中的原子壽命則只有不到0.1 s.德國蒂賓根大學Bernon 等[65]實驗上利用超導鈮金屬薄膜產生的微勢阱制備了3.5 ×105個BEC(350 nK), 全自旋極化態壽命大于4 min,基態相干時間可以達到8 s, 證實了超導體原子芯片在提升原子相干時間、實現長壽命激發方面的優勢.

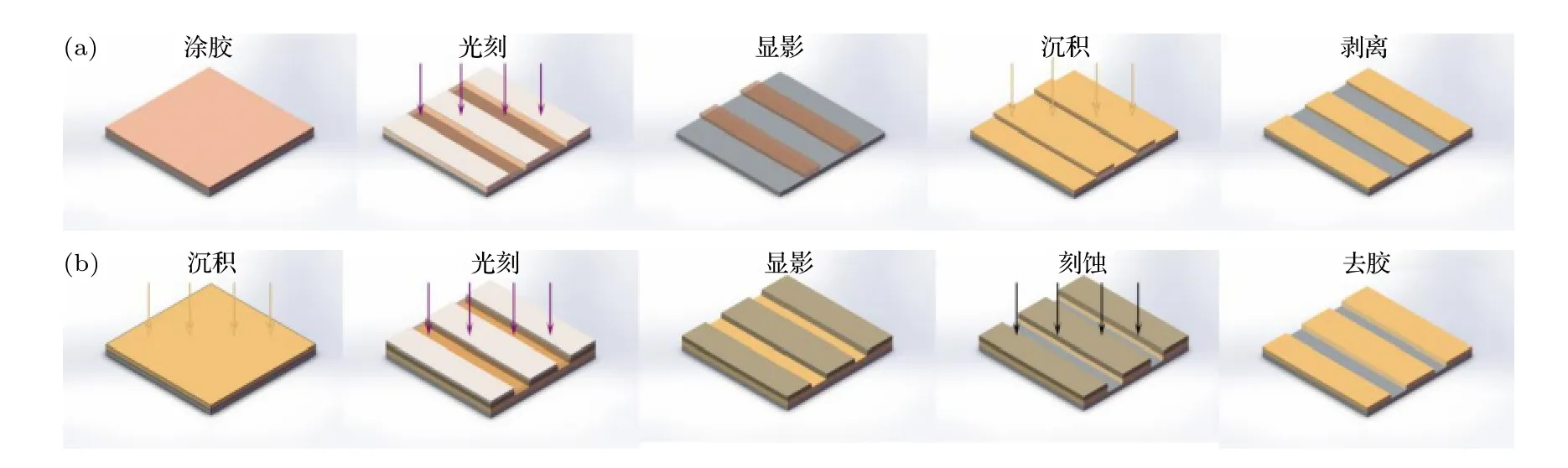

載流導線的成型工藝通常有兩種: 1) 采用厚膠光刻制備圖案, 生長金屬層后剝離; 2) 優先生長金屬層, 再制備掩膜層后進行刻蝕, 主要流程分別如圖11(a),(b)所示.其中, 載流導線可采用磁控濺射、電子束蒸發或電鍍沉積等方式制備.磁控濺射生長的薄膜致密、平整、黏附性強, 但速率緩慢、成本較高; 電子束蒸發的平整度較好, 但金屬層與基片黏附性較差, 與基底存在熱失配時容易脫落; 電鍍沉積雖然能快速生長金屬導線層, 不過內部晶體結構不均勻, 表面粗糙, 容易氧化, 不利于制備表面平整、內部均勻的原子芯片.

圖10 (a) 雙層CNT 原子芯片示意圖; (b) 原子力顯微鏡(AFM)下CNT 及其與Z 形導線的接觸[61]Fig.10.(a) Schematic representation of the two layer CNT atom chip; (b) atomic force microscope image of a CNT fabricated and contacted for use as a Z-shaped wire trap[61].

圖11 原子芯片上載流導線的制備方法 (a) 剝離法; (b) 刻蝕法Fig.11.Fabrication methods of the on-chip current-carrying wires: (a) Stripping method; (b) etching method.

量子信息處理等應用往往需要原子芯片具有復雜的線型, 多層芯片可以避免單層芯片中的導線交叉, 勢阱的設計也具有更大的靈活性.制備多層原子芯片最簡單的方法是將兩個(或多個)單層芯片粘接在一起, 每個芯片工藝完全獨立, 一旦出現問題可以單獨置換某一芯片, 避免整體芯片的重新加工.德國Günther 等[66]在250 μm 厚的基底上利用激光刻出直徑約為400 μm 的過孔并在其中鍍金, 首先實現了兩層原子芯片疊加互連.該方法雖然簡單, 但當芯片之間的距離相對較大或者導線布局較復雜時, 很難實現不同層上微結構的精確對準.后續微納加工工藝不斷發展,涌現出厚膜混合技術、紫外光刻與電子束曝光結合等更適宜制備多層芯片的工藝方法.

原子芯片制備完成后需要與真空腔體進行封裝, 實現其在超高真空環境下的工作.超高真空封裝主要通過如下途徑實現: 1) 傳統的超高真空封裝方式, 即采用真空法蘭通過電極將電流接入原子芯片, 這種方式穩定性較高, 但空間體積占用較大;2) 超高真空膠黏接的封裝方式, 即直接將芯片與玻璃池黏合在一起.由于真空膠的絕緣特性, 芯片電極可以由芯片上表面邊緣引出, 氣密性可達3.3 ×10—11Pa·m3/s, 不過該方式存在有機膠體易老化的缺點; 3) 陽極鍵合的封裝方式, 即通過對玻璃池與芯片施加高電壓與力壓強, 誘發玻璃池與芯片之間成鍵, 實現芯片與玻璃池的封接.該技術封接強度高、重復性好、氣密性高, 特別適用于采用TSV技術制備的原子芯片, 但存在工藝復雜、條件要求嚴格, 生產效率低、可能會出現開裂或自動脫落、不適宜用于較長尺寸玻璃池等問題[67]; 4) 低溫玻璃焊料封接的方式.相較陽極鍵合方式, 此方法工藝簡單、封接強度高、密封效果好.本課題組利用軟鉛焊鍵合的芯片與玻璃池樣品氣密性達8.5 × 10—13Pa·m3/s, 真空規測試的真空度可達2.18 × 10—8Pa, 焊縫厚度可控制在50 μm 以內,連接強度大于20 MPa.圖12(a)—(d)是采用不同封接工藝實現的原子芯片超高真空封裝, 除圖12(c)外均由本課題組與中國科學院上海光學精密機械研究所共同完成[68].

3.2 原子芯片的測試

原子芯片的測試主要包括兩大類.

1) 基礎特性測試: 包括原子芯片的基本形貌與粗糙度、導線的電阻、導線間電阻、導線載流能力、芯片表面反射率等.這些測試可以分別通過電子顯微鏡、AFM、電流電壓源以及角分辨光譜儀等常規設備完成.

圖12 基于不同封裝工藝的原子芯片 (a) 針對傳統真空法蘭電極接口的芯片封裝形式; (b) 超高真空膠; (c) 陽極鍵合[67]; (d) 軟釬焊Fig.12.Atom chips based on different packaging processes:(a)Traditional vacuum package; (b) ultra-high vacuum adhesive; (c) anode adhesive[67]; (d) soft soldering.

2) 磁阱結構測試: 用于驗證接入電流時芯片的表面磁場特性并主要關注兩個參數, 即空間分辨率和磁場靈敏度.目前, 能對空間磁場進行測量的有磁強計、超導量子干涉設備(SQUID)、掃描磁力探針顯微鏡(MFM)、低溫強磁場掃描霍爾顯微鏡(SHPM)和掃描磁阻顯微鏡(SMM)等方法.SQUID 的場靈敏度最高, 噪聲水平可低至幾fT/Hz1/2, 然而其空間分辨率大概在50—100 μm,難以分析十幾微米導線的磁場分布[69]; MFM 可以對空間分辨率在十幾納米的磁場進行測試, 但場靈敏度較低[70], 并且很難對磁場的強度進行定量測量; SHPM基于霍爾效應, 能定量地對空間中的磁場強度進行掃描反映芯片在空間中的磁場分布, 目前最好的空間分辨率可達兩百多納米; SMM 基于磁隧道結技術, 是一種相對簡便、成本較低的方法, 空間分辨率可到25 μm, 噪聲在1 kHz 的時候大概為100 nT/Hz1/2, 且可以在室溫下使用[71].Quantum Design 公司近期將低溫共聚焦顯微鏡和低溫AFM結合, 實現了光探測磁共振成像系統, 可同時達到納米級空間分辨率和3 nT 的磁場測試精度(100 s積分時間), 并已經用于原子芯片的磁場測試中.盡管如此, 最便捷的方法仍然是直接在芯片上加載冷原子進行成像反演, 可以實現納特(nT)精度、幾個微米的空間分辨率, 能夠滿足大多數情況下的測試要求[72].

針對原子芯片上微勢阱中囚禁的原子團的數目、溫度、密度等性質的測試, 可采用熒光成像或吸收成像的方法探測[73].熒光成像法收集角有限,測量的信號較弱, 因此需要設計高信噪比、高放大倍數、低噪聲的電流電壓轉換電路; 吸收成像主要是測試探測光方向上的光功率變化, 具有很高的信噪比, 但對探測光的功率與頻率穩定性同樣有很高的要求.

3.3 原子芯片上冷原子的操控

在原子芯片上加載冷原子進行操控的實驗系統一般包括如下部分.

1) 超高真空系統.用于產生原子氣體并提供冷原子實驗的超高真空環境, 一般可以分為單腔系統與雙腔系統.單腔系統不涉及原子團的轉移, 結構相對雙腔系統簡單; 雙腔系統則是在一個腔體內對原子進行抓取后推送至下一個腔室, 既能俘獲足夠數量的原子又能保持優秀的真空度.

2) 磁場系統.由多個線圈組成, 主要用于屏蔽地磁場并產生二維磁光阱、三維磁光阱、偏置場所需的磁場, 同時也對真空腔中的原子團進行轉移.

3) 光學系統.用于對激光進行移頻、強弱調整、偏振調整后制備冷原子并提供冷原子實驗及成像, 包括3D cooling, 2D cooling, Pushing, Pumping,Imaging, Repumping 等光路, 以及后期的原子分束與合束光路.

4) 時序控制系統與數據采集系統.用于控制各個系統在時間上的協同工作, 如整體控制光路的開啟與關閉、磁場線圈的開啟與關閉、芯片上導線的導通與斷開、相機的數據采集時間等, 最后實現對數據的收集與處理.

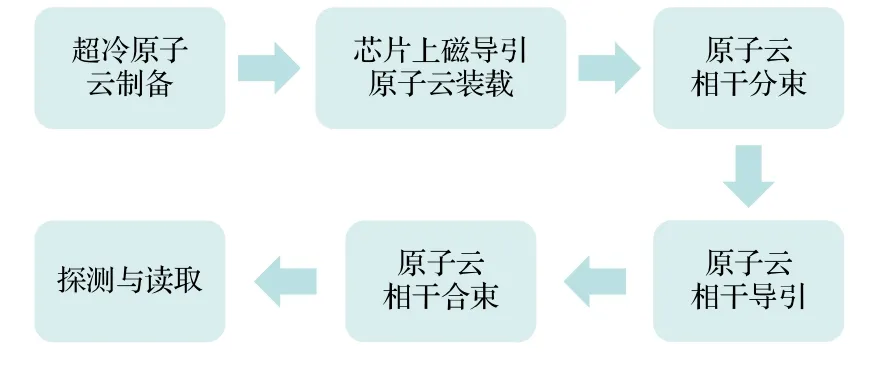

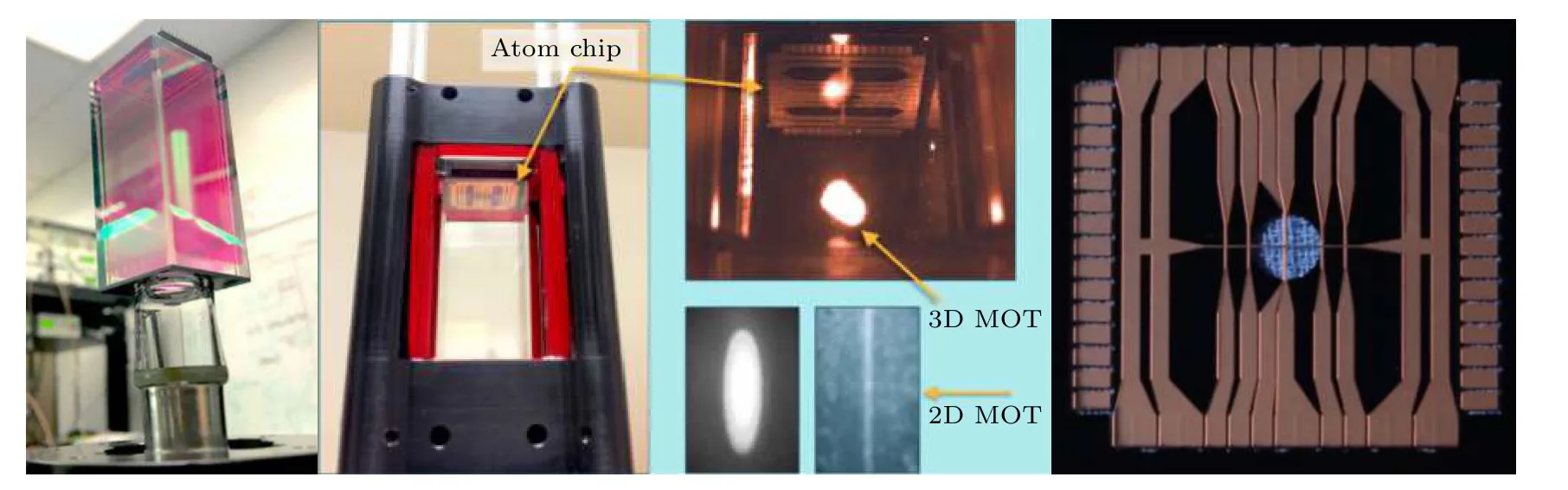

以基于冷原子干涉的原子芯片陀螺儀為例, 其工作流程如圖13 所示.首先是利用激光冷卻制備超冷原子云.通過二維磁光阱、光抽運、三維磁光阱完成原子的初態制備后, 采用轉移線圈將制備的冷原子團向芯片轉移, 并利用mirror-MOT 在芯片上對原子團進行抓取, 逐級完成冷原子向U 阱、Z 阱的轉移, 進一步完成原子的蒸發冷卻后將原子加載到用于實現冷原子干涉的波導中.在波導中完成相干分束、傳播和相干合束, 旋轉信息通過測量相干合束后各動量態上的布居獲得.原子的蒸發冷卻也可以在自由空間中完成后向芯片轉移, 這樣可以降低芯片的復雜度與實驗難度, 但自由空間用于蒸發冷卻的線圈的功耗與體積都較大, 還需要配備水冷, 因此可根據實驗要求選擇具體方案.

圖13 基于冷原子干涉的原子芯片陀螺儀基本流程Fig.13.Basic process of gyroscope based on cold atom interference on chip.

上述過程面臨著一系列挑戰性科學技術難題亟待解決, 比如冷原子的高通量制備應滿足冷原子數量多和制備時間短兩個要求, 而目前國際上BEC 的制備時間最快只有幾個赫茲, 原子數量約為105個, 距離預期仍有較大差距.將冷原子云轉移到原子芯片上還涉及原子裝載的效率問題, 受限于模式匹配問題目前的裝載效率僅有約50%.此外, 冷原子在導引中運動時, 還需要克服原子數損失、熱噪聲、退相干等不利因素.其中, 原子數的損失主要由原子之間的碰撞、勢阱的變化、勢阱的噪聲等因素引發; 原子的加熱主要指冷原子由于芯片的熱噪聲、電流噪音等的激發造成的溫度上升[17];退相干則是存在于所有的量子體系, 也是橫亙于冷原子高性能實驗全過程的關鍵問題, 是反映所制備的原子團狀態和芯片質量的綜合指標, 也是衡量是否能觀測到原子干涉現象的直接因素.原子芯片的典型退相干機制包括[22]: 與冷原子云自身的碰撞散射; 冷原子與原子芯片之間的相互作用; 原子導引自身的不完美; 外界環境或外界操縱激光的耦合等.這些退相干機制大多并非單獨起作用, 往往減弱了其中一種的同時可能會增強其他退相干機制.因此, 原子芯片上退相干的有效抑制是需要不斷深入研究的關鍵問題.

3.4 集成原子芯片

原子芯片自問世起, 科研人員的愿景一直是將其打造為高穩定、高精度、集成化的小型原子研究平臺, 并應用于各類精密傳感與測量等場景.因此, 只有將載流導線等表面微結構與不同材料體系的光子/電子微納器件混合集成, 才可能實現功能強大的集成原子芯片或者原子微系統.2000 年,Folman等[74,75]制作了第一塊集成原子芯片雛形,集成了微MOT、微磁阱和表面磁導線, 實現了中性原子的磁光囚禁、冷卻、裝載與導引.隨后一系列將磁或者光產生的微阱與導引等集成實現磁光混合型或者全光型原子芯片的工作見諸報端.除在同一基底上多種微結構的集成外, 采用wire-bonding或者TSV 等工藝將不同功能層進行芯片間集成的技術也得到了快速發展.如美國Honeywell 和美國國家標準與技術研究院(NIST)實現了將激光器、反射鏡、微真空腔、探測器等混合集成的芯片級原子鐘, 如圖14 所示[76].基于相似的技術途徑他們還實現了芯片級磁力計.

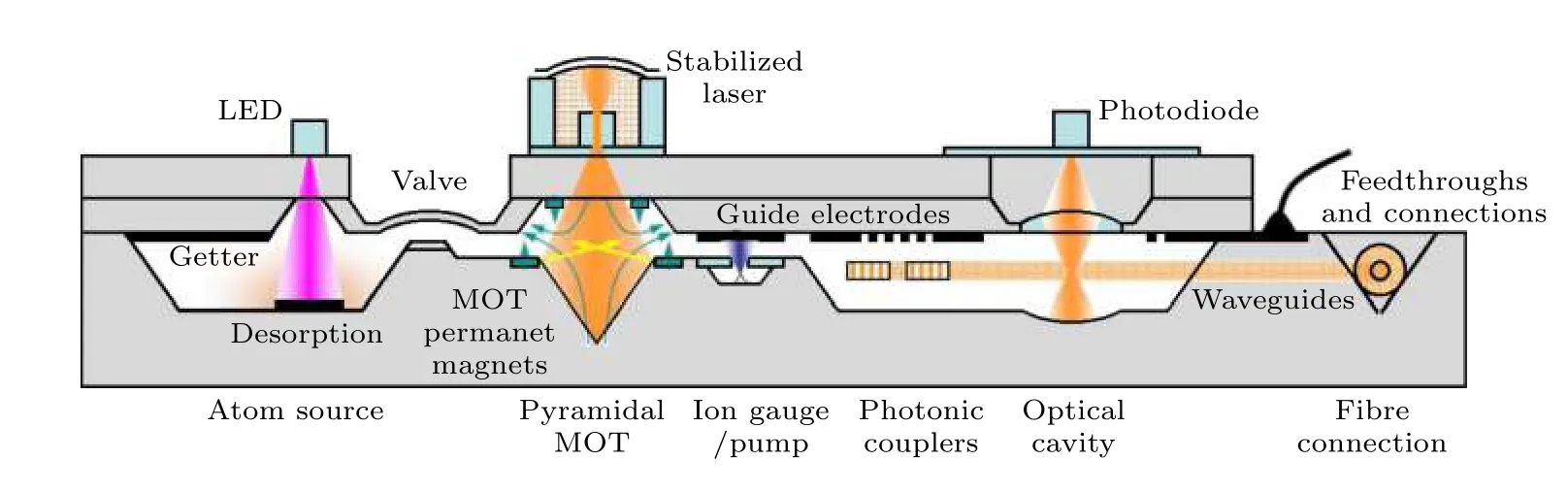

近年, 以色列本古里安大學提出了高度集成化的原子芯片量子陀螺儀構想(理念來源于南安普頓大學Freegarde 團隊), 如圖15 所示.在深刻蝕的基底上集成了微真空系統、微原子源、微真空泵和閥門、單束激光反射式微MOT、微光源、光耦合器、波導和光電探測器等, 具備了傳統大型原子系統的所有功能, 且體積只有20 mm × 24 mm ×5 mm[77].實現這一構想的技術挑戰主要來源于幾方面: 一是光學元件和真空系統的小型化、集成化;二是在同一基底上的異質集成及混合集成; 三是根據不同的應用, 設計具有不同功能、不同技術兼容的集成原子芯片架構.這些問題的解決需要材料、原子物理器件、原子光學等多層次、多學科技術相互促進、共同發展, 才能實現芯片上光子-電子-原子的深度耦合.美國等國家和地區也確實在沿襲此思路推動相關工作, 如NIST 提出了芯片級集成化的冷原子片上實驗室(NIST-on-a-chip), 并正在逐個解決集成原子芯片中的關鍵使能技術, 本文在4.1 節還會對此進行介紹.

4 原子芯片的主要進展

4.1 各國有關原子芯片技術的計劃與項目

由于原子芯片滿足體積(size)、重量(weight)、功耗(power)和成本(cost), 即SWAP-C 的苛刻要求, 在授時、定位、導航等領域展現出獨特優勢,因而近年來各國與冷原子或量子相關的研究計劃幾乎都包含了原子芯片相關技術.

圖14 Honeywell 提出的水平方向集成的芯片級原子鐘方案 (a) 原子物理集成部分; (b) 蒸汽室與光路的集成[76]Fig.14.Horizontally integrated design for a chip-scale atomic clock physics package: (a) Schematic of physics package and (b) photograph of vapor cell integrated into optical path[76].

圖15 高度集成化的原子芯片量子陀螺儀構想[77]Fig.15.Futuristic visions of highly integrated atom chips for quantum gyroscope[77].

美國國防部高級研究計劃局(DARPA)于2001 年啟動芯片級原子鐘(chip-scale atomic chips,CSAC)研究, 開辟了將芯片微加工與冷原子授時相結合的技術途徑.2010 年啟動著名的微型定位導航授時計劃(micro-technology for positioning,navigation, and timing, Micro-PNT), 主要開發自主的芯片級慣性導航和精確制導技術, 對美國發展微型化原子技術起到巨大的推動作用, 時至今日仍在運行.Micro-PNT 包含5 個項目, 最重要的部分為芯片級組合原子導航儀項目(chip-scale combinatorial atomic navigator, C-SCAN), 研究高性能原子慣性傳感器的小型化制造、算法和協同架構,包括核磁共振陀螺儀和原子干涉的Sagnac 效應陀螺儀兩種方案, 最終目標是將原子和固態慣性傳感器集成在一個體積不超過20 cm3、功耗不超過1 W 的微系統中, 轉動精度達到10—4(°)/h, 線性加速度精度達到10—6g, 如圖16 所示[78].

C-SCAN 的指標在實驗室中已得到了驗證, 但其進一步實用需要小型化、集成化的激光器、光學系統和真空系統等協同發展.因此2015 年DARPA-在Micro-PNT 計劃中增加冷原子微系統項目(cold atom microsystems, CAMS), 主要解決低SWAPC 的原子鐘、原子物質波導陀螺儀和加速計所需要的高效窄線寬激光源、高效光學調制器、微型高隔離光學開關、緊湊型低損耗光學隔離器、微電子系統、微型超高真空室和真空泵等關鍵技術.2018 年DARPA 進一步啟動原子-光子集成計劃(atomicphotonic integration, A-PHI), 致力于發展緊湊型光子集成技術逐步代替空間光學系統, 一方面滿足高性能芯片原子干涉陀螺儀和原子鐘的使用需求,另一方面為實現功能齊全、性能優越的便攜化導航授時傳感系統奠定基礎, 如圖17 所示.2020 年底前A-PHI 計劃實現原子囚禁與冷卻的光子集成芯片, 并且與冷原子鐘的架構兼容.

美國NIST 近年來提出了芯片級原子器件項目(chip-scale atomic device program, CSADP),目標是開發芯片級的時鐘、磁力計、干涉儀、陀螺儀等, 實現時間、頻率、距離、質量和力、溫度和壓力、電場和磁場、電流和電壓、流體體積和流量等的精密測量, 最終構筑Nist-on-a-chip, 實現精確的芯片級的量子測量技術[76].美國空軍研究實驗室(AFRL)和美國國家航空航天局(NASA)等機構在最近十余年也對面向傳感的原子芯片技術持續投入, 集合了全美超過50 家知名大學、研究所和公司參與, 具備了非常雄厚的技術積累.

圖16 C-SCAN 的概念圖[78]Fig.16.Schematic scheme of C-SCAN[78].

圖17 美國DARPA 的A-PHI 計劃框架Fig.17.Framework of A-PHI of DARPA.

歐洲對原子芯片技術也非常重視.2014 年法國國家研究署啟動了原子芯片慣性傳感項目(OnACIS), 旨在利用原子芯片實現超高精度的磁導引型原子干涉陀螺儀, 重點解決原子芯片分束結構、原子芯片基底、原子芯片干涉中的退相干問題等.同年英國國防部設置量子羅盤項目(quantum compass),主要研究量子導航和重力成像儀, 核心目標包括將上述系統進行芯片集成與制造.2015 年英國發布的《A roadmap for quantum technologies in the UK》也包含原子芯片的內容, 并認為基于芯片的冷原子傳感在10—15 年內會逐步成熟.近期, 英國量子技術中心(UK Quantum Technology Hub)發布了系列計劃, 將半導體材料、量子器件技術、原子芯片架構與制造技術結合, 研發出用于旋轉傳感和磁力測量的緊湊、低噪聲、超真空兼容的原子芯片.除此, 2016 年歐盟提出量子宣言計劃(Quantum-Manifesto), 計劃利用15 年左右開發可集成在手機等內部的芯片上量子傳感器設備.

我國20 多年前就開始從事原子芯片研究, 近些年在量子技術方面有較大投入, 部分研究計劃涉及了芯片級原子鐘、原子芯片陀螺儀等.自中國科學院上海光學精密機械研究所率先實現芯片上的BEC 后, 中國科學院武漢物理與數學研究所等單位相繼實現了芯片上BEC 的制備和不同結構的中性原子的磁導引等[17,79], 提出了利用倏逝波和表面等離子體勢來囚禁原子的全光原子芯片方案、數字原子芯片方案、激光誘導虛擬磁場阱及陣列方案和原子芯片上冷原子系綜量子邏輯門方案等[80].但相較國外, 我國專項重點支持原子芯片的研究計劃仍然相對較少, 對原子芯片的基礎研究與應用進行體系化的整體布局仍然較為欠缺.

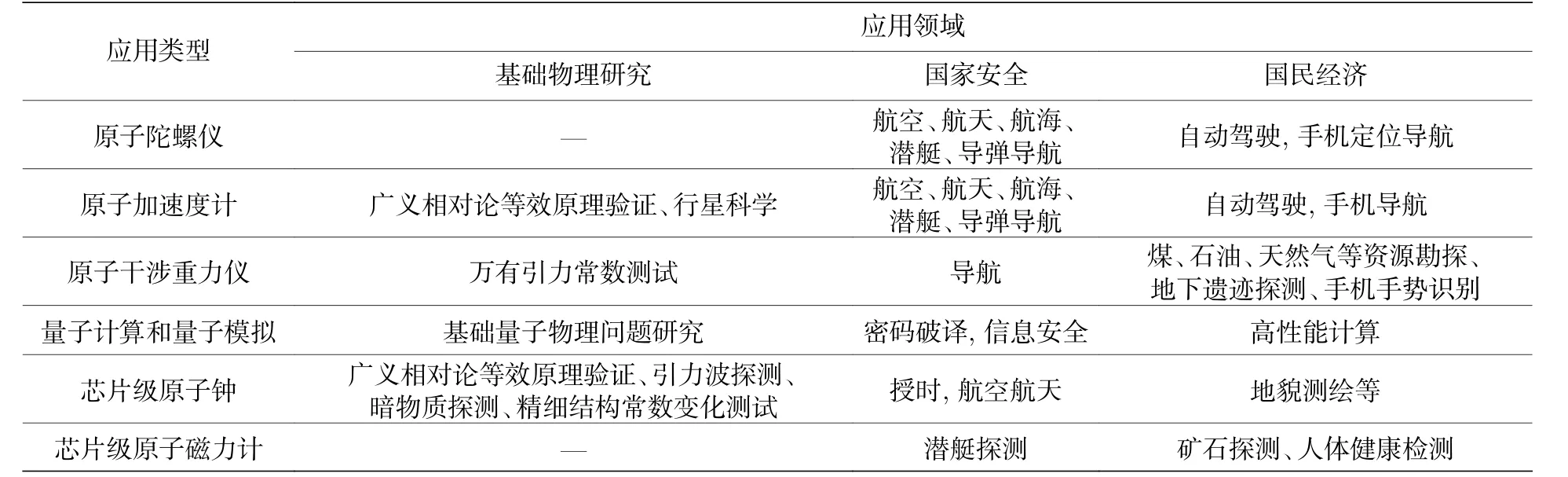

4.2 原子芯片的應用

近年來, 基于原子芯片或芯片級加工與集成技術的冷原子鐘、陀螺儀、加速度計、重力儀、磁力計等精密測量與傳感器獲得了廣泛的關注并逐步走出實驗室, 在高精密授時、慣性導航、重力測繪、腦探測等領域得到應用并且展現了優秀的性能, 如表1 所示.此外, 原子芯片可以提供低維量子氣體、腔量子電動力學、原子-表面相互作用等基礎研究的微納化平臺, 被稱為“微芯片上的量子實驗室”, 在基礎物理研究也有不可忽視的潛力.其中,芯片級原子鐘、芯片級原子磁力計等應用的核心技術是小型化的原子氣室、單模激光器、探測器、光學元器件及其集成技術, 本文不對此做詳細闡述.

1) 冷原子干涉陀螺儀

利用原子德布羅意波干涉效應可以測量萬有引力常數、旋轉角速度、加速度、重力場梯度等, 是量子傳感與精密測量領域的重要手段.特別是基于Sagnac 效應的冷原子干涉陀螺儀具有超高的測量精度(理論精度可達10—12(°)/h)、靈敏度和分辨率, 對于實現不依賴衛星等外部條件定位的全自主慣性導航具有重大意義.相對于國內外已有較多研究報道的自由空間冷原子干涉陀螺儀, 基于原子芯片的導引型冷原子干涉陀螺儀在大大減小體積重量的同時還能縮短冷原子的制備時間, 利用光場或磁場與原子的相互作用力抵消原子重力影響, 在導引過程中原子云不容易發生擴散, 具有魯棒性好、超高精度、可小型化、可集成化、功耗低、重量輕和抗干擾等優點.

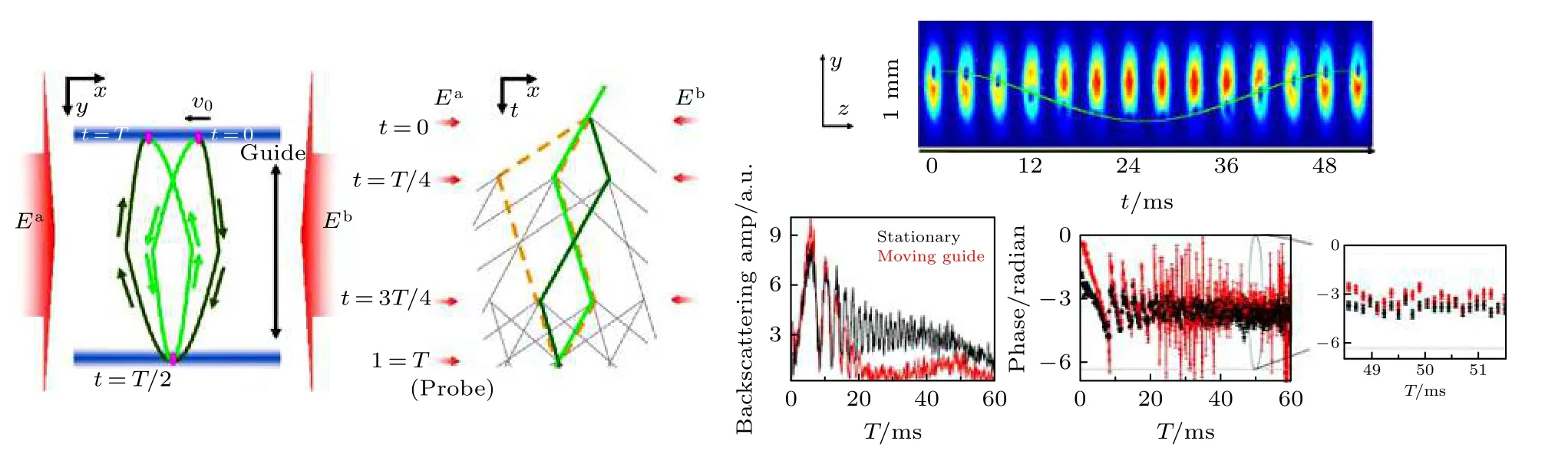

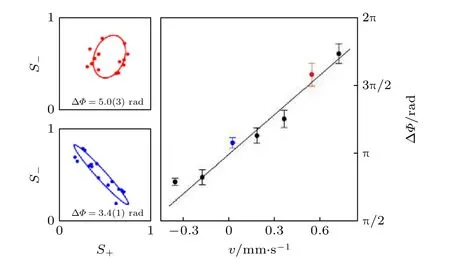

目前國際上有多家科研團隊在開展原子芯片上的冷原子干涉技術, 并致力于將其用于旋轉信息測量中.2005 年, 美國科羅拉多大學Wang 等[54]最早實現了芯片級冷原子邁克耳孫干涉儀, 他們利用波矢沿著磁波導方向的駐波光場實現了芯片上的BEC 分束、反射與合束, 并通過磁場梯度與BEC初始速度在干涉儀兩路之間引入相移差異調節干涉, 在原子傳播10 ms 后仍能觀察到20%的干涉對比度.同年, 美國麻省理工大學Shin 等[44]在原子芯片上通過使勢阱沿緊束縛方向變形成純磁雙阱勢實現了Na 原子BEC 的分束, 從而也觀察到了BEC 干涉.德國海德堡大學Schumm 等[81]結合靜磁阱及射頻誘導的絕熱雙阱勢也在原子芯片上實現了BEC 分束與物質波干涉.2006 年麻省理工大學Jo 等[82]在芯片上射頻誘導的雙阱勢中測量了兩束23Na BEC 的相對相位, 并通過分束過程中的排斥相互作用將相對原子數起伏壓縮到比經典泊松分布小10 倍, 實現了10 倍于相位擴散時間的相位相干時間增強, 進而初步獲得了可用于旋轉角速度測量的等效閉合回路.隨后哈佛大學Wu等[83]利用運動的直線型宏觀磁導引實現了等效“8”字形的閉合回路冷原子干涉儀, 環路面積0.2 mm2.該團隊預計改進后在厘米級的干涉器件上能實現每秒回路面積達1000 mm2, 轉動角速度測量靈敏度達到1 × 10—9rad/(s·Hz1/2), 如圖18所示.2009 年, 美國弗吉尼亞大學Burke 等[84]提出基于線性磁阱波導的二維Sagnac 效應干涉儀,通過移動線性磁阱中心來誘導原子沿一個方向振蕩, 實現了等效面積0.05 mm2的閉合回路, 閉合回路面積可進一步擴展, 但受到初始速率波動、勢阱形貌等因素限制, 未能實現旋轉角速度測試.2012 年華南師范大學Yan 等[85]提出一種利用對稱態依賴的微波電勢的芯片上導引型原子陀螺儀理論方案, 在磁導引的自由傳播方向上對內態不同的原子進行分離和復合, 并隨磁導引的來回移動沿另一個方向平移原子, 有望實現大面積閉合回路的芯片級原子陀螺儀.2013 年, 德國Muntinga 等[86]在微重力環境下, 利用“π/2-π-π/2”型Bragg 激光脈沖作用于原子芯片微磁阱中下落的BEC 上, 實現了原子芯片上的Mach-Zehnder 干涉儀.最新報道他們已經研制了小型化裝置, 估計每1.6 s 可以產生4 × 105束流的BEC, 微重力環境下l Hz 帶寬可產生l × 105的BEC 原子, 改進真空系統后有望將帶寬提升到10 Hz[87].2017 年美國加州大學伯克利分校Wu 等[88]報道了基于金字塔型單激光微MOT(25.4 mm × 25.4 mm × 25.4 mm)的多軸光脈沖原子干涉儀, 利用原子與光相互作用產生的反沖動量實現物質波的相干分束與合束, 實現了對加速度測量精度6 μm/(s2·Hz1/2)、轉動角速度測量靈敏度300 μrad/(s·Hz1/2)、傾角測量精度4 μrad/Hz1/2的綜合指標.2020 年, 美國弗吉尼亞大學Moan 等[89]在TOP 阱中操控分束后的BEC(分束前冷原子數目大概104個, 溫度約為100 nK), 使其在柱對稱環形導引中以相反的方向勻速閉合運動產生Sagnac 干涉, 環路面積約為0.5 mm2.通過使用同步反向旋轉干涉儀有效地抑制共模噪聲, 首次實驗驗證了在環形閉合導引上利用干涉相位的變化對轉動信息的響應, 干涉可見度達到50%, 旋轉測量靈敏度達到8 × 10—5rad/s,接近地球自轉水平, 如圖19 所示.作者認為采用該方案有效閉合面積可以擴展到1 cm2以上, 對轉動角速度的測量精度預計可達10—7rad/(s·Hz1/2)的水平, 有助于推動可實用的芯片導引的原子陀螺儀發展.

表1 基于原子芯片的部分應用Table 1.Applications based on atom chips.

圖18 哈佛大學提出的直線形宏觀磁導引等效“8”字形的閉合回路冷原子干涉陀螺儀[83]Fig.18.Schematic of a moving-guide with a ‘folded figure 8’ configuration for creating an atom gyroscope with multiple-turn interfering paths by Harvard University[83].

圖19 美國弗吉尼亞大學基于芯片上閉合環形原子波導實現BEC 干涉與轉動測量[89]Fig.19.The rotational information experimental results of BEC atomic interferometry based on Sagnac effects by University of Virginia[89].

盡管弗吉尼亞大學實現了環形閉合磁導引BEC 干涉儀及其對轉動的測試是里程碑式的成果,但該實驗采用6 個微環形磁線圈, 其構成的柱對稱環形磁導引勢阱產生的束縛較弱, 原子數目較少,靈敏度不高, 導引中的BEC 原子間的碰撞散射問題一定程度上被弱化.實際應用中對冷原子干涉陀螺儀的靈敏度要求往往非常高, 面臨的環境干擾也較為惡劣, 這就需要將更多原子囚禁到芯片表面的緊束縛勢阱中, 此時大密度冷原子團內原子間相互作用產生的退相干效應是不可忽視的.此外, 除了在環形導引芯片實現穩定的原子干涉與轉動測量本身難度就很大之外, 冷原子干涉陀螺儀往往存在帶寬和動態范圍小的缺點, 還需要通過發展新的原理方案或與其他傳統陀螺儀復合的技術方案解決[90].

2) 冷原子干涉重力儀

原子芯片上冷原子干涉的另一個重要應用是實現重力儀.2016 年德國漢諾威大學的Abend等[91]報道了基于原子芯片的BEC 噴泉式重力儀,如圖20 所示.他們利用原子芯片來進行BEC 態制備并將其作為反射鏡形成脈沖晶格來驅動布洛赫振蕩與雙布喇格衍射從而形成馬赫-曾德干涉儀,最終在芯片表面1 cm3空間內實現了精度達到亞μGal (1 μGal = 10 nm/s2)的重力測量, 為高精度絕對重力測量提供了小型化的技術途徑.2019 年,加州大學伯克利分校的Wu 等[92]利用中心含通孔的金字塔形MOT 將原子冷卻到約2 μK, 使銫原子團沿MOT 中心通孔自由下落到熒光探測區后再被反射從而構成馬赫-曾德干涉儀, 實現了移動式原子干涉重力儀, 靈敏度達到37 μGal/Hz—1/2、長期穩定性2 μGal.他們用這套系統揭示了海洋潮汐載荷效應、記錄了數次遠距離的地震, 并以大約0.04 mGal 的不確定度現場測量了伯克利山的重力以及地下巖石的密度.

3) 量子信息處理、計算與模擬相關應用

圖20 基于原子芯片的噴泉式重力儀[91]Fig.20.Atom-chip fountain gravimeter[91].

原子芯片為原子光學與量子信息處理、量子計算與量子模擬相結合提供了發展契機.2002 年, 德國海德堡大學Schmiedmayer 等[93]報道了基于原子芯片的中性原子量子信息處理方案: 芯片上的交叉導線在偏置場作用下形成靜磁阱, 通過調節電流、磁場相關參數可以控制每個阱中裝載的原子數目, 對這些原子態進行量子編碼就可以實現量子計算, 這是在芯片上實現的第一個量子計算方案.2007 年, 帝國理工學院Trupke 等[94]報道了基于原子芯片和光學微腔集成的單原子量子計算方案,并從理論上指出可以通過測量從光學微腔泄漏的光子來實現原子間的糾纏, 從而實現簡單且兼具高魯棒性的量子計算.2012 年, 普林斯頓大學Houck等[95]對基于芯片級超導回路的量子模擬理論與實驗進行綜述, 并報道了基于超導回路腔量子電動力學陣列的量子模擬方案.阿姆斯特丹大學La 等[96]近期報道了用于量子模擬的FePt 永磁體薄膜蜂巢納米結構磁晶格原子芯片架構, 如圖21 所示, 但他們尚未在芯片上實現原子操控和量子模擬功能.2019 年, 德國聯邦物理技術研究院和漢諾威大學合作報道了基于芯片上多層離子阱的可擴展量子計算和量子模擬方案, 利用激光冷卻在芯片表面35 μm 處實現了對9Be+離子的操控, 如圖22 所示[97].總體上, 當前基于原子芯片的量子計算與量子模擬研究還較為初步, 已有報道的工作主要為理論方案研究, 實驗工作主要集中于作為量子比特的晶格結構設計與制備.

圖21 用于量子模擬的FePt 永磁體納米磁晶格原子芯片[96]Fig.21.The magnetic potential in arbitrary units above an magnetized patterned layer of FePt[96].

圖22 聯邦物理技術研究院和漢諾威大學合作報道的離子阱芯片[97]Fig.22.Multilayer ion trap chip by Germany[97].

4) 其他精密測量應用與基礎研究

冷原子的狀態與原子芯片上導線產生的磁場息息相關, 因此可以利用監測冷原子的狀態來進行高靈敏度的電場和磁場傳感.瑞士的Treutlein 團隊[98]使用原子芯片上的BEC 作為掃描探針, 以微米的分辨率繪制出芯片表面的微波場, 場靈敏度達77 pT/Hz1/2.此外, 里德伯原子具有大極化率、低場電離閾值和大電偶極矩, 對外部電磁場十分敏感, 可以用來測量微波電場強度的微弱變化, 目前利用原子芯片技術已經獲得了優于0.04 V/cm 的測量精度, 但比自由空間的里德伯原子測量微波電場的性能仍然有數個數量級的差距[99].

在加深對量子力學的認知、推動基礎物理研究方面, 冷原子芯片也逐步發揮著重要的作用.2010 年,慕尼黑馬克思-普朗克實驗室第一次在原子芯片上實現多體量子糾纏——自旋壓縮態.這一成果對實現更高精度的芯片級冷原子鐘和冷原子干涉儀提供了重要指導, 也有助于理解多體量子關聯[100].另外, 操控微重力下的超冷原子可以檢驗愛因斯坦等效原理、研究量子力學在宏觀尺度上的有效性以及探究暗能量和暗物質.近日, 加州理工學院噴氣推進實驗室(JPL)和NASA 的研究人員在《Nature》上發表了重要論文, 借助國際空間站的冷原子實驗室(cold atom laboratory), 他們在原子芯片上利用射頻蒸發冷卻實現了BEC, 獲得了20 s 的超長壽命以及230 pK 的原子溫度, 證明了微重力環境對冷原子實驗的優勢, 如圖23 所示[101].除上述進展外, 原子芯片對于研究量子物理中退相干、無序、非線性和低維物理中的原子散射等基礎問題也提供了新的視角和研究手段, 例如原子芯片與最近發展起來的數字微鏡DMD 技術相結合可實現對一維勢阱的有效調控, 為未來一維體系中研究諸如無序導致的Anderson 局域、非晶體系以及其他晶格模型的精確量子模擬提供了新的平臺[102].

圖23 JPL 和NASA 發射到空間站的原子芯片[103,104]Fig.23.Atom chip launch to the space station by JPL and NASA[103,104].

5 總結和展望

5.1 亟待解決的問題

經過不懈的努力, 原子芯片研究取得了長足的進步, 成為原子光學與量子光學的理想研究平臺之一, 但目前仍存在一系列科學技術難題亟待解決.

1) 理論方面: 第一是重點研究原子芯片上的各類原子損耗、熱噪聲及相干性問題, 揭示芯片材質、幾何形貌、原子云特性以及環境因素與相干性的關聯, 闡明冷原子內態、外態相干性在初態制備、裝載、分束、導引、合束等操控過程以及測量中的演變, 豐富原子芯片表面效應以及冷原子中量子少體與多體物理的基本物理認知; 第二是著力拓展針對不同應用目的發展原子芯片操控冷原子的新方法和新理論; 第三是從量子力學的基本測量原理出發, 研究各種探測的理論方案, 為基于原子芯片的量子傳感與精密測量性能提升提供理論依據.

2) 芯片設計與實現技術方面: 一方面需要提出滿足不同需求的緊束縛微勢阱以及單模原子導引的優化設計方案, 能夠在理論上實現高密度BEC 的囚禁與相干操控; 另一方面需要研制高載流能力、高電導率的高質量載流導線, 以及具有高散熱性和高質量絕緣層的基底, 同時還需要開發微米尺度甚至納米尺度的原子芯片新工藝、解決微納尺度結構的精準構造、納米尺度薄膜的高精度制備以及多層芯片間微結構的對準等工藝技術.針對集成原子芯片的發展需求, 還應發展復雜原子芯片的設計方法, 并推動微納尺度窄線寬激光器、微磁/微光/磁光阱、微型化冷原子氣室和探測系統及其他新穎原子光學器件的發展, 探索原子光學器件混合集成或者單片集成技術以及封裝互聯技術[11].

3) 原子芯片實驗方面: 根據加速度計與陀螺儀等實際應用需求, 芯片上冷原子的產生頻率應至少到100 Hz 以上, 因此原子芯片上高通量高效率冷原子制備是與應用緊密相關的重要問題.另外,實驗中常常將自由空間冷卻的原子云轉移裝載到原子芯片上, 此時則需要解決裝載過程中勢阱的尺寸匹配、模式匹配、中心位置重合、形狀和大小匹配等技術難題.在原子操控過程中如何在實際應用環境中保持良好的相干性, 削弱熱噪聲和原子損耗的影響, 同時實現對芯片上的原子及其量子態的高靈敏度、高精度探測也是非常重要的研究課題.

5.2 未來展望

得益于基礎物理與材料、微納加工與集成技術的突破, 盡管原子芯片至今只有20 余年的歷史,但已經獲得巨大的突破: 從操控中性原子到里德伯原子、分子、離子, 從載流導線、永磁體到偶極阱和表面等離激元, 從金屬、硅等材料到磁性材料、超導體、CNT 等, 從外部檢測到片上單原子檢測, 從單層芯片到多層芯片乃至集成芯片, 從單體到多體物理問題, 從表面科學到量子力學基礎研究······原子芯片逐步具備取代大型的傳統裝置的能力, 提供了原子-光子-電子相互作用的片上接口, 在諸多領域得到成功的應用并展示出獨一無二的優勢.未來, 原子芯片有望根據需求定制設計, 集成冷原子源、原子單模相干導引、納米尺度勢阱、移動勢和原子態探測器等模塊, 成為功能強大的原子量子態操控芯片化平臺, 助力量子精密測量、量子傳感、量子信息處理等技術革新性跨越以及量子物理基礎認知的更新.

感謝蘭州大學物理學院安鈞鴻教授和中國科學院物理研究所王如泉研究員提出的寶貴建議, 感謝上海光學精密機械研究所周蜀渝副研究員以及張海潮研究員長期以來的大力幫助!