基于Multisim14仿真設計的多功能數字電子鐘

金子涵 任致遠 史旭東 王勝鐸

摘 要:數字電子鐘是一種利用數字電子技術實現計時的鐘表。本文介紹了在Multisim 14仿真軟件上設計的滿足要求的可調鬧鐘功能數字鐘,對其設計原理、整體框圖和各單元電路做了詳細說明。利用Multisim軟件具有花費少、效率高、周期短,功能強等優勢,可對數字電子鐘電路進行分層設計。將整機框圖拆分成多個單元電路,再將各單元電路連線成整機電路,結構清晰,便于理解每個單元電路功能,使整機電路功能一目了然。

關鍵詞:數字電子鐘;Multisim 14;可調鬧鐘;反饋置數法;分層設計

0 引言

Multisim 14是美國NI公司研發的一款以Windows為操作平臺的EDA工具軟件[1],可以對模擬、數字電路進行仿真與設計,具有豐富仿真分析能力,所以在電子技術領域以Multisim仿真軟件為平臺進行電路設計非常普遍。

數字電子鐘是一種以數字電路技術實現計時的現代計數器,與傳統機械式時鐘相比,具有更高的準確性和直觀性,且無機械裝置,使用壽命更長,因此得到了廣泛使用。從原理上講,數字電子鐘是一種典型數字電路,包括組合邏輯電路和時序電路[2],所以,本文借助Multisim 14軟件仿真數字電路便捷高效的優勢,進行模塊化電路設計,使得設計花費少、效率高、周期短。

1 設計任務

1.1 基本功能

1)應用模擬振蕩電路實現正弦波時鐘信號發生,并作為數字鐘的時鐘信號。

2)實現數字時鐘計時功能,時間以24 min為1個周期。

3)用數碼管顯示分鐘、秒。

1.2 擴展功能

1)具有校時功能,可以對分鐘和秒單獨校時。

2)計時過程具有鬧鐘功能,到達指定時間(時間可選定)蜂鳴。

2 系統結構

數字電子鐘主要由6個單元電路構成。分別為:石英晶體振蕩電路、分頻電路、計時電路、譯碼顯示電路、校時電路、鬧鐘電路。系統框圖如圖1。

系統工作原理:晶振產生穩定的脈沖信號,通過cd4060和74LS74構成的分頻器電路分頻得到1 Hz秒脈沖,作為基準脈沖信號,該信號經過門電路與74HC161構成的計數器電路產生8421BCD碼,再經過譯碼器交由數碼管顯示。秒位累計達到60進位,分鐘滿24進位,以此循環。

如果數字電子鐘顯示的時間與標準時間不一致,可用校時電路進行校準。自選時間的鬧鐘功能由撥碼開關和邏輯門構成的拓展電路來實現。整機電路如圖2所示。

3 單元電路方案設計

3.1 石英晶體振蕩電路

石英晶體振蕩電路如圖3所示。通過石英晶體振蕩器輸出脈沖具有頻率精度高、受溫度影響小、電路結構簡單的優點。選用體積小、抗沖擊性能好的音叉型石英諧振器,其諧振頻率為32.768 kHz,能產生穩定的32.768 kHz的脈沖信號。

3.2 分頻電路

分頻電路如圖4所示。32.768 kHz的脈沖信號通過4060芯片進行11分頻,再接入2個D觸發器,構成直接的4分頻電路,輸出1 Hz的秒脈沖作為秒計數器計時的基準時鐘。

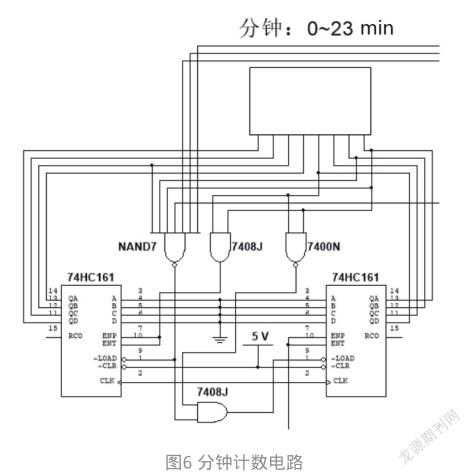

3.3 計數電路

數字電子鐘的秒位采用60進制,選用兩個74HC161計數器級聯并采用反饋置數法實現計數,電路如圖5所示。分頻器送出的秒脈沖經計數器累計,當計數值為59時,同步預置信號有效,下一時鐘同步預置零且向分鐘位送出進位脈沖信號,從而實現60進制。電子鐘的分鐘位是24進制,同樣選用兩個74HC161計數器級聯用反饋置數法計數,電路如圖6所示。秒位送出的進位脈沖信號累計達到“23”,秒數為“59”時,同步預置信號有效,并在下一時鐘同步預置零,并向更高位送出進位脈沖信號。

3.4 顯示譯碼電路

譯碼顯示電路分為譯碼驅動和數碼管顯示。譯碼驅動電路能將計數器輸出的8421BCD碼轉換為數碼管需要的邏輯狀態,并且為數碼管提供足夠的工作電流,保證其正常工作。實時顯示計數值的功能要求通過LED數碼管來實現。

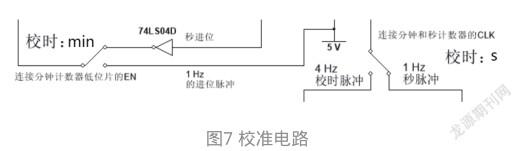

3.5 校時電路

校準電路如圖7所示。當發現時間不準時,可手動選擇脈沖進行校時。選擇4分頻前的秒脈沖校時秒數。如果發現分鐘的數值不準。選擇1 Hz的進位脈沖,不必等秒計60次才進一次位。

3.6 鬧鐘電路

如圖8所示,數字電子鐘可以自選時間做為鬧鈴,顯示分鐘數碼管的各引腳通過撥碼開關連接5 V電源,將撥碼開關撥到選定的分鐘(即對應的引腳為高電平),通過二輸入異或門將分鐘數碼管的高位和低位分別和撥碼開關的對應引腳的電平進行異或運算,各個異或的輸出再接入或門,或門最后通過或非門連到鬧鐘。只有當電子鐘計時到選定的分鐘時,數碼管的高電平與開關撥動情況對應,異或門都傳遞出低電平,或門輸出低電平,再通過二輸入或非門,輸出高電平給蜂鳴器,蜂鳴器工作蜂鳴,持續1 min后停止。

4 整體電路調試

將上述各單元電路組合起來,可以得到數字電子鐘的整體電路。進行多功能數字電子鐘電路的仿真。由實驗結果觀察得到,顯示秒數的數碼管顯示從“00”到“59”計數,并在下一時鐘返回到“00”狀態,連續循環,構成六十進制秒計數器。實驗可觀察得到,顯示分鐘的數碼管顯示從“00”到“23”計數,“23”狀態下一時鐘回到“00”狀態,不斷循環,構成二十四進制分鐘計數器。將撥碼開關撥到選定的分鐘,當時鐘計數到選定分鐘時,鬧鐘響起,下一分鐘自動關閉。仿真結果表明,電路實現了數字電子鐘的計時、校時、鬧鐘功能,完成設計任務。讀者朋友們也可以添加其他模塊來完善數字鐘的功能。

5 硬件調試

在本設計中,為了設計的順利進行,在焊接的時候,我們根據電路的工作原理進行分步調試,保證電路各項功能順利實現。電路調試總圖如圖9所示。

6 結束語

通過Multisim 14仿真軟件設計出各個單元模塊并搭建成一個多功能數字電子鐘電路,調試驗證了設計所要求完成的功能。設計復雜的電子電路時,可借助Multisim 14等仿真工具[4-5],運用分層、分塊設計的思想,使得設計、仿真、測試更為便捷,具有更高的設計效率,進而提高團隊分工協作和解決實際問題的能力。

參考文獻:

[1] 陳建輝.Multisim軟件在《電工學》教學中的應用[J].信息與電腦(理論版),2018(9):99-101.

[2] 李精華.任意進制計數器的仿真設計與制作[J].桂林師范高等專科學校學報,2011(1):149-151.

[3] 陳志貴,郭隱彪.Multisim在數字電子設計中的應用技巧P126[J].機電產品開發與創新,2007(2):148-149.

[4] 張繼,儲開斌,張小芳.基于 Multisim 的電子技術課程設計[J].實驗室科學,2018(1):60-63.

[5] 閻石.數字電子技術基礎[M].6版.北京:高等教育出版社,2016: 271-310.