FPGA在雙通道信號采集與傳輸系統設計中的應用

中國兵器裝備集團自動化研究所有限公司 李坤賀 陳 剛 盧 崢

文章針對高精度、高速信號采集需求,以FPGA為處理核心設計了一款雙通道高速信號采集與傳輸系統,該系統具備雙通道高速AD采樣,經過FPGA處理后,將數據打包通過1路千兆以太網絡上傳給遠程控制終端。該系統具有采樣精度高、適用范圍廣、功耗低等特點。

在寬帶通信、基站及圖像處理領域經常遇到高精度、高速信號采集需求,同時還需要將采集數據進行遠距離上傳,針對該應用需求,本文設計了一款雙通道信號采集與傳輸系統,不僅能夠對2路模擬信號進行高速采集,還能通過千兆以太網接口將采集數據實時傳輸給遠程控制終端。該系統具有采樣精度高、采樣速度快、適用范圍廣、傳輸距離遠等特點。

1 系統方案設計

本文設計的雙通道信號采集與傳輸系統主要包括硬件設備和系統軟件。

硬件設備主要包括:模擬信號調理電路、A/D采集電路、FPGA處理模塊、網絡傳輸模塊;系統軟件主要包括:FPGA邏輯程序和遠程控制終端繪圖顯示軟件。

系統結構框圖如圖1所示。

圖1 系統結構框圖

2 系統硬件設計

本文設計的信號采集與傳輸系統主要由模擬信號調理電路、A/D采集電路、FPGA處理模塊、網絡傳輸模塊等幾部分組成。

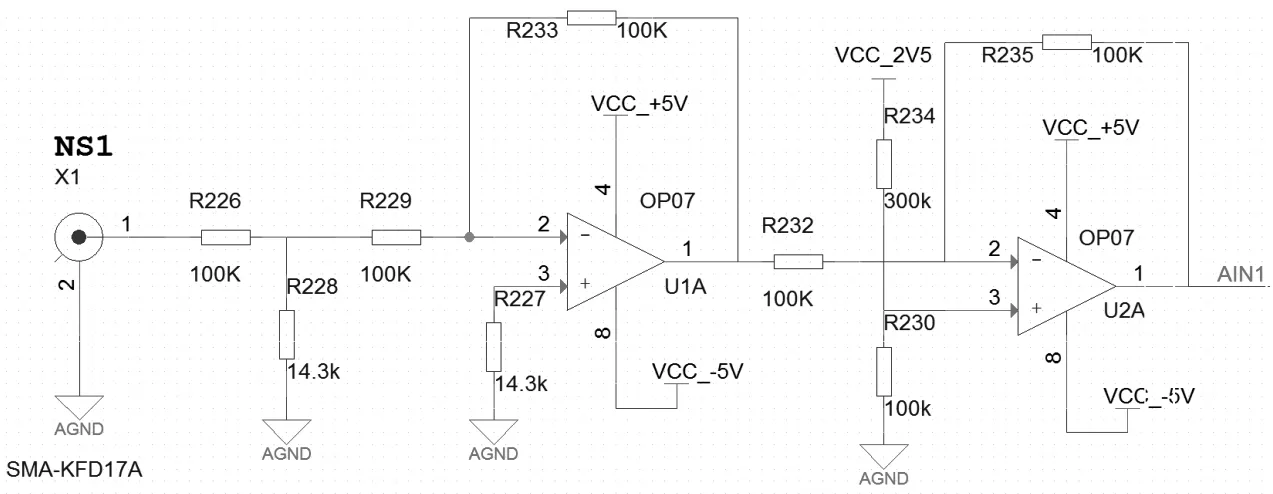

2.1 模擬信號調理電路

為了滿足采集信號的寬范圍輸入,本文設計了模擬信號調理電路(如圖2所示),通過兩級精密運算放大器組成模擬信號調理電路,能夠對不大于±10V的模擬信號進行調理,使其滿足A/D采樣芯片的輸入要求。

圖2 模擬信號調理電路

2.2 A/D采集電路

本文設計中選用2片AD9224作為A/D轉換芯片,該芯片具有最高40MSPS采樣能力,采樣精度12位,可適應2V/4V 輸入電壓范圍,模擬輸入共模電壓為2.5V,只需提供單端+5V模擬電源和+3V/+5V 數字電源。

該芯片數字端接口為12位并行數據接口,本文設計中將該并行接口連接至FPGA,FPGA接收到2路AD9224發送來的采集數據后,進行組幀、打包發送。為了防止數字地層產生的干擾,保證電路較高的采樣精度,在設計中將模擬地(AGND)和數字地(GND)分離開,并且在布線時也避免數字線布于模擬線旁邊或ADC下方。A/D采樣電路如圖3所示。

圖3 A/D采樣電路

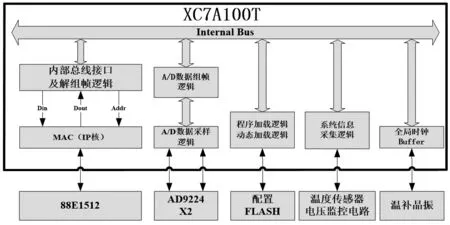

2.3 FPGA處理模塊

本文設計中選用Xilinx公司的XC7A100T作為數據采集及處理核心,該FPGA具有101K邏輯單元、4Mb Block RAM、285只GPIO,邏輯資源和GPIO接口豐富。

FPGA處理模塊程序加載電路:本文設計中選擇256Mb QSPI FLASH作為FPGA的程序存儲器,通過對M[0:2]配置方式引腳的設置,選擇QSPI主動配置模式,配置時鐘最高可為50MHz,程序加載時間約為500ms,保證了FPGA程序的快速加載和啟動。

FPGA處理模塊電源系統:為了保證FPGA能正常工作,選用了Linear的LTM4644作為其電源系統解決方案,該電源模塊具有4路4A DC/DC電源輸出能力,輸入電壓范圍為:4~14V,輸出電壓為0.6~5.5V,輸出電源紋波電壓為:20mVpp,滿足FPGA核電源、接口電源、輔助電源的要求;同時,選用了兩種LDO芯片:CW78D25和CW78D18產生模擬電路所需的更高質量要求的2.5V和1.8V電源。FPGA有嚴格的上電時序,所選電源芯片具有EN、PG引腳,可以通過級聯的方式有效控制電源的上電時序,滿足FPGA對上電時序的要求。

FPGA處理模塊時鐘網絡:為了保證高精度、高速采樣及FPGA內部邏輯的穩定性,選用了高精度、高穩定性的40MHz溫補晶振作為FPGA全局時鐘輸入,40MHz全局時鐘輸入FPGA內部后,經過DCM時鐘、復位邏輯模塊產生內部邏輯使用的100MHz、66.667MHz等時鐘網絡和復位信號;40MHz溫補晶振的頻率溫度穩定度為±1ppm,從時鐘源頭上保證了FPGA內部邏輯采樣的精準度。

FPGA處理模塊內存系統:為了保證高精度、高速采樣數據緩存需要,FPGA處理模塊還設計了1333MHz、32位寬、512MB容量的DDR3內存系統,內存顆粒選用MICRON公司的MT41J128M16JT-125IT。內存顆粒掛載在XC7A100T的HP Bank,能充分發揮DDR3的高速緩存特性。

FPGA處理模塊系統信息采集電路:為了保證系統的穩定工作,設計了溫度傳感器、電源電壓檢測等系統信息采集電路,能夠實現對系統主要電源電壓、溫度信息的監控,并通過網絡接口上報至遠程控制終端。

2.4 網絡傳輸模塊

為了能將采集的數據有效、快速的傳輸給遠程控制終端,本文設計中實現了1路千兆以太網絡接口,由FPGA內部邏輯調用IP Core實現MAC層協議,選用Marvell公司的88E1512作為外接PHY芯片。

FPGA MAC與88E1512之間通過RGMII接口互聯,FPGA通過MDIO、MDC接口實現對88E1512的內部寄存器配置;選用1片25MHz晶體諧振器作為88E1512的外部時鐘源;88E1512所需要的1.0V、1.8V、3.3V電源要求與FPGA各電源系統相同,本文設計中將88E1512所需要各電源系統與FPGA各電源系統共用,既滿足了系統應用,也減少了單獨電源設計,降低功耗和成本。

3 系統軟件實現

本文設計的信號采集與傳輸系統軟件部分主要包括FPGA邏輯程序和遠程控制終端采集繪圖顯示軟件兩部分組成。

3.1 FPGA邏輯程序

FPGA主要實現A/D采集數據的預處理、組幀、發送功能,主要由時鐘及復位邏輯、A/D接口邏輯、網絡接口邏輯、程序加載及動態加載邏輯、系統信息采集及上報邏輯。

時鐘及復位邏輯實現對輸入時鐘和復位信號的處理,并通過DCM模塊產生其他內部邏輯模塊所需要的不同時鐘和復位信號;A/D接口邏輯實現對2片AD9224采集芯片采集數據的預處理功能,組幀后傳給上層組幀邏輯,和系統信息一起上傳給遠程控制終端;系統信息采集邏輯實現對溫度傳感器、電壓監控電路信號的采集處理功能,將溫度、電壓等信息隨A/D采樣數據幀一起上傳給遠程控制終端;網絡接口控制邏輯實現對PHY芯片的配置、MAC IP核的例化和數據的解組幀功能。FPGA邏輯結構框圖如圖4所示。

圖4 FPGA邏輯結構框圖

3.2 遠程控制終端采集繪圖顯示軟件

為了更加形象的觀察采集的結果,本文設計了遠程控制終端采集繪圖軟件,遠程控制終端通過千兆以太網接口接收數據后,首先對數據進行解幀處理,然后將數據分別顯示在采集繪圖顯示軟件上。采集繪圖軟件包括AD采樣波形繪圖界面、系統信息顯示界面。采集繪圖顯示軟件的處理流程如圖5所示。

圖5 遠程控制終端繪圖顯示軟件流程

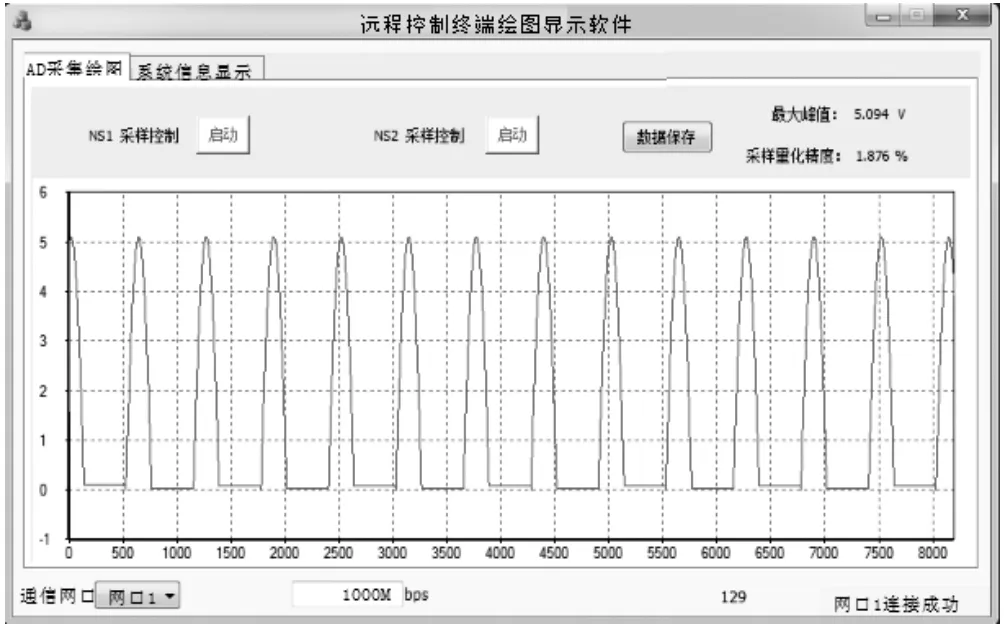

4 功能測試及實現情況

在對本文設計的信號采集與傳輸系統進行測試時,選擇+5V半波正弦信號作為激勵信號源,通過遠程控制終端采集繪圖顯示軟件將采集到的數據進行繪圖顯示(如圖6所示),采樣數據精度誤差不大于2%,系統典型總功耗為3.5W。

圖6 信號采集與傳輸系統采集結果繪圖顯示

結束語:本文詳細介紹了基于FPGA的雙通道信號采集與傳輸系統設計,首先介紹了系統功能結構,然后分模塊介紹了各部分硬件電路設計,其次又介紹了FPGA邏輯和遠程控制終端采集繪圖顯示軟件的設計流程,最后對整個系統進行了信號采集測試,測試結果證明該系統采集指標滿足設計及應用需求。

綜上所述,本文設計的基于FPGA的雙通道信號采集與傳輸系統結構簡單、采樣精度高、采樣速度快、傳輸距離遠、性能穩定可靠,能很好地滿足寬帶通信、基站及圖像處理領域的應用需求。