MCMM技術在SOC FD_Z801模塊中的運用

蔡沅坤,王仁平,孫恒

(福州大學物理與信息工程學院,福建 福州 350108)

1 引言

隨著集成電路產業的不斷發展,特征尺寸不斷縮小,到了深亞微米工藝下,芯片功能受到工藝、電壓、溫度的影響更為嚴重,需要使用更多的工藝角來保證所設計的芯片在不同極端情況下能夠穩定工作。同時,隨著芯片測試需求的增加和芯片功能的增強,芯片工作模式也在不斷增加。設計者除了保證芯片在不同的工藝角下時序收斂,也需要保證在各種工作模式下正常工作。對此,工藝角和芯片工作模式的增加使得芯片在時序收斂方面遭受較大的挑戰。所謂工藝角是指在保證芯片功能正確的前提下所表現出來的參數波動的極端情況[1-2]。在以往設計過程中習慣性采用傳統的方法實現時序收斂,但在這過程中往往需要大量的人工操作進行大工作量的反復迭代并且分析消除模式之間的影響,容易產生時序難以收斂的情況。除此以外,可測試性設計(Design for Test,DFT)技術也可以降低芯片功耗成本和測試成本,在DFT中的掃描鏈技術(Scan Chain)可以在短時間內檢查芯片內部各寄存器的好壞,早一步將因工藝缺陷和塵埃附著的損壞芯片在裸片階段檢測出來,可以防止損壞的芯片流入下一階段的設計中,從而避免造成更大損壞[3]。目前,很多知名電子設計自動化EDA(Electronic Design Automation)公司已相繼發布了系統層面的電路設計軟件,被行業廣泛應用[4]。本文采用了Synopsis公司IC Compiler軟件的MCMM設計技術,以FD_Z801芯片設計為例,對比傳統時序收斂方法,證明了MCMM技術有效實現了時序快速收斂,縮短了設計周期。

2 傳統時序收斂實現方法

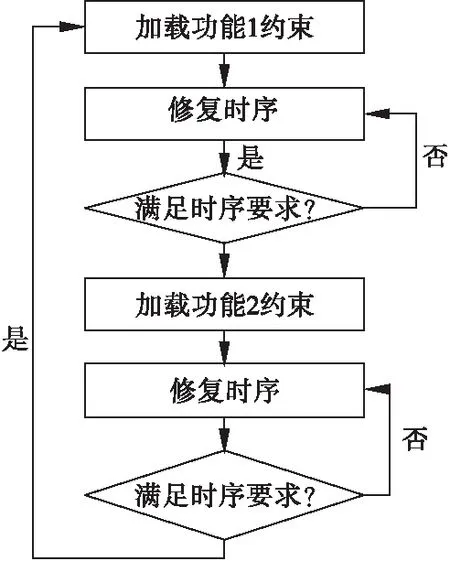

時序分析的目的是檢查時序路徑延時是否符合時序約束要求,根據到達時間(arrival time)、要求時間(required time)和違例值(slack)判斷是否存在時序違約[6]。由于早期工具的限制,早期的時序分析方式是利用一套單元庫,在單一的情況下進行時序分析。在邏輯綜合、自動布局布線過程中選擇最差的工藝角。在最后時序signoff時更換成其他不同的庫,反復分析時序這一流程,如圖1所示。這一情況只能考慮到一種時序情況進行邏輯綜合和布局布線,對此,在設計過程中需要預留足夠的裕量(margin)從而保證在最后時序signoff時能夠在其他工藝角下滿足時序。

對此EDA工具提供對建立時間和保持時間的時序分析分別設定不同的兩套單元庫。使用最差狀況(延遲最大)的庫處理建立時間,使用最佳狀況(延遲最小)的庫處理保持時間,該方法被稱為最佳-最差(best-case worst-case,BC-WC)分析。該方法的工作模式是:建立時間對時鐘頻率以及最長路徑總延時敏感,所以希望數據路徑延遲越小越好,對此采用最大延遲情況去分析,得到的結果是最悲觀的,如果該結果能夠滿足,則其他情況也能同時被滿足;同時保持時間希望數據路徑延遲越大越好,對此采用最小延遲情況去分析,以此覆蓋所有情況[5]。

該方法存在的問題:保持時間希望數據路徑來得越晚越好,但在最佳狀況下的保持時間裕量可能比最差狀況下的保持時間裕量大。這說明使用最佳狀況檢查,保持時間符合時序要求,但在使用最差狀況進行檢查時,保持時間就不符合時序要求,這種情況存在多數復雜的實際情況中。所以傳統的BC-WC方法并不能保證覆蓋靜態時序分析結果的最差狀況[7]。

從圖1流程圖不難看出,該方法存在的問題是EDA工具無法同時覆蓋所有模式下的時序問題,只能通過串行的方式對各個模式下的時序進行修復,同時需要保證修復過程中各個模式之間沒有影響。對此需要設計者反復切換到各個模式檢查時序是否滿足,只要對其中某一個模式進行時序修復操作,其他模式也需要進行檢查。這無疑增加了各個模式之間切換迭代的次數和人工手動ECO(Engineering Change Order)的時間成本。工作量會隨著芯片工藝角和模式增多而增大[8]。

圖1 傳統時序收斂方法

3 MCMM設計流程

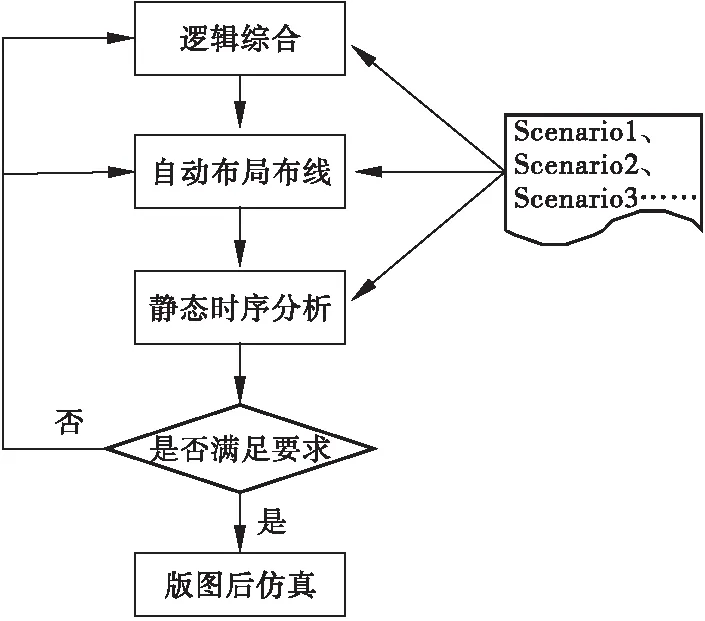

傳統的靜態時序分析,屬于串行的,需要逐個分析,且每種工作模式都要分析。因此,需要耗費大量的時間。為了解決傳統設計流程帶來的不便,MCMM旨在解決這一問題。其內容主要是將工作模式和工藝角相互組合,corner分析由工藝參數(process),電源電壓(voltage)和溫度(temperature)組成,從而創建多個場景(Scenario),接著選擇需要激活的場景讓EDA工具對其進行優化[10]。在這過程中同一條時序違例的路徑會在不同的場景中出現,評估這條時序為例的路徑在不同場景中的時序裕量大小,例如一條路徑在場景1中的裕量為-1,在場景2中的裕量為-0.2,可以認為該路徑在場景1中的權重更高,選擇在場景1中進行修復[9]。流程如圖2所示。

圖2 MCMM設計流程

傳統設計流程可以理解為每次對一個場景進行時序分析和操作,但無法分析其他場景的狀況,同時也無法確定當前要修復的時序路徑是否在其他場景下也有影響。但倘若對所有場景進行分析評估以后便可以確定時序修復的最佳方案,并依照該方案進行時序修復,一方面提高了時序修復的效率,另一方面也保證不對其他場景的時序產生其他影響。

綜上所述,與傳統的時序收斂方法相比,MCMM設計通過在靜態時序分析的過程中將不同的工作模式和工藝角相互組合,創建場景的方式來減少設計迭代,由“串行”變為“并行”,大大節省了人工手動ECO的工作量,提高了工作效率和減少了設計成本[11]。

4 FD_Z801模塊的MCMM技術設計應用

4.1 場景定義

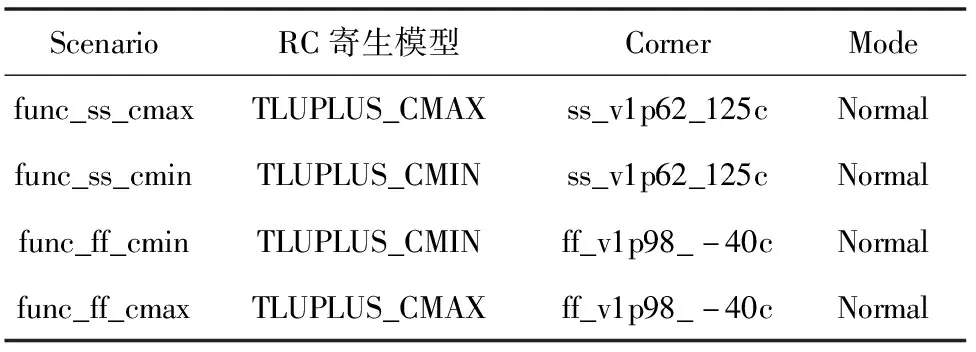

場景就是工藝角和工作模式相互組合[12]。雖然EDA工具能夠對輸入的多個模式進行優化,但工作模式的增加會導致計算機運算時間的增加,所以需要選出有針對性的模式。經過綜合考慮選擇如表1的4個場景。

表1 工藝角和模式的選擇

定義場景的腳本如下:

建立名叫func_ss_cmax的Scenario:

create_scenario func_ss_cmax

讀入該模式的時序約束文件:

source FD_Z801_core.sdc

場景Scenario是由工藝角Corner和工作模式Mode組合而成的,其中Corner分析由工藝參數(process),電源電壓(voltage)和溫度(temperature)組成,下面指定時序分析類型和對應Corner下的lib庫:

set_operating_conditions-analysis_type on_chip_variation-max library scc018ug_uhd_rvt_ss_v1p62_125c_basic-max ss_v1p62_125c

同時設定相應corner的RC寄生模型:

set_tlu_plus_files-max_tluplus $TLUPLUS_CMAX-min_tluplus $TLUPLUS_CMAX-tech2itf_map $TLUPLUS_MAP

同理,根據如上腳本依次建立func_ss_cmax,func_ss_cmin,func_ff_cmin,func_ff_cmax場景。

4.2 實現時序修復和收斂

在完成時鐘樹綜合以后,下一步需要對保持時間進行時序修復。考慮到4個場景都有保持時間違約,需要對其進行修復。對此應當同時激活func_ss_cmax,func_ss_cmin,func_ff_cmin,func_ff_cmax這4個關鍵scenario進行時序收斂,操作腳本具體如下:

激活關鍵的場景Scenario:

set_active_scenarios {func_ss_cmax func_ss_cmin func_ff_cmin func_ff_cmax}

對已經激活的場景Scenario依次設置每個場景的時序裕量:

foreach scenario[all_active_scenarios]{

current_scenario $scenario

set_clock_uncertainty-setup 0.2[all_clocks]

set_clock_uncertainty-hold 0.2[all_clocks]

set_max_transition 0.8[current_design]

set_max_transition-clock_path 0.7[all_clocks]

set_max_fanout 64[current_design]

set_app_var timing_remove_clock_reconvergence_pessimism true

set_scenario_options-setup true-hold true

set_propagated_clock[all_clocks]

set_fix_hold[all_clocks]

remove_ideal_network-all

group_path-name INPUTS-from[all_inputs]

group_path-name OUTPUTS-to[all_outputs]

group_path-name COMBO-from[all_inputs]-to[all_outputs]

}

設置完各類場景的時序裕量后更新clock延遲:

update_clock_latency

開始進行時序修復:

clock_opt-fix_hold_all_clocks

經過一輪時序修復后,再進行增量修復:

psynopt

4.3 時序修復結果

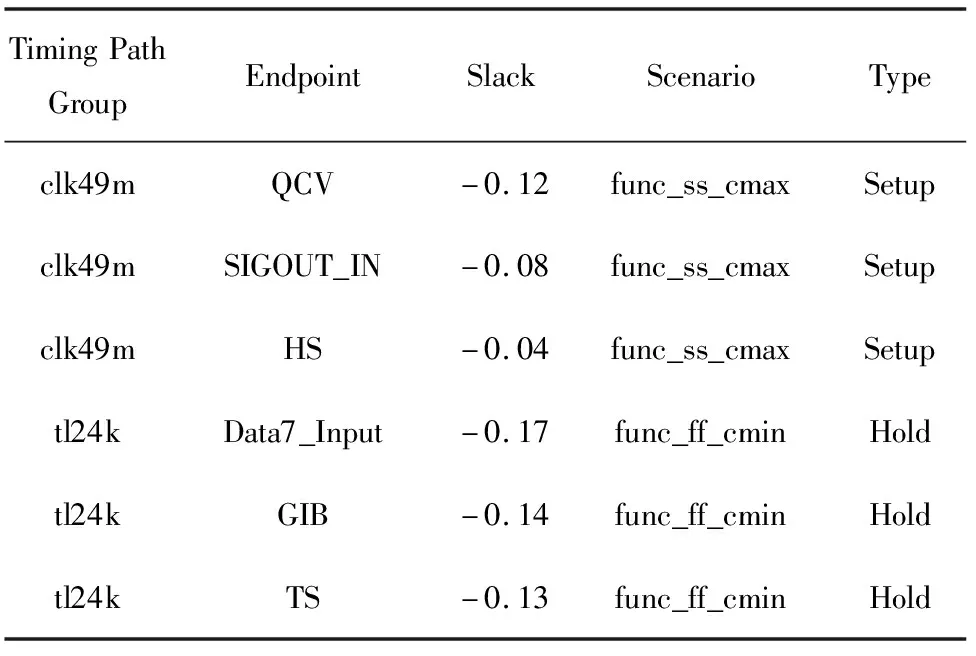

經過上述操作,4個關鍵場景時序路徑完成優化,當前時序違約情況如表2所示。

表2 MCMM第1次優化結果

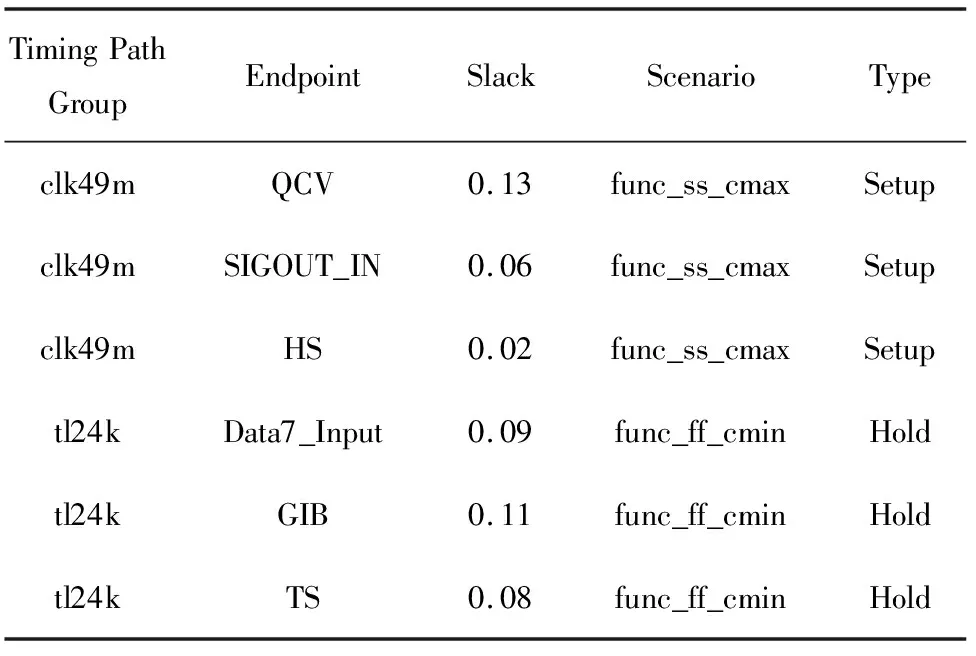

結果顯示,大部分時序已經滿足要求,func_ss_cmax的場景有建立時間上的時序的違例,func_ff_cmin場景有保持時間上的時序違例,只需要激活該場景然后迭代運行一次指令“psynopt”即可修復,結果如表3所示。

表3 MCMM第2次優化結果

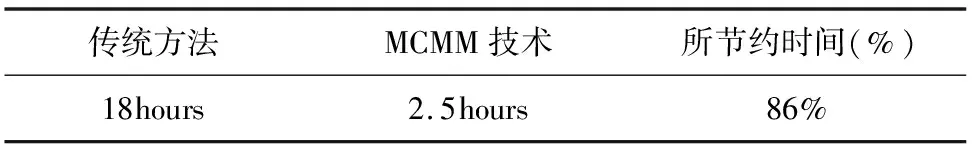

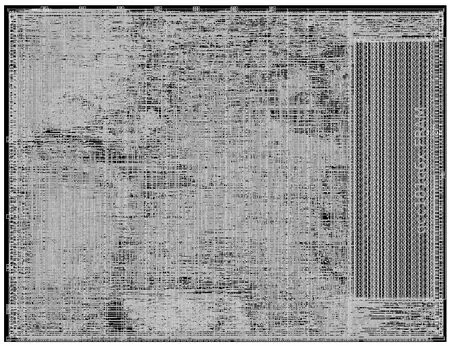

傳統方式修復時序,由于不同模式和工藝角之間數量較多,需要人工來回切換模式,并且模式之間時序相互影響,導致在時序收斂方面所需要的時間多于MCMM技術所需要的時間,在本次設計中嘗試利用傳統方法進行時序收斂。在這一過程中因為工作模式數量多,從而導致在模式間來回切換,切換次數多于20次,由于不同模式之間的時序干擾較為嚴重,所以人工ECO的工作量很大,時序收斂所需要的時間遠遠高于MCMM技術所需要的時間,具體結果如表3所示。對此可以看出MCMM技術在時序收斂方面優勢明顯。MCMM流程完成后的版圖如圖3所示。

表3 傳統方法與MCMM技術所用時間對比

圖3 最終版圖

5 結論

本文介紹了MCMM技術在時序收斂方面的應用,并利用FD_Z801設計實例闡述實現過程,結果表明該技術能夠為版圖設計工程師節省設計時間,其實際應用價值可觀。CTS(Clock Tree Synthesis)階段需要平衡時鐘網絡的負載,減小時鐘偏差,保持時鐘信號的完整性,從而建立一個合理的時鐘網絡[13]。所以本次設計過程中將MCMM技術從CTS階段開始應用,并且達到芯片時序收斂的結果。在今后遇到更為復雜的設計時可以將MCMM技術應用到邏輯綜合階段和布局布線階段,保證芯片能夠一次性滿足在不同工作模式和不同工藝角下的時序要求,同時避免在時序驗證時反復回到布局布線階段進行時序修復,達到縮短設計周期和節約面積的效果,從而節約設計成本。同時現階段已有很多優秀的EDA工具,可以從更多不同的角度研究MCMM優化的設計流程以及方法。對于新的工藝和設計流程還有許多值得深入研究討論的地方。