一種波門信號的設計與實現

貴州航天計量測試技術研究所 貴州 貴陽 550009

引言

波門信號可以產生各種重復頻率和寬度的脈沖信號,而脈沖信號的重復頻率、脈沖寬度、幅度等參數可以在一定范圍內進行調節[1]。

隨著數字處理技術的不斷發展,對波門信號的產生方式也更加多樣化。波門信號在實際中作為典型信號或測試信號而獲得廣泛應用。本文以FPGA數字電路為核心實現一種矩形脈沖信號的研制,用于測試設備中對其他電子設備的校準檢測。

1 方案設計

控制模塊通過總線BUS發送數據,控制多信號模塊控制單元中的FPGA,進而控制多信號模塊中波門信號單元。

多信號模塊控制單元的功能主要是接收控制模塊發送的數字信號,控制相應電路輸出相應特征的波門信號。

總線接收器將控制模塊發送的數據指令中指令及參數并行輸出至數據處理單元,數據處理單元將數據字解釋成RAM1和RAM2的地址總線(AB),在下一個時鐘周期的上升沿,RAM1和RAM2的數據總線將更新為地址總線所對應地址空間中的值[2]。RAM1和RAM2的數據總線的數據之和發生改變將使能總線驅動器輸出控制信號,控制波門電路單元輸出相應波門信號。

2 實現過程

圖1 波門信號產生單元原理框圖

多信號模塊控制單元產生原始波門信號,經RS-422總線驅動器,單端轉差分輸出。單刀雙擲開關實現輸出波門和外部波門輸入的切換,通過光耦隔離輸出內部波門信號,實現對射頻信號的控制。其原理如圖1所示。

多信號模塊控制單元核心為FPGA,其參考時鐘為50MHz,即每個時鐘信號的周期為0.02us,所以,只需編程進行分頻/計數,使得FPGA的I/O口在1.00ms/0.02us=50000個時鐘周期內保持高電平,在(90.00-1.00)ms/0.02us=4450000個時鐘周期內保持低電平,重復操作即可得到所需要周期和占空比的波門信號。

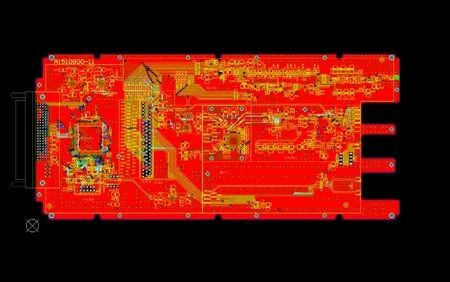

依據波門信號方案設計,波門信號印制板設計為8層板,板材為FR4。PCB如圖2所示。

圖2 波門信號電路PCB圖

3 信號測試

波門信號頻率誤差、電壓精度測試用儀器為Lecroy公司的數字示波器,型號為wavepro 7200A。

表1 波門信號周期精度、脈沖寬度精度、單極電壓精度數據表

從數據記錄表表1中可知,信號輸出范圍滿足設計指標要求。

4 結束語

本文主要介紹波門信號的設計及實現,通過對波門信號進行測試,結果表明,設計的波門信號的實測數據滿足設計指標要求。該電路的實現方式可廣泛應用于類似產品的設計,具有很好的應用價值。