卷積神經網絡RLeNet加速器設計

康磊 李慧 鄭豪威 李鑫

摘要:針對卷積神經網絡(CNN)對運算的需求,現場可編程邏輯門陣列(FPGA)可以充分挖掘CNN內部并行計算的特性,提高運算速度。因此,本文基于FPGA開發平臺,從模型優化、參數優化,硬件加速以及手寫體數字識別四個方面對CNN的FPGA加速及應用進行研究。提出一種數字識別網絡RLeNet,并對網絡進行參數優化,卷積運算加速采用脈沖陣列與加法樹結合的硬件結構實現,同時使用并行技術和流水線技術優化加速,并使用microblaze IP通過中斷控制CNN加速器IP接收串口發送的圖片數據進行預測,輸出結果。最后在Xilinx Nexys 4 DDR:Artix-7開發板上實現了MNIST數據集手寫體數字識別預測過程,當系統時鐘為200MHz時,預測一張圖片的時間為36.47us。

關鍵詞:CNN;FPGA;RLeNet;MNIST;手寫體數字識別

中圖分類號:TP389.1? ? ?文獻標識碼: A

文章編號:1009-3044(2021)06-0016-04

Abstract: In response to the requirement of convolutional neural network (CNN) for multiplication and accu-mulation operations, Field Programmable Logic Gate Array (FPGA) can fully tap the characteristics of parallel computing within CNN and increase the speed of operation. Therefore, based on the FPGA development platform, this article studies the FPGA acceleration and application of CNN from four aspects: model optimization, parameter optimization, hardware acceleration, and handwritten digit recognition. Propose a digital recognition network RLeNet, and optimize the parameters of the network. Convolution operation acceleration use a hardware structure combining pulse array and addition tree,parallel technology,pipeline technology, and microblaze IP is used to control the CNN accelerator through interrupts. The IP receives the picture data sent by the serial port for prediction and outputs the result. Finally, on the Xilinx Nexys 4 DDR: Artix-7 development board, the MNIST data set handwritten digit recognition and prediction process is implemented. When the system clock is 200MHz, the time to predict a picture is 36.47us.

Key words: CNN; FPGA; RLeNet; MNIST; handwritten digit recognition

1 引言

CNN作為一種典型的深度學習神經網絡結構,受到自然視覺認知機制啟發而來[1],在視頻處理、人臉識別、語音識別和自然語言處理等很多方面都表現得非常出色[2-3]。但CNN需要大量的計算,在這樣的背景下,FPGA 似乎是一種非常理想的選擇,同GPU相比,FPGA 不僅擁有數據并行的特點,還擁有流水線并行的特點[4]。目前很多研究者對FPGA加速進行了研究,例如Yu-Hsin Chen提出的Eyeriss高效可配置卷積神經網絡[5],中科院Temam教授和陳教授合作的機器學習加速器DianNao[6],以及google的TPU[7]等。本文在已有加速器的基礎上,進行了數據優化、加入流水線技術實現卷積神經網絡的加速,并使用開發板自帶microblaze通過中斷控制CNN加速IP輸出預測結果。

2 系統總體介紹

2.1 RLeNet模型結構

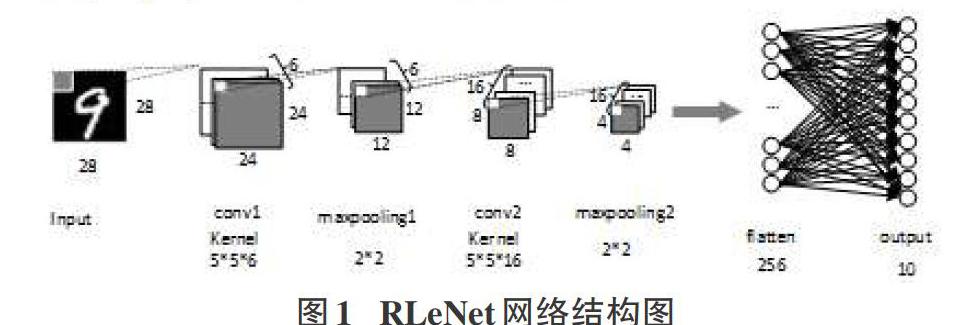

RLeNet模型是在LeNet-5[8]模型的基礎上進行改進得到的,LeNet-5模型共8層,包括卷積層1(C1),池化層1(P1),卷積層2(C2),池化層2(P2),平壓層(F1),全連接層1(D1),全連接層2(D2),輸出層(Output)。本文對模型進行如下改進:將LeNet-5的D1層,D2層刪除,只保留Output輸出層,改進后的模型命名為RLeNet(Reduced LeNet-5),改進后的模型共有6層,包括卷積層1(C1),池化層1(P1),卷積層2(C2),池化層2(P2),平壓層(F1),輸出層(Output)。RLeNet的模型結構如圖1所示。

表1為LeNet-5、RLeNet模型各層參數量對比。其中,LeNet-5的D1層、D2層共有41004個float32數據,約占總數據44426個float32(177.8KB)的92.3%。改進后的模型RLeNet共有5142個float32數據(20.6KB),模型參數數據量由原來的177.8KB降低到20.6KB。模型使用Keras框架 [9],模型訓練完成后,準確率為98.5%,和LeNet-5的精確度98.7%相比,模型精確度幾乎沒有降低,但是模型參數數據量減少為原來的11.6%。

2.2 系統硬件結構

CNN加速器IP的硬件結構如圖2所示。整個系統由CPU,中斷,CNN加速器IP和UART串口模塊組成。系統工作流程為:CPU通過按鍵中斷接收CNN加速器IP使信號,當CPU接收到該使能信號后,等待串口發送的圖片數據,然后將接收到的圖片數據送入Block_ram,CNN加速器IP從Block_ram中讀取圖片,進行卷積運算。運算完成后,將運算結果返回給CPU,CPU將結果通過LED燈顯示。其中,CNN加速器IP完成圖片的預測,它主要包括卷積模塊,池化模塊,全連接模塊,輸入輸出模塊。CNN加速器IP工作流程是:首先由控制器發出控制信號,從數據寄存器讀取輸入和權重數據分別放入移位寄存器和權重Buffer,將數據和權重分別從移位寄存器和權重Buffer讀出,送入乘加模塊進行卷積運算。卷積運算完成之后,將卷積結果送入池化層進行池化運算,池化運算的結果送入特征圖Buffer,兩次卷積池化后,將數據進行平壓,最后進行全連接運算,輸出圖片的預測結果。

3 數據輸入

3.1 數據類型轉換

相比于浮點運算,FPGA在做定點運算會消耗更少的資源,同時有更高的性能[10]。因此,本文將RLeNet模型參數將float32的模型參數左移13位并保存為int16類型參數,存入.coe格式文件中。輸入數據為28*28的灰度圖片,將輸入數據轉為uint8并保存為.txt格式文件。

3.2 串口數據輸入

數據輸入分為兩部分,圖片數據輸入和權重數據輸入。權重數據輸入直接存入片上的block_ram中,圖片數據通過uart_ctrl模塊控制串口將上位機發送的數據存儲到片上的block_ram中。圖片數據發送主要包括uart和uart_ctrl以及數據存儲三個模塊。圖片數據發送模塊結構如圖3所示:

3.3 數據處理

圖片數據通過串口發送到block_ram中后,CNN IP將數據從block_ram中讀入shift_ram,將串行輸入轉為并行輸出,獲取卷積運算的輸入滑窗。

卷積運算的輸入滑窗大小和卷積核大小相同,滑動順序是:從圖像左上角開始,從左到右每次滑動一個單元,在滑窗到達輸入的最右端時,滑窗從上到下滑動一個單元,再次從最左端開始,每次向右滑動一個單元,最后滑動窗后到達圖像右下角結束[11]。圖4為本文卷積運算的輸入,其中灰色部分是第一個5*5輸入滑窗。黑色箭頭表示滑窗滑動順序。

為了硬件實現卷積運算的滑動窗口,本文使用shift_ram生成卷積滑窗像素矩陣。將存放圖片數據的block_ram和4個28*9bit的Shift_ram (Shift_ram1、Shift_ram2、Shift_ram3、Shift_ram4)以圖5方式連接。從block_ram中讀圖片數據進入Shift_ram,裝滿后,輸出Out_0,Out_1,Out_2,Out_3,Out_4的值為1、29、57、85、113和圖5中灰色卷積滑窗的第一列數據相同(粗黑框圈出),然后將這五個數據存儲到5*5寄存器中的最右邊一列。

下個CLK,Shift_ram4移除數據1,數據逐個移動后,得到圖6中的Out1_0,Out1_1,Out1_2,Out1_3,Out1_4的值為2、30、58、86、114和圖5中灰色卷積滑窗的第二列數據相同(虛線框圈出)。將上一個CLK獲取的存在5*5寄存器中的五個輸出左移,再將當前CLK五個輸出存儲到5*5寄存器中的最右邊一列。五個時鐘周期后,得到5*5的卷積輸入窗口。之后每個CLK,移除5*5寄存器最左邊一列數據,獲得下一個卷積輸入滑窗。

這樣獲取輸入滑窗會產生無用的滑窗,在移除數據為25至30時,五個ClK內讀取的分別是序號為26,27,28,29,30為首地址的列,但在實際卷積過程中,滑窗右端到達序號為28的列時,滑窗會向下移動,直接讀取以29,30,31,32,33為首的列。在卷積完成后,需要將這些無用數據刪除。

4 卷積模塊實現

4.1 單個乘單元(Mul)硬件實現

卷積運算的單個乘法模塊Mul如圖7所示,將輸入數據Input_x和權重Weight進行乘運算,運算結果Output_y保存在寄存器中,同時,輸入數據Intput_x向下傳輸。

4.2 卷積運算(Conv)硬件實現

本文卷積運算模塊如圖8所示,首先將Weight數據放入Mul單元,然后將5*5的輸入數據Input_x送入25個并行Mul單元,下一個CLK,將運算結果送入加法樹,一個CLK后輸出加法器運算結果。加法樹共分為五級,第1級共有13個加法器,將25個乘法器結果和一個bias分別送入13個加法器。第2級將第1級計算結果送入6個加法器(余下1個后面算),以此類推,第5級將第4級結果送入加法器,得到最后的結果。

4.3 乘加模塊并行運算設計

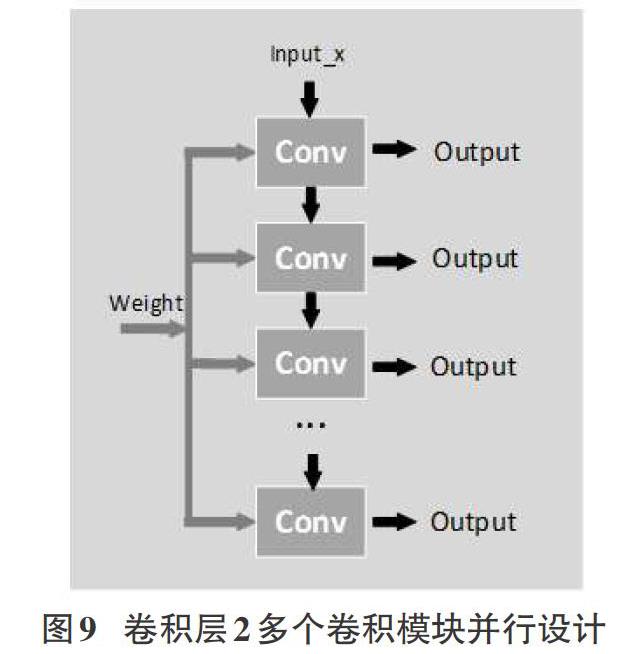

本文乘加模塊并行運算設計是同一個輸入滑窗和多個卷積核進行并行計算,輸出多個卷積運算結果。本文卷積層2將12*12輸入和16個卷積核同時進行并行運算,輸出運算結果,卷積模塊并行設計硬件結構如圖9所示。

5 池化模塊設計

5.1 池化模塊輸入

卷積運算完成后,將其運算結果保存到存儲器中。由于卷積運算的卷積核有多個channel,需要將卷積運算多個channel的結果進行累加求和,作為池化模塊的輸入。

5.2 池化運算硬件實現

在得到池化運算輸入后,進行池化運算。本文采用步長為2的最大池化。在2*2的滑窗內獲取最大值。首先,通過地址獲取池化窗口的輸入,以池化1為例,卷積運算可以獲得24*28的卷積結果并存儲在寄存器中。那么第一次池化運算的輸入的窗口為地址0,地址1(0+1),地址28(0+28),地址29(0+29)中的數據。第二次卷積運算輸入滑窗數據為存儲器中數據地址2,地址3(2+1),地址30(2+28),地址31(2+29)中的數據。另外,由于卷積運算輸出為24*28,實際卷積層1的輸出應為24*24,在池化運算時,無用數據不需要進行池化運算,在輸入行地址大于24時,行地址等于0,列地址加56(向下移兩列)。

在獲取輸入滑窗后,通過三次兩兩比較得到2*2滑窗內的最大值。如圖10所示,首先比較din_x和din_y,得到max1和max2,之后比較max1和max2大小,輸出較大數max。之后,滑窗向右移動兩個單元,獲取下個滑窗中的最大值。

池化運算并行接收多個卷積運算的結果,將結果累加,之后并行進行池化運算。

6 全連接模塊設計

全連接模塊的實現采用乘加運算,全連接模塊輸入為平壓層的輸出,輸出為10個數字的預測結果。全連接模塊的運算是輸入和權重進行乘累加運算,獲取一個數字預測結果的輸出,循環十次之后,輸出十個手寫體數字的預測結果。硬件設計將輸入數據和權重數據放入乘法器,獲取乘運算結果,然后和之前的結果進行累加,獲取數字預測結果。

7 實驗結果

本設計是在Vivado ISE下使用Verilog HDL進行開發,使用Xilinx公司的Nexys 4 DDR : Artix-7開發板進行測試,主頻為0.2GHz。CPU環境為CORE i7 10th四核處理器,主頻為3.9GHz。 GPU型號為Tesla P 100,主頻為1.4GHz。本文采用MNIST數據集手寫體數字為輸入數據,數據為28*28的單通道灰度圖片。

本文將浮點輸入和權重改為9位定點后,模型用1000張圖片進行測試,檢驗模型準確度,最終測試結果,共有5張數據預測不正確,準確率達到99.5%。在200MHz的CLK下,一張圖片在卷積層1做浮點運算的時間為9.1us做定點運算的時間為1.58us,速度提高了約6倍。

表2為不同平臺下,CNN運行的時間及能耗對比[12]。CPU運算時間是在python環境下執行模型預測函數,得到預測12000張圖片的時間,再算出預測一張圖片時間,同理得GPU平臺圖片預測時間。FPGA平臺上的運算時間是采用CNN加速器IP運算得到的預測時間,由表2可知,在CPU平臺上,卷積網絡運行時間約為在FPGA平臺運行時間的2倍。而在GPU平臺上,卷積網絡的功耗比在FPGA平臺多4倍。

CNN IP加速后,片上寄存器使用了20974個,LUT as logic使用了53123個,LUT as memory使用了2742個,block_ram使用了48.5個。系統資源消耗較高。

8 結語

研究了手寫體數字識別的CNN的FPGA實現,提出了一種基于數據優化及多級并行流水結構的CNN加速器,并將其作為外設,將數據。通過資源復用、并行計算和流水線技術,來對卷積運算進行加速。最后實驗結果表明,系統的運算速度以及資源利用率得到提高,系統預測一張圖片約為36us,其計算速度是CPU的2倍,而系統的能耗是GPU的1/4。但系統的LUTs資源占用較多,可以通過其他優化方式降低系統資源占用率。

參考文獻:

[1] Gu, J., Wang, Z., Kuen, J., Ma, L., Shahroudy, A., Shuai, B., Liu, T., Wang, X., Wang, L., Wang, G. and Cai, J., [J].2015. Re-cent advances in convolutional neural networks. arXiv preprint arXiv:1512.07108.

[2] Chen Y H , Emer J , Sze V . Eyeriss: A Spatial Architecture for Energy-Efficient Dataflow for Convolutional Neural Networks[C]// International Symposium on Computer Architecture (ISCA). IEEE Computer Society, 2016..

[3] Chen T , Du Z , Sun N , et al. DianNao: a small-footprint high-throughput accelerator for ubiquitous ma-chine-learning[C]// International Conference on Architectural Support for Programming Languages & Operating Systems. ACM, 2014.

[4] MONREALE A, PINELLI F, TRASARTI R, et al. WhereN-ext: a location predictor on trajectory pattern min-ing[C]//Proceedings of the 15th ACM SIGKDD International Conference on Knowledge Discovery and Data Mining, Paris, Jun 28-Jul 1, 2009. New York: ACM, 2009: 637-646.

[5] Kumar S , Bitorff V , Chen D , et al. Scale MLPerf-0.6 models on Google TPU-v3 Pods[J]. 2019.

[6] 蹇強,張培勇,王雪潔.一種可配置的CNN協加速器的FPGA實現方法[J].電子學報,2019,47(7):1525-1531.

[7] Han X , Zhou D , Wang S , et al. CNN-MERP: An FPGA-based memory-efficient reconfigurable processor for forward and backward propagation of convolutional neural networks[C]// 2016 IEEE 34th International Conference on Computer Design (ICCD). IEEE, 2016.

[8] Zhang C, Li P, Sun G, et al. Optimizing fpga-based accelerator design for deep convolutional neural networks[C] Proceedings of the 2015 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays. ACM, 2015: 161-170.

[9] Cavigelli L , Magno M , Benini L . Accelerating real-time embedded scene labeling with convolutional networks[J]. 2015:1-6.

[10] Chen Y H , Krishna T , Emer J S , et al. Eyeriss: An Ener-gy-Efficient Reconfigurable Accelerator for Deep Convolu-tional Neural Networks[C]// Solid-state Circuits Conference. IEEE, 2016.

[11] Qiu J , Wang J , Yao S , et al. Going Deeper with Embedded FPGA Platform for Convolutional Neural Network[C]// Pro-ceedings of the 2016 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays. ACM, 2016.2001 March.

[12] 傅思揚,陳華,郁發新.基于RISC-V的卷積神經網絡處理器設計與實現[J].微電子學與計算機,2020,37(4):49-54.

【通聯編輯:梁書】