一種100 G EPON系統(tǒng)RS編碼器設(shè)計與實現(xiàn)

杜慧敏,張英杰,張麗果

(西安郵電大學(xué) 電子工程學(xué)院,陜西 西安 710121)

以太網(wǎng)無源光網(wǎng)絡(luò)(Ethernet Passive Optical Network,EPON)在物理層采用無源光網(wǎng)絡(luò)(Passive Optical Network,PON)技術(shù),在鏈路層使用以太網(wǎng)協(xié)議,利用PON的拓?fù)浣Y(jié)構(gòu)實現(xiàn)了以太網(wǎng)的接入,具有低成本、高帶寬、擴展性強、靈活快速地服務(wù)重組、與現(xiàn)有以太網(wǎng)兼容以及管理方便等特點,成為寬帶接入網(wǎng)一種有效的通信方法。

受4K/8K超高清視頻、虛擬現(xiàn)實和智慧家庭等市場應(yīng)用的強烈驅(qū)動,用戶帶寬以每年50%的速率增長[1],當(dāng)前主流的10 G EPON技術(shù)越來越無法滿足市場需求,高帶寬、高穩(wěn)定性的100 G EPON技術(shù)將成為未來全球超帶寬產(chǎn)業(yè)中的主要光接入網(wǎng)技術(shù)[2]。

為了檢測和糾正通信過程中信息發(fā)生的錯誤,在通信系統(tǒng)中常用前向糾錯碼(Forward Error Correct,FEC)技術(shù)來保證通信的質(zhì)量。在FEC的碼類中,里德-所羅門(Reed-Solomon,RS)編碼是一種糾錯能力較強的線性分組碼[3]。RS編碼是基于有限域伽羅華域(Galois Field,GF)的碼組,其所有的校驗碼符號均取自伽羅華域,編碼中所有運算都在伽羅華域中進(jìn)行。RS碼由于其編碼相對簡單、編碼結(jié)構(gòu)穩(wěn)定性強,糾錯能力強等特點[4],被廣泛應(yīng)用于高速數(shù)字通信系統(tǒng)中,以滿足數(shù)據(jù)通信可靠性的要求[5]。

通常使用RS(n,k)表示不同糾錯能力的RS碼,其中n代表碼長符號的數(shù)目,k代表待編碼數(shù)據(jù)單元(Code Word,CW)符號的數(shù)目,n、k之間的差值越大,糾錯能力就越強。電氣與電子工程師協(xié)會(Institute of Electrical and Electronics Engineers,IEEE)802.3-2015版標(biāo)準(zhǔn)使用RS (255,223)作為10 G EPON的糾錯碼標(biāo)準(zhǔn)。而對于100 G EPON系統(tǒng),IEEE并沒有規(guī)定需要采用的FEC糾錯碼類,通常采用RS碼或者低密度奇偶校驗(Low Density Parity Check Code,LDPC)碼。

從100 G EPON系統(tǒng)實現(xiàn)上來看,目前主流的方法是采用4個25 G EPON子系統(tǒng)來構(gòu)建100 G EPON系統(tǒng)。在國際標(biāo)準(zhǔn)中尚沒有明確規(guī)定25 G EPON系統(tǒng)糾錯碼標(biāo)準(zhǔn),文獻(xiàn)[6]建議在25 G EPON系統(tǒng)中依舊采用RS編碼作為糾錯碼,通過分析不同n、k值的RS碼在25 G EPON系統(tǒng)中的性能,從編碼效率、冗余度、碼長和連續(xù)糾錯能力等4個方面綜合考慮,發(fā)現(xiàn)選用RS(1 023,847)碼作為25 G EPON系統(tǒng)的前向糾錯碼時,可以在不影響系統(tǒng)傳輸速率的情況下達(dá)到最優(yōu)的編碼增益。

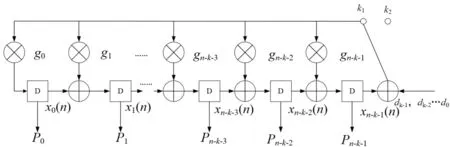

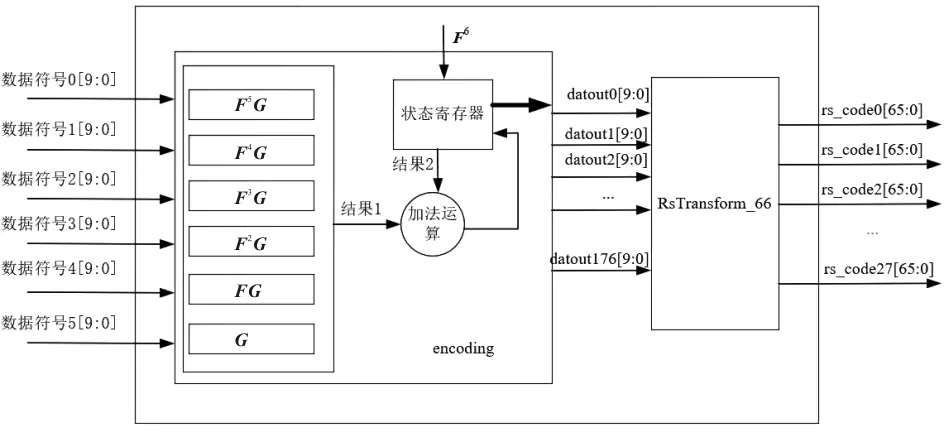

在RS編碼算法和編碼器設(shè)計上,線性反饋移位寄存器(Linear Feedback Shift Register,LFSR)可以直接實現(xiàn)串行編碼,但是,這種做法采用串行處理的做法,需要將待編碼的數(shù)據(jù)符號依次串行移入編碼電路,處理周期較長、計算效率低,不能滿足高速通信系統(tǒng)的要求[7]。針對這一問題,采用并行方式實現(xiàn)RS編碼器是主流的方法,2013年,文獻(xiàn)[8]借鑒文獻(xiàn)[9]提出的高速循環(huán)冗余校驗碼(Cyclic Redundancy Check,CRC)并行編碼方法,將該方法用于并行RS編碼,實現(xiàn)了靈活性更強、可用于并行編碼計算的RS(255,223)編碼器,滿足了10 G EPON的系統(tǒng)要求。2015年,文獻(xiàn)[10]實現(xiàn)了一種編碼利用率更高的RS(624,k)編碼器(615 從目前的研究看,還沒有一種通用的RS編碼器并行設(shè)計及實現(xiàn)方法。另外,在現(xiàn)場可編程邏輯門陣列(Field Programmable Gate Grray,FPGA)中實現(xiàn)100 G EPON RS編碼依然面臨巨大的挑戰(zhàn),即單通道編碼器最高工作頻率要達(dá)到390.625 MHz,以保證最高數(shù)據(jù)吞吐率達(dá)到25 Gbit/s。 擬提出一種100 G EPON系統(tǒng)RS編碼器設(shè)計與實現(xiàn)方法。由4路數(shù)據(jù)傳輸速率為25 Gbit/s的通信子系統(tǒng)構(gòu)成100 G EPON通信系統(tǒng)。選用適用于25 G EPON通信系統(tǒng)并且性能更好的RS碼組作為子系統(tǒng)編碼器的碼型。通過分析RS編碼器的n、k等參數(shù)以及待編碼數(shù)據(jù)的特性,求出編碼電路的并行系數(shù),計算RS編碼器的并行度。合理選擇RS編碼器的并行度并利用多路切換技術(shù)、數(shù)據(jù)并行化計算等方法,設(shè)計一種可用于100 G EPON通信系統(tǒng)的RS編碼器。 RS碼為定義在有限域GF(2m)上的線性分組碼[13],其中m為該碼組的符號寬度,其對應(yīng)的生成多項式為 其中,ai為對應(yīng)伽羅華域中的第i個元素,2t為n與k的差值。 待編碼數(shù)據(jù)的信息多項式為 d(x)=dk-1xk-1+…+d1x+d0 其中,dk-1,…,d1、d0表示k個符號的待編碼數(shù)據(jù)。 不同碼型的RS碼組其生成多項式也不同[14]。用生成多項式g(x)除x2td(x),商式記為Q(x),余式記為r(x)。計算過程可表示為[15] 余式r(x)即為RS(n,k)編碼的校驗多項式,余式r(x)可以表示為 r(x)=rn-k-1xn-k-1+…+r1x1+r0 其中,rn-k-1、…、r1、r0表示生成的n-k個符號的校驗碼。 待編碼信息多項式與RS編碼校驗多項式共同構(gòu)成碼組多項式[16]c(x),其表達(dá)式為 c(x)=x2td(x)+r(x)=dk-1xn-1+…+ 經(jīng)典RS編碼器[17]通常采用除法方式實現(xiàn)編碼過程,其編碼器主要采用一組線性反饋移位寄存器(Linear Feedback Shift Register,LFSR)。經(jīng)典RS(n,k)串行編碼器的電路結(jié)構(gòu)示意圖如圖1所示。其中,g0、g1、…、gn-k-1為生成多項式g(x)的系數(shù),dk-1、…、d1、d0為編碼器的輸入數(shù)據(jù)符號,x0(n)、x1(n)、…、xn-k-1(n)為n時刻各個寄存器的狀態(tài)值,P0、P1、…、Pn-k-1為該編碼電路計算k個周期后編碼的結(jié)果,即n-k個校驗符號。 圖1 經(jīng)典RS串行編碼器結(jié)構(gòu) RS串行編碼器電路包括3個工作過程。首先,開關(guān)調(diào)至k1,將k個數(shù)據(jù)符號dk-1、…、d1、d0串行移入電路中。一旦所有的數(shù)據(jù)符號全部移入電路中,寄存器n-k個狀態(tài)值x0(n)、x1(n)、…、xn-k-1(n)就構(gòu)成了RS校驗碼。其次,將開關(guān)調(diào)至k2,以關(guān)閉反饋連接。最后,移出n-k個校驗符號到信道中。這n-k個校驗符號與之前的k個數(shù)據(jù)符號共同構(gòu)成了一個完整的碼字。 可以看出,該串行編碼器每次只能處理1個輸入符號,編碼時延為k個周期。該串行編碼每個時鐘周期處理的符號數(shù)有限,制約了編碼器的計算效率,不符合高速系統(tǒng)的性能要求[18]。采用串行方式實現(xiàn)的RS編碼器,由于其編碼效率低、編碼周期長等缺點,限制了其應(yīng)用范圍[19]。 文獻(xiàn)[20]最早使用狀態(tài)空間的方法處理并行CRC編碼的問題,之后有大量文獻(xiàn)使用了相同的方法研究不同使用情況下的CRC并行編碼問題。CRC碼與RS碼都屬于循環(huán)碼,編碼原理相同,都可以使用LFSR進(jìn)行編碼,這就決定了也可以使用狀態(tài)空間這一方法來解決RS碼的并行化編碼問題[21]。 采用狀態(tài)空間的方法重新描述上述LFSR的工作原理,串行RS編碼電路時刻n寄存器的狀態(tài)可以表述為 (1) 其中:x0(n)、x1(n)、…、xn-k-1(n)表示時刻n每個寄存器的狀態(tài),在下一時刻n+1,寄存器的狀態(tài)按照式(1)更新;m(n)表示n時刻移入電路的數(shù)據(jù)符號,所有寄存器的初始值均為0,時刻0時進(jìn)入寄存器序列的消息符號為m(0),時刻0結(jié)束時寄存器的狀態(tài)為x(1),以此類推,時刻1移入編碼電路的數(shù)據(jù)符號為m(1),時刻n-k-1移入編碼電路的最后一個數(shù)據(jù)符號為m(n-k-1),該時刻結(jié)束時寄存器序列里的值即為校驗碼數(shù)據(jù)。 若將其生成多項式系數(shù)組成的矩陣記為G,生成多項式系數(shù)與常量組成的方陣記為F,那么式(1)可以表示為 x(n+1)=Fx(n)+m(n)G (2) 為了得出并行編碼的算法,只需要對式(2)進(jìn)行超前遞推即可,遞推的層數(shù)決定了并行編碼的符號寬度。根據(jù)式(2),可以推導(dǎo)出q個數(shù)據(jù)符號并行RS編碼的計算表達(dá)式為 x(n+q)=Fqx(n)+m(n)Fq-1G+ (3) 由于g0、…、gn-k-1等系數(shù)可以預(yù)先計算出來,意味著式(1)中F與G就是確定的,可以在RS編碼計算前提前計算出來。式(3)可以同時處理并行q個數(shù)據(jù)符號,于是就實現(xiàn)了并行編碼處理。 針對不同的應(yīng)用場景,用RS并行編碼電路的并行度來衡量其編碼效率[22]。將編碼器理論上需要同時處理的數(shù)據(jù)符號數(shù)定義為編碼電路并行系數(shù),實際上需要處理的數(shù)據(jù)符號的個數(shù)定義為編碼電路的并行度。并行系數(shù)理論上可以是任意正數(shù),但并行度一定是正整數(shù)。 設(shè)RS(n,k)編碼器的數(shù)據(jù)符號位寬為m,編碼器的輸入數(shù)據(jù)位寬為Bw,CW的更新周期為Tcw個時鐘周期,則Tcw與m、n以及Bw之間的關(guān)系可以表述為 (4) 為了在Tcw個周期內(nèi)處理完k個數(shù)據(jù)符號,需要計算出每個時鐘周期電路需要處理的符號數(shù),即電路的并行系數(shù),其計算表達(dá)式為 (5) 電路并行系數(shù)θ可以是任意的正數(shù),但是在電路實現(xiàn)的時候,并行度只能是整數(shù),因此,將并行系數(shù)θ向上取整,得出編碼電路并行度β的取值范圍為 (6) 雖然并行度越大,編碼電路可同時處理的數(shù)據(jù)符號就越多,越有利于提高編碼電路的計算效率[23],但是,由于β只是對并行系數(shù)θ向上取整,并不等于并行系數(shù),采用β作為電路并行度的編碼電路,需要計算出實際的編碼計算周期,編碼計算周期的計算表達(dá)式為 (7) 與使用Tcw相比,采用Tencode作為編碼周期會造成不同程度的周期浪費,并且β的值越大,浪費的周期數(shù)越多。在實際的操作過程中,β的上界受輸入數(shù)據(jù)的時序關(guān)系或編碼電路可用資源數(shù)的制約,往往存在有一個界限。 由式(6)可得編碼電路最小并行度為 (8) 更大的并行度意味著更大的電路面積,因此,在資源受限的情況下,選擇最小并行度βmin作為RS編碼電路的最優(yōu)并行度,可以使電路占用最小的硬件資源。另外,電路選擇最小并行度βmin進(jìn)行并行化編碼計算,以滿足輸入數(shù)據(jù)的時序要求,最大程度地減少編碼計算浪費的周期數(shù),提高編碼效率。 由4個數(shù)據(jù)吞吐率為25 Gbit/s的通信子系統(tǒng)構(gòu)成100 G EPON通信系統(tǒng)。100 G EPON通信系統(tǒng)的結(jié)構(gòu)示意圖如圖2所示,光線路終端(Optical Line Terminal,OLT)設(shè)備承載4個OLT子通信系統(tǒng),每個OLT子系統(tǒng)通過光分配網(wǎng)(Optical Distribution Network,ODN)與光網(wǎng)絡(luò)單元(Optical Network Unit,ONU)設(shè)備相連,構(gòu)成4個25 G EPON子通信系統(tǒng),從而組成100 G EPON通信系統(tǒng)。 圖2 100 G EPON通信系統(tǒng)結(jié)構(gòu) 根據(jù)電氣與電子工程師協(xié)會(Institute of Electrical and Electronics Engineers,IEEE)802.3-2015等相關(guān)協(xié)議,在Intel Stratix 10系列的1SG280LN2F43 FPGA芯片上實現(xiàn)4×25 G EPON系統(tǒng)對RS編碼器的處理能力有著如下的要求。 1)在數(shù)據(jù)接口寬度為65 bit的條件下,編碼器的工作頻率需大于390.625 MHz,以滿足子系統(tǒng)25 Gbit/s的數(shù)據(jù)吞吐率要求。 2)在CW的更新周期為158個時鐘周期的條件下,編碼器需要具備高速數(shù)據(jù)的處理能力。 3)FPGA芯片需要承載4個EPON系統(tǒng),分配給單路編碼器的芯片硬件資源有限,經(jīng)計算,單路編碼器硬件資源占用最大值為板級資源的3%,因此,需要在有限的資源上實現(xiàn)該編碼器。 實現(xiàn)的25 G EPON子通信系統(tǒng)中RS編碼器的輸入是65 bit位寬的數(shù)據(jù),碼組類型為RS(1 023,847),數(shù)據(jù)符號位寬m為10 bit。利用式(4)和式(5),得到CW的更新周期Tcw為158個時鐘周期,并行度系數(shù)θ為5.36,因此,選擇的最優(yōu)并行度βmin為6,即編碼器可在一個時鐘周期內(nèi)并行處理6個數(shù)據(jù)符號。由于電路并行度βmin只是接近并行度系數(shù)θ的最小整數(shù),并且根據(jù)式(7)可以計算出,編碼器實際的計算周期為142個時鐘周期,與Tcw(158個時鐘周期)相比較,存在16個時鐘周期的浪費。 在確定電路并行度βmin后,根據(jù)式(3)可得出6倍并行編碼電路的推導(dǎo)公式為 x(n+6)=F6x(n)+m(n)F5G+ (9) 根據(jù)上一部分的并行算法設(shè)計RS(1 023,847)并行編碼器電路架構(gòu)。編碼器電路由數(shù)據(jù)輸入與輸出電路和編碼電路核心計算模塊組成。編碼器整體架構(gòu)示意圖如圖3所示。 圖3 并行編碼電路架構(gòu) 2.3.1 數(shù)據(jù)輸入與輸出電路 編碼器需要適用于25 G EPON通信系統(tǒng),需要滿足系統(tǒng)的高數(shù)據(jù)吞吐率的要求,為此,編碼器電路架構(gòu)采用多路切換技術(shù)的采用乒乓電路結(jié)構(gòu)。與不采用乒乓結(jié)構(gòu)的電路相比,在相同電路時鐘頻率的條件下可以達(dá)到2倍的數(shù)據(jù)吞吐率。其電路內(nèi)部包括2套相同的子編碼電路,輸入數(shù)據(jù)以CW為單元,緩存單元為異步先進(jìn)先出存儲器(First in First Out,FIFO),經(jīng)過乒乓電路中的輸入仲裁寫入兩個緩存單元“fifo_in”,其不但要滿足跨時鐘域條件下數(shù)據(jù)的存儲,保證數(shù)據(jù)不丟失,而且還要滿足最大程度上節(jié)省電路資源的要求,為此,經(jīng)過實驗發(fā)現(xiàn),將輸入緩存深度設(shè)為128最為合適。 數(shù)據(jù)從緩存單元分別進(jìn)入兩個子編碼電路進(jìn)行編碼計算,編碼完畢后,寫入緩存深度也為設(shè)置為128的緩存單元“fifo_out”,深度的選取與輸入緩存的深度選取原則一致,數(shù)據(jù)在乒乓電路的輸出仲裁下,分別從緩存中相互切換的輸出。 編碼電路的外部輸入數(shù)據(jù)的寫時鐘為系統(tǒng)時鐘,其頻率為390.625 MHz。由于編碼器采用乒乓操作,則編碼電路內(nèi)部只需采用工作頻率為195.312 5 MHz的時鐘即可滿足系統(tǒng)需求,實現(xiàn)了低速模塊處理高速數(shù)據(jù)流的功能。 2.3.2 核心計算模塊 編碼電路核心計算模塊主要包括位寬轉(zhuǎn)換模塊、編碼計算模塊等。 位寬轉(zhuǎn)換模塊對輸入數(shù)據(jù)進(jìn)行并行化處理。本文設(shè)計采用RS(1 023,847)碼組,一個CW中有效數(shù)據(jù)周期持續(xù)130 個時鐘周期,數(shù)據(jù)位寬為66 bit。該模塊首先將66 bit有效數(shù)據(jù)的最低位去掉,形成130個時鐘周期位寬為65 bit的待校驗數(shù)據(jù),由于每個CW中實際待校驗數(shù)據(jù)為8 450 bit,因此,在其之后添加20 bit的“0”,構(gòu)成8 470 bit即847 個數(shù)據(jù)符號的待校驗數(shù)據(jù)。之后,將數(shù)據(jù)進(jìn)行6路并行化處理,每路一個10 bit符號的數(shù)據(jù)輸出。 編碼計算模塊的設(shè)計基于式(9),核心計算模塊架構(gòu)示意圖如圖4所示。 圖4 核心計算模塊架構(gòu) 該模塊由編碼模塊“encoding”以及位寬轉(zhuǎn)換模塊“RsTransform_66”模塊組成。編碼模塊根據(jù)選擇的最優(yōu)并行度βmin設(shè)計,“encoding”模塊中電路主要負(fù)責(zé)并行度為6的編碼計算,即按照每個時鐘輸入6個數(shù)據(jù)符號進(jìn)行計算,其中狀態(tài)寄存器主要計算每個周期更新的狀態(tài)x(n)。在進(jìn)行編碼計算時,每個周期內(nèi),并行輸入的6個數(shù)據(jù)符號分別與乘法運算模塊F5G、F4G、F3G、F2G、FG和G進(jìn)行伽羅華域乘法運算并相加,記為結(jié)果1,另外,將乘數(shù)F6與當(dāng)前時刻狀態(tài)寄存器中的狀態(tài)值x(n)進(jìn)行伽羅華域乘法運算,其結(jié)果記為2。將結(jié)果1與結(jié)果2相加,并將和反饋給狀態(tài)寄存器x(n),作為下個計算周期的初始狀態(tài)值。如此,即實現(xiàn)了并行6 路編碼計算。該計算過程總共需要142 個計算周期,計算結(jié)束時,所獲得的176 個狀態(tài)即為校驗碼字,由狀態(tài)寄存器輸出,完成編碼計算過程。 計算出的RS校驗碼為176 個校驗符號的數(shù)據(jù)格式,每個符號位寬為10 bit,與編碼器外部的數(shù)據(jù)位寬66 bit不匹配,為此,將數(shù)據(jù)輸入至編碼位寬轉(zhuǎn)換模塊“RsTransform_66”,經(jīng)過添加同步頭數(shù)據(jù)和補零操作,將其轉(zhuǎn)換為每個時鐘周期66 bit的數(shù)據(jù)格式輸出。 使用Matlab 2012b軟件仿真編碼算法,利用Modelsim軟件仿真電路軟件,采用Quartus Prime Standard Edition 18.1軟件與Intel 1SG280LN2F43 FPGA 芯片實現(xiàn)電路。 為了驗證編碼器的功能正確性,可對比算法仿真結(jié)果與硬件電路仿真結(jié)果的差異。 為了方便對比二者的結(jié)果,在待編碼的CW中構(gòu)造全“1”的CW,即該CW由8 450 bit全“1”構(gòu)成。 由于采用的是RS(1 023,847)碼組,在算法仿真與硬件仿真中的CW為8 470 bit,因此,需要在事先提供的8 450 bit數(shù)據(jù)后添加20 bit的全“0”數(shù)據(jù),構(gòu)成8 470bit的待編碼信息。 在進(jìn)行Matlab編程時,首先輸入RS(1 023,847)碼組的生成多項式,之后輸入由8 450bit全“1”數(shù)據(jù)以及20 bit全“0”數(shù)據(jù)構(gòu)成的CW,得出經(jīng)Matlab計算的編碼結(jié)果如圖5所示,其中校驗碼符號以十進(jìn)制數(shù)來表示,高符號位數(shù)據(jù)處于每一行的左側(cè)。在進(jìn)行硬件仿真時,利用Verilog語言,基于Modelsim仿真軟件,CW的構(gòu)造也由8 450 bit全“1”數(shù)據(jù)以及20 bit全“0”數(shù)據(jù)構(gòu)成,硬件仿真的部分結(jié)果如圖6所示,由于校驗碼符號過多,因此只顯示了部分低符號位的校驗碼符號與第174至175符號位的校驗碼符號。 對比算法仿真與硬件仿真的結(jié)果可以看出,兩者的RS(1 023,847)編碼結(jié)果相同,表明硬件電路的邏輯功能正確。 圖5 Matlab編碼仿真結(jié)果 圖6 Modelsim編碼仿真結(jié)果 利用基于Stratix10芯片的邏輯綜合工具對設(shè)計的編碼電路進(jìn)行綜合,得出該編碼電路最高時鐘頻率已經(jīng)達(dá)到390.625 MHz,表明該電路可以滿足25 G EPON子通信系統(tǒng)對編碼器在時鐘頻率上的要求。 另外,對本編碼電路的資源消耗數(shù)進(jìn)行分析。由于本電路基于的FPGA芯片的基本單元庫為可編程邏輯單元(Adaptive Logic Module,ALM),每個ALM包括1組查找表、2個寄存器、2個加法器和一些其他布線。編碼模塊的邏輯資源消耗以ALM為單位來表示。根據(jù)編碼模塊綜合結(jié)果可以得出,編碼模塊的總資源占用為17 884個ALM。而Stratix10芯片可用的ALM數(shù)為933 120個ALM,25 G EPON子通信系統(tǒng)給RS編碼器分配的資源占用率為3%,所提設(shè)計電路的資源占用率為1.91%,符合25 G EPON子通信系統(tǒng)的要求,也符合100 G EPON通信系統(tǒng)的要求。 將所提設(shè)計的RS(1 023,847)編碼電路與10 G EPON通信系統(tǒng)中所采用的RS(255,223)編碼電路的性能進(jìn)行對比,對比結(jié)果如表1所示。 表1 兩種RS編碼器的性能對比 從上述對比結(jié)果可知,所提設(shè)計的編碼電路具有更大的數(shù)據(jù)吞吐率,可應(yīng)用于更高速的通信系統(tǒng),糾錯能力更強,幾乎是RS(255,223)編碼器糾錯能力的7倍,在相同的誤幀率情況下,設(shè)計的編碼電路可以帶來更高的編碼增益,并且,編碼電路的最大時鐘頻率也大于RS(255,223)編碼器的最大時鐘頻率。設(shè)計的編碼電路在性能方面具有非常明顯的優(yōu)勢,在資源占用方面,僅僅為RS(255,223)編碼器的10倍,相對而言,設(shè)計的編碼電路具有更加良好的性能。 在FPGA的實際測試中,設(shè)計了RS(1 023,847)碼的性能測試平臺,測試平臺結(jié)構(gòu)示意圖如圖7所示。 圖7 性能測試平臺結(jié)構(gòu) 測試平臺由數(shù)據(jù)測試儀和光衰減器,以及包含EPON電路的OLT芯片與ONU芯片等設(shè)備構(gòu)成。1個OLT設(shè)備與4個ONU設(shè)備同時通信。測試過程中利用數(shù)據(jù)測試儀生成待編碼數(shù)據(jù)并發(fā)送到OLT設(shè)備中,數(shù)據(jù)經(jīng)過OLT設(shè)備后,進(jìn)行RS(1 023,847)編碼運算后輸出,輸出后的數(shù)據(jù)通過光纖傳輸至光衰減器,再從光衰減器到1號與4號ONU設(shè)備,每個ONU設(shè)備對編碼數(shù)據(jù)進(jìn)行譯碼,最終把譯碼糾錯后的數(shù)據(jù)輸出到數(shù)據(jù)測試儀,數(shù)據(jù)測試儀將接收到的數(shù)據(jù)與發(fā)送的數(shù)據(jù)進(jìn)行比對,分析每個25 G EPON通信子系統(tǒng)的誤碼情況。若RS編譯碼器具有良好的數(shù)據(jù)糾錯能力,達(dá)到系統(tǒng)要求的編碼增益,則表明本編碼器具有正確的邏輯功能,并且符合高速EPON系統(tǒng)的要求。 具體的測試方法為,利用數(shù)據(jù)測試儀向OLT發(fā)送固定幀長為64的數(shù)據(jù),OLT將數(shù)據(jù)傳輸至每個ONU,ONU將數(shù)據(jù)返回數(shù)據(jù)測試儀來分析誤碼情況。光衰減器用來調(diào)節(jié)光功率,可以改變OLT至ONU傳輸過程中的誤碼率。整個測試過程分為兩步。第一步,關(guān)閉帶有FEC糾錯功能的RS編譯碼器進(jìn)行數(shù)據(jù)測試,測試從10-8到10-2等不同數(shù)量級的誤幀率(Frame Error Rate)水平情況下信噪比數(shù)值。第二步,開啟帶有FEC糾錯功能的RS編譯碼器進(jìn)行數(shù)據(jù)測試,測試過程與第一步一致。 對用上述測試方法測試的數(shù)據(jù)進(jìn)行整理,得出4個25 G EPON通信子系統(tǒng)接收的光功率-誤幀率結(jié)果,如圖8所示。其中,F(xiàn)EC1、FEC2、FEC3、FEC4等4條折線分別表示在開啟FEC功能的情況下,OLT與第1、第2、第3和第4號ONU同時進(jìn)行通信時,信道在不同誤幀率情況下的信噪比數(shù)值;NO FEC1、NO FEC2、NO FEC3、NO FEC4等4條折線分別表示在關(guān)閉FEC的情況下,信道在不同誤幀率情況下的信噪比數(shù)值。 圖8 實際測試的信噪比-誤幀率結(jié)果 從圖8可以看出,對于4條子通信線路,在相同誤幀率的情況下,開啟FEC能帶來明顯的編碼增益,所設(shè)計的RS(1 023,847)編譯碼器可以明顯地改善4條通信線路的信號傳輸質(zhì)量,在誤幀率達(dá)到1×10-7時,開啟FEC可以帶來平均8.0 dB的編碼增益,能夠滿足100 G EPON系統(tǒng)對糾錯能力需求。 提出了一種適合于100 G EPON系統(tǒng)的通用RS編碼器的設(shè)計方法。由4路25 G子系統(tǒng)構(gòu)成100 G 通信系統(tǒng)。綜合考慮碼型性能和糾錯能力,選用RS(1 023,847)作為編碼器的碼組。提出了一種通用的編碼電路并行度計算方法,根據(jù)編碼器參數(shù)與輸入數(shù)據(jù)的特點,通過計算電路并行系數(shù)進(jìn)而計算編碼電路的并行度。通過選擇合適的并行度,提出了適合于25 G EPON子系統(tǒng)的RS(1 023,847)的高速編碼器設(shè)計方案,4路編碼器同時工作,利用多路切換技術(shù)、數(shù)據(jù)并行化等技術(shù),實現(xiàn)了一種由4路25 G EPON子系統(tǒng)構(gòu)成的100 G EPON通信系統(tǒng)的高速RS編碼器。實際測試結(jié)果表明,設(shè)計編譯碼器的數(shù)據(jù)吞吐率和糾錯能力滿足100 G EPON系統(tǒng)要求。1 RS碼的原理與性質(zhì)

1.1 RS串行編碼原理

d1xn-k+1+d0xn-k+rn-k-1xn-k-1+…+r1x1+r01.2 基于LFSR的串行RS編碼方法

1.3 并行RS編碼方法

m(n+1)Fq-2G+…+m(n+q-2)FG+

m(n+q-1)G1.4 RS編碼的并行度計算

2 并行編碼器的實現(xiàn)

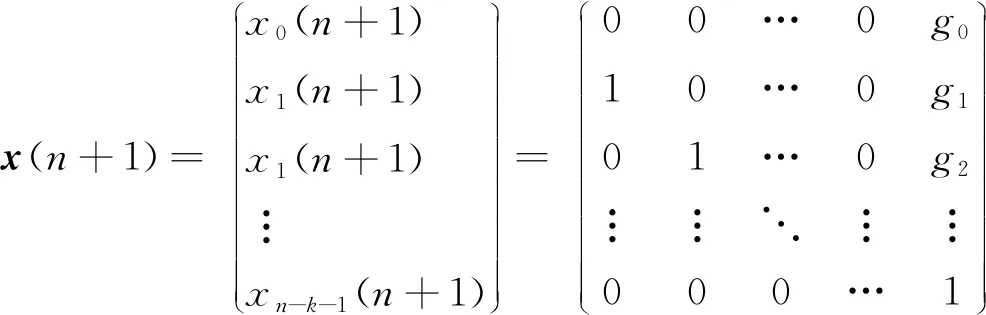

2.1 100 G EPON通信系統(tǒng)

2.2 RS編碼器并行度的選擇

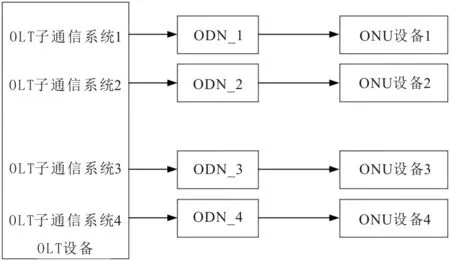

m(n+1)F4G+m(n+2)F3G+m(n+3)F2G+m(n+4)FG+m(n+5)G2.3 編碼器整體架構(gòu)設(shè)計

3 仿真結(jié)果及分析

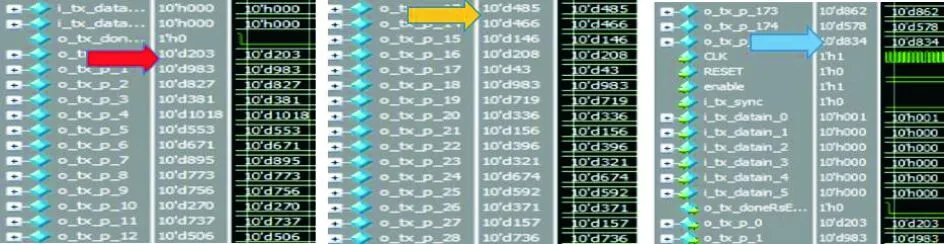

3.1 算法與硬件仿真

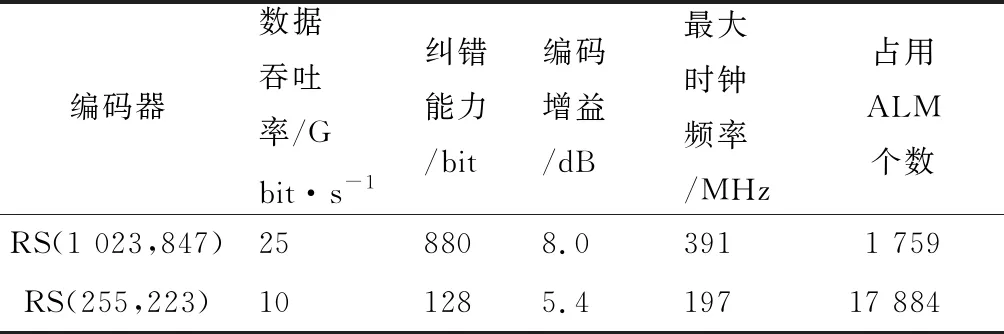

3.2 電路時序與資源分析

3.3 編碼器的硬件測試

4 結(jié)語