一種多通道高速高精度PXIe 數(shù)據(jù)采集模塊設(shè)計(jì)*

唐新懿 ,曹 平 ,解立坤 ,李 超 ,黃錫汝 ,安 琪

(1.中國科學(xué)技術(shù)大學(xué) 核探測與核電子學(xué)國家重點(diǎn)實(shí)驗(yàn)室,安徽 合肥230026;2.中國科學(xué)技術(shù)大學(xué) 近代物理系,安徽 合肥230026)

0 引言

數(shù)據(jù)采集技術(shù)是信息技術(shù)的重要內(nèi)容,它研究數(shù)據(jù)的采集、存儲(chǔ)、處理和控制問題[1]。 現(xiàn)如今,多通道數(shù)據(jù)采集系統(tǒng)已經(jīng)被廣泛應(yīng)用于諸如核物理、高能物理、航空航天、醫(yī)療衛(wèi)生、通信等各個(gè)領(lǐng)域中。 隨著數(shù)據(jù)采集需求的日趨復(fù)雜[2],人們對(duì)采集系統(tǒng)性能指標(biāo)的要求也越來越高, 例如高采樣率、高精度等[3]。 IC 工藝的飛速發(fā)展使得ADC 芯片的性能不斷提升[4],這讓數(shù)據(jù)采集系統(tǒng)同時(shí)具備高采樣率與高精度成為可能。 本文設(shè)計(jì)了一種基于FPGA 的 八 通 道、500 MS/s 采 樣 率、14 bit 采 樣 精 度的數(shù)據(jù)采集模塊,該模塊為標(biāo)準(zhǔn)的PXIe 插卡模塊,通過PXIe 機(jī)箱背板總線以及機(jī)箱控制器與上位機(jī)進(jìn)行通信,最終實(shí)現(xiàn)了上位機(jī)與FPGA 協(xié)同完成數(shù)據(jù)采集與性能測試。

1 采集卡總體設(shè)計(jì)

數(shù)據(jù)采集卡采用子母板的結(jié)構(gòu):ADC 子板和數(shù)據(jù)讀出母板,子板主要負(fù)責(zé)對(duì)模擬信號(hào)進(jìn)行調(diào)理和采集,母板負(fù)責(zé)將數(shù)據(jù)傳輸?shù)缴衔粰C(jī),兩塊板通過FPGA Mezzanine Card(FMC)連 接 器 相 連。 FMC 標(biāo) 準(zhǔn)是一種針對(duì)FPGA 的夾層卡標(biāo)準(zhǔn),通過它可以使設(shè)計(jì)更具模塊化與可拓展性[5]。 模擬信號(hào)從子板輸入,首先會(huì)經(jīng)過模擬調(diào)理電路,對(duì)信號(hào)進(jìn)行放大、偏置調(diào)整、單端轉(zhuǎn)差分、濾波后進(jìn)入ADC 進(jìn)行模數(shù)轉(zhuǎn)換,采集下來的數(shù)據(jù)通過高速串行接口JEDEC Standard No.204B(JESD204B)經(jīng)由FMC 連接器傳輸?shù)侥赴宓腇PGA,再通過Peripheral Component Interconnect Express(PCIe)總線傳輸至PXIe 機(jī)箱控制器,最后可通過控制器網(wǎng)口傳輸?shù)缴衔粰C(jī)。 采集卡的參數(shù)配置與數(shù)據(jù)上傳可通過上位機(jī)進(jìn)行靈活控制。 采集系統(tǒng)總體結(jié)構(gòu)如圖1 所示。

圖1 采集系統(tǒng)總體結(jié)構(gòu)

2 ADC 子板設(shè)計(jì)

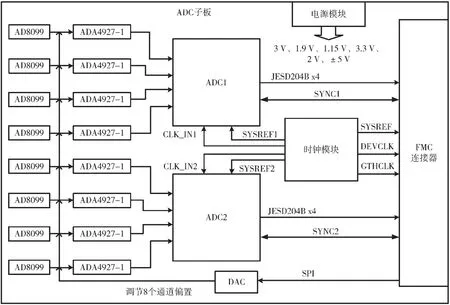

子板電路結(jié)構(gòu)如圖2 所示,主要包含兩級(jí)放大電路、時(shí)鐘模塊、電源模塊、ADC 和DAC。 其中,兩級(jí)放大電路包含一級(jí)單端放大器(AD8099)和一級(jí)單端轉(zhuǎn)差分放大器(ADA4927-1),DAC 產(chǎn)生的模擬電平輸送到差分放大器的反相輸入端,可調(diào)節(jié)信號(hào)的直流偏置。 單片ADC 為四通道差分輸入,因此共有2 片ADC,對(duì)應(yīng)8 通道模擬信號(hào)輸入。 時(shí)鐘模塊為2 片ADC 提供必要的采樣時(shí)鐘(CLK_IN1、CLK_IN2)和參考時(shí)鐘(SYSREF1、SYSREF2),同時(shí)為母板的FPGA提供系統(tǒng)時(shí)鐘(DEVCLK)、參考時(shí)鐘(SYSREF)和數(shù)據(jù)傳輸時(shí)鐘(GTHCLK)。 電源模塊需要為子板所有的芯片供電,提 供了3 V、1.9 V、1.15 V、3.3 V、±5 V 等多種供電電壓,此外,還為單端轉(zhuǎn)差分放大器提供了2 V 的共模電壓,以適配ADC 的輸入要求。

為了實(shí)現(xiàn)8 個(gè)采集通道的同步,需要滿足2 片ADC 接收到的采樣時(shí)鐘、參考時(shí)鐘、SYNC 信號(hào)各自都對(duì)齊[6]。 因此,在設(shè)計(jì)中讓2 片ADC 的時(shí)鐘來源于同一個(gè)時(shí)鐘芯片,并且在PCB 布線時(shí)通過等長處理來保證時(shí)鐘模塊輸出到2 片ADC 的采樣時(shí)鐘、參考時(shí)鐘各自的相位對(duì)齊。 由FPGA 給到ADC 的SYNC 信號(hào),可在邏輯設(shè)計(jì)時(shí)由同一個(gè)核產(chǎn)生,以保證相位的對(duì)齊。

2.1 兩級(jí)放大電路

模擬信號(hào)從子板輸入后,需要經(jīng)過兩級(jí)放大電路的模擬調(diào)理,調(diào)理包含線性放大、直流偏置調(diào)節(jié)、單端轉(zhuǎn)差分、濾波,兩級(jí)放大電路的具體結(jié)構(gòu)如圖3所示(NC 表示不連接)。 所選用的單端放大器(AD8099)和差分放大器(ADA4927-1)均為極低噪聲的放大器,AD8099 輸入噪聲密度為輸入噪聲密度為除此之外,兩款放大器還擁有較好的諧波失真性能[7-8]。

兩級(jí)放大的電路結(jié)構(gòu)讓增益選擇更加靈活,可以通過更換電阻的阻值來適應(yīng)不同的增益需求。 第一級(jí)放大器AD8099 的增益為:

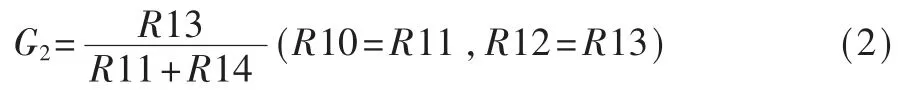

第二級(jí)放大器ADA4927-1 的增益約為:

圖2 子板結(jié)構(gòu)框圖

圖3 兩級(jí)放大電路

圖3 電路中第一級(jí)放大增益為3,第二級(jí)放大增益為2。 在只需要一級(jí)放大或需要小于1 的增益時(shí),也可通過調(diào)整電阻阻值將第一級(jí)放大器旁路掉。 在只使用ADA4927-1 時(shí),需要增加匹配電阻R18,以保證輸入阻抗為50 Ω。 差分放大器輸入阻抗為:

為了達(dá)到50 Ω 的輸入阻抗匹配,需滿足:

同時(shí),反相輸入端的匹配電阻也需做相應(yīng)的更改:

DAC 產(chǎn)生的模擬電平從差分放大器反相端輸入,它與差分放大器增益乘積的相反數(shù)即為對(duì)最終信號(hào)的直流偏置調(diào)節(jié)。 在此模擬電平接入處設(shè)置了一個(gè)下拉電阻R15,當(dāng)它存在時(shí),可大大減小DAC接入所造成的信號(hào)諧波失真。 選用此下拉電阻是對(duì)比測試后的結(jié)果,具體可見4.1.1 小節(jié)。

R16、R17、C4 組成了低通濾波網(wǎng)絡(luò),其傳遞函數(shù)為[9]:

由于高精度的采集系統(tǒng)對(duì)前端模擬電路的噪聲非常敏感,因此需要盡可能地降低噪聲。 除了選用極低噪聲的放大器之外,放大器周圍的電阻取值在保證環(huán)路穩(wěn)定的前提下需要盡可能小,以減少電阻熱噪聲,此外,在保證信號(hào)能夠正常通過的前提下,可盡量減小模擬帶寬,以進(jìn)一步減小噪聲。模擬帶寬主要通過調(diào)整放大器反饋電阻與RC 濾波網(wǎng)絡(luò)來實(shí)現(xiàn)。

2.2 DAC 輸出電路

DAC 選型為LTC2666-12,精度為12 bit,通過Serial Peripheral Interface(SPI)接口進(jìn)行配置,支持8 通道獨(dú)立配置、獨(dú)立輸出。 DAC 輸出電路如圖4 所示(僅畫出了一個(gè)輸出通道),其中ADA4004-4 為一款4 通道運(yùn)算放大器, 可提高模擬電平的驅(qū)動(dòng)能力,R19的設(shè)置可進(jìn)一步減小噪聲的引入。DAC 輸出電路的設(shè)計(jì)也是對(duì)比測試的結(jié)果,具體可見4.1.2 小節(jié)。

圖4 DAC 輸出電路

2.3 時(shí)鐘模塊

ADC 自身的信噪比主要被三個(gè)因素制約:量化噪聲、熱噪聲、時(shí)鐘抖動(dòng)。 對(duì)于流水線ADC,量化噪聲通常可忽略;熱噪聲主要在低頻時(shí)限制信噪比,而當(dāng)頻率升高時(shí),時(shí)鐘抖動(dòng)就成了限制ADC 信噪比的主要因素。 因此對(duì)于高速高精度的數(shù)據(jù)采集系統(tǒng)來說,時(shí)鐘的質(zhì)量尤為重要,低抖動(dòng)的時(shí)鐘信號(hào)才能保證ADC 的分辨率。 采樣時(shí)鐘抖動(dòng)對(duì)ADC 信噪比(Signal-to-Noise Ratio,SNR)的影響可用如下關(guān)系表示[10]:

其中,總的時(shí)鐘抖動(dòng)(TJitter)包含兩部分:內(nèi)部孔徑抖動(dòng)(TAperture_ADC)和外部時(shí)鐘抖動(dòng)(TJitter,Ext_Clock_Input)。 總的時(shí)鐘抖動(dòng)可用下式計(jì)算:

設(shè)計(jì)所選ADC 的內(nèi)部孔徑抖動(dòng)約為120 fs,在信號(hào)頻率為10 MHz 時(shí)信噪比典型值為70.8 dB,根據(jù)式(8)、(9)推算,外部時(shí)鐘的抖動(dòng)至少應(yīng)小于4.6 ps。由于ADC 前端還包含模擬調(diào)理電路,會(huì)額外引入一部分噪聲,為保證信噪比,需使用較高質(zhì)量的時(shí)鐘源和抖動(dòng)清除器。 設(shè)計(jì)選用了支持JESD204B、具有雙環(huán)路Phase Locked Loop(PLL)的超低抖動(dòng)合成器和抖動(dòng)清除器——LMK04821,在12 kHz ~20 MHz范圍內(nèi),抖動(dòng)的均方根值可低至88 fs。LMK04821 包含14 路可配置的差分時(shí)鐘輸出,2 片ADC 所需的采樣時(shí)鐘(500 MHz)、參考時(shí)鐘(7.812 5 MHz),F(xiàn)PGA所需的數(shù)據(jù)傳輸時(shí)鐘(250 MHz)、系統(tǒng)時(shí)鐘(250 MHz)、參考時(shí)鐘(7.812 5 MHz)共8 路時(shí)鐘均由LMK04821提供。

3 數(shù)據(jù)讀出母板設(shè)計(jì)

母板的主要功能是接收來自ADC 子板采集的數(shù)據(jù), 并將其通過PCIe 總線傳輸?shù)缴衔粰C(jī)。 FPGA是母板的核心器件, 也是整個(gè)采集卡的控制單元。FPGA 內(nèi)部的邏輯框圖如圖5 所示。

其中,Xilinx DMA/Bridge Subsystem for PCI Express(XDMA)是Xilinx 公司的一款I(lǐng)P 核[11],它實(shí)現(xiàn)了高性能、可配置的離散聚合式存儲(chǔ)器直接訪問(Direct Memory Access,DMA),并且具有PCIe 協(xié)議中物理層、數(shù)據(jù)鏈路層和事務(wù)層的邏輯功能。 此IP 提供了可選的AXI4 Memory Mapped 或者AXI4-Stream 兩種用戶接口,實(shí)現(xiàn)了與用戶邏輯的直接連接,每種接口均可提供PCIe 地址空間和Advanced eXtensible Interface(AXI)地址空間之間的高性能數(shù)據(jù)傳輸。 此外,XDMA 還提供了配置管理接口、中斷控制信號(hào)、時(shí)鐘信號(hào)(AXI_CLK)等可供用戶配置使用[12]。 AXI4-Lite 是AXI4 的簡化版,是一種簡單的、低吞吐量的內(nèi)存映射總線,主要用于內(nèi)核和外設(shè)寄存器之間的通信。 AXI4-Stream 總線不包含地址項(xiàng),因此可以允許無限制的數(shù)據(jù)突發(fā)傳輸規(guī)模,主要用于高速數(shù)據(jù)流傳輸。 XDMA 的運(yùn)用使得用戶可以通過上位機(jī)軟件進(jìn)行在線參數(shù)配置與數(shù)據(jù)上傳控制。

數(shù)據(jù)接收模塊用到了Xilinx 公司的IP 核——JESD204,用于接收ADC 通過JESD204B 發(fā)送的采集數(shù)據(jù), 此IP 包含JESD204B 協(xié)議中的物理層和鏈路層,物理層用于以比特速率接收經(jīng)過編碼的數(shù)據(jù),鏈路層負(fù)責(zé)處理鏈路的同步、建立和保持,并對(duì)數(shù)據(jù)進(jìn)行8B/10B 譯碼[13]。 緊隨其后的解碼模塊負(fù)責(zé)對(duì)數(shù)據(jù)進(jìn)行順序調(diào)整、補(bǔ)碼/原碼轉(zhuǎn)換等處理,使得處理后的數(shù)據(jù)便于重建為原始波形。 觸發(fā)判選模塊用于對(duì)采集到的信號(hào)進(jìn)行“篩選”,篩選依據(jù)為用戶配置的通道使能、觸發(fā)閾值、采集長度等參數(shù),最終將各個(gè)使能后的采集通道超過一定閾值的、一定長度的信號(hào)“篩選”出來,送入數(shù)據(jù)打包模塊,按照用戶自定義的格式進(jìn)行打包處理,數(shù)據(jù)包中可包含用戶感興趣的數(shù)據(jù)類型、通道號(hào)、時(shí)間、數(shù)據(jù)包長度等信息。 系統(tǒng)配置模塊主要負(fù)責(zé)通過SPI 接口對(duì)各個(gè)芯片進(jìn)行參數(shù)的配置,也可對(duì)JESD204B 鏈路進(jìn)行重置。 ADC 間的同步通過FPGA 分發(fā)相位對(duì)齊的ADC_SYNC 信號(hào)實(shí)現(xiàn)。

圖5 FPGA 邏輯框圖

4 采集卡測試

采集卡的測試主要包括兩大部分:偏置調(diào)節(jié)電路測試與采集卡性能測試。

4.1 偏置調(diào)節(jié)電路測試

偏置調(diào)節(jié)電路包括差分放大器反相輸入端電路與DAC 輸出電路。 傳統(tǒng)的單端轉(zhuǎn)差分電路,反相輸入端的參考平面通常為地平面,為了實(shí)現(xiàn)對(duì)信號(hào)直流偏置的調(diào)節(jié),本設(shè)計(jì)用DAC 輸出的模擬電平來代替地平面。 然而,DAC 的使用會(huì)引入額外的噪聲并且會(huì)增大信號(hào)的諧波失真。 為了盡可能減小DAC 對(duì)采集卡性能的影響,通過一系列對(duì)比測試來確定電路結(jié)構(gòu)。

4.1.1 差分放大器反相輸入端電路測試

在差分放大器反相輸入端、DAC 輸出的模擬電平接入處設(shè)置了一個(gè)下拉電阻(見圖3 中的R15),對(duì)比測試了此下拉電阻取不同阻值時(shí)采集信號(hào)的諧波失真。 測試方法為:用信號(hào)發(fā)生器產(chǎn)生一個(gè)頻率為8 MHz、幅度接近ADC 滿量程(約-0.5 dB)的正弦波輸入采集卡進(jìn)行采集,DAC 輸出模擬電平為0 V,用Fast Fourier Transform(FFT)做出采集信號(hào)的頻譜圖,并計(jì)算其諧波失真[14]。在同等條件下,僅改變下拉電阻R15 的阻值,測得相應(yīng)的諧波失真參數(shù),見表1。

表1 下拉電阻對(duì)諧波失真的影響

從對(duì)比結(jié)果來看,下拉電阻的阻值越小,信號(hào)的諧波失真性能越好。 因此,在電路結(jié)構(gòu)中保留了下拉電阻R15 的設(shè)置。 與此同時(shí),下拉電阻的存在對(duì)DAC 的驅(qū)動(dòng)能力是一個(gè)考驗(yàn)。 經(jīng)過測試,當(dāng)R15為22 Ω 時(shí),DAC 能 夠 為 放 大 器 提 供±479 mV 的 模擬電平,能夠滿足使用需求。

4.1.2 DAC 輸出電路測試

在圖4 的DAC 輸出電路中,模擬電平輸出的方式可以有三種:(1)DAC 直接輸出(R19 取0 Ω、無電壓跟隨器);(2)DAC 經(jīng)由電壓跟隨器輸出(無R19);(3)DAC 與電壓跟隨器“同時(shí)輸出”(R19 取0 Ω)。 對(duì)比測試了三種輸出方式下采集信號(hào)的信噪比。 測試方法與4.1.1 小節(jié)類似,在同等條件下,僅改變模擬電平的輸出方式,用FFT 測得相應(yīng)的信噪比參數(shù),如表2 所示。

從對(duì)比結(jié)果來看,當(dāng)模擬電平采用方式(3)輸出時(shí),有更好的信噪比。

表2 模擬電平輸出方式對(duì)信噪比的影響

4.2 采集卡性能測試

采集卡性能測試主要包含:模擬帶寬測試、噪聲測試、ADC 動(dòng)態(tài)性能測試。 測試時(shí)采集卡模擬調(diào)理電路的增益設(shè)置為1,直流偏置為0 V。

4.2.1 模擬帶寬測試

帶寬描述的是模擬前端可精確測量的頻率范圍。 帶寬定義為正弦波輸入信號(hào)的幅度衰減到原幅度的0.707 時(shí)的頻率,也稱為-3 dB 帶寬。 采集卡模擬前端帶寬的測試方法為:用信號(hào)發(fā)生器(R&S SMA100A)產(chǎn)生一個(gè)幅度為Vi(不超過ADC 滿量程1.9 Vpp)的正弦波輸入到采集卡,逐漸增加輸入信號(hào)的頻率,同時(shí)記錄每一個(gè)頻點(diǎn)下ADC 采集到的信號(hào)的幅度Vo,Vo/Vi即為模擬前端電路的增益,將其轉(zhuǎn)換為對(duì)數(shù),并取初始頻點(diǎn)的增益為0 dB,當(dāng)增益衰減到-3 dB 時(shí)輸入信號(hào)的頻率即為采集卡的模擬帶寬[15]。 作出增益與輸入信號(hào)頻率的關(guān)系曲線如圖6 所示。

圖6 增益-頻率變化曲線

模擬帶寬的實(shí)測結(jié)果為136 MHz,已能滿足眾多直流耦合的應(yīng)用場景。

4.2.2 噪聲測試

由于采集卡所測信號(hào)均為電壓信號(hào),因此所測噪聲為輸入端接地時(shí)的電壓噪聲。 由于采集卡信號(hào)輸入端有對(duì)地的端接電阻R3(見圖3),因此無需額外做接地措施。 測試方法為:將采集卡輸入端懸空, 用ADC 采集此時(shí)的波形, 對(duì)所有采樣點(diǎn)的碼值取其標(biāo)準(zhǔn)差,即為采集卡的噪聲。 具體計(jì)算公式如式(10)、(11)所示:

其中,Vi為每一個(gè)采樣點(diǎn)的碼值,為所有碼值的平均值,n為采樣點(diǎn)個(gè)數(shù),Vδ為所有采樣點(diǎn)的標(biāo)準(zhǔn)差。ADC 能識(shí)別的最小刻度表示為最低有效位(Least Significant Bit,LSB),其碼值的單位通常用LSB 表示。一共測量了122 880 個(gè)采樣點(diǎn),計(jì)算得到其標(biāo)準(zhǔn)差為2.172 LSB。 由于14 位ADC 總 共包含16 384 LSB,滿量程為1.9 Vpp, 因此2.172 LSB 對(duì)應(yīng)為0.252 mV。因此,采集卡的噪聲為0.252 mV。

4.2.3 ADC 動(dòng)態(tài)性能測試

ADC 的動(dòng)態(tài)性能參數(shù)主要包含:無偽峰動(dòng)態(tài)范圍(Spurious Free Dynamic Range,SFDR)、信噪比(Signalto-Noise Ratio,SNR)、總諧波失真(Total Harmonic Distortion,THD)、信納比(Signal-to-Noise and Distortion Ratio,SINAD)、有效位(Effective Number of Bits,ENOB)[16]。目前通常采用FFT 頻譜分析法來測試ADC 的動(dòng)態(tài)性能,它可以將ADC 采樣結(jié)果中各個(gè)頻率成分的幅度計(jì)算出來,然后依據(jù)ADC 各個(gè)動(dòng)態(tài)性能參數(shù)的定義進(jìn)行計(jì)算。

具體測試方法為:用信號(hào)發(fā)生器(R&S SMA100A)產(chǎn)生一個(gè)幅度接近ADC 滿量程的正弦波(約-1 dB),經(jīng)過對(duì)應(yīng)頻率的帶通濾波器后輸入到采集卡,將ADC 采集到的數(shù)據(jù)用FFT 進(jìn)行分析,得到各個(gè)動(dòng)態(tài)性能參數(shù)。 選取了采集卡模擬帶寬內(nèi)的9 個(gè)頻點(diǎn),選取動(dòng)態(tài)性能參數(shù)中的4 個(gè)進(jìn)行了測試,測試結(jié)果如表3 所示。 其中10 MHz 的時(shí)域波形如圖7 所示,頻譜圖如圖8 所示。

所測得的ADC 有效位接近11 bit,略低于手冊的參考值,考慮到性能測試時(shí)包含了前端模擬調(diào)理電路,因此測試結(jié)果符合預(yù)期。

表3 ADC 動(dòng)態(tài)性能參數(shù)測試結(jié)果

圖7 ADC 采集信號(hào)典型時(shí)域波形(10 MHz)

圖8 ADC 采集信號(hào)典型頻譜圖(10 MHz)

5 結(jié)論

本文設(shè)計(jì)了一種8 通道14 位500 MS/s 的數(shù)據(jù)采集卡,使用時(shí)可調(diào)整模擬調(diào)理電路以適應(yīng)不同信號(hào)特征,在其模擬調(diào)理電路增益設(shè)置為1、直流偏置為0 V 時(shí)進(jìn)行測試,ADC 動(dòng)態(tài)性能良好,有效位約為11 bit,接近芯片指標(biāo)。 對(duì)于經(jīng)過測試驗(yàn)證的ADC,后續(xù)設(shè)計(jì)可在本文所提框架不變的前提下,將其直接放在母板上,子板上僅放置模擬調(diào)理電路,根據(jù)不同的信號(hào)特征準(zhǔn)備相應(yīng)的子板即可,不需要頻繁更換電阻,使用起來更方便。 本文所設(shè)計(jì)的采集卡為標(biāo)準(zhǔn)的PXIe 模塊,通過PXIe 機(jī)箱擴(kuò)展及同步授時(shí),可進(jìn)一步構(gòu)建規(guī)模更大的多通道高精度的信號(hào)采集儀器,在實(shí)驗(yàn)物理、信號(hào)采集、通信、電子信息等領(lǐng)域有著廣泛的應(yīng)用。