一種雙網絡總線接口模塊故障實時檢測的硬件設計與實現

武堅 朱志強 馮思桐

摘要:現有的機載單總線接口模塊當網絡總線通信故障時,主機系統無法獲取模塊及交聯電路的狀態信息,模塊表面上看起來就像黑匣子一樣無法訪問,給主機系統帶來了潛在的安全隱患,因此雙網絡總線接口模塊的設計對于機載產品的故障檢測具有重要的意義。該文設計了一種基于FC(Fibre Channel,光纖通道)和CAN的雙網絡總線接口模塊,能夠有效地完成接口模塊的故障實時檢測,提升了系統的測試性和維修性。

關鍵詞:FC總線;CAN總線;故障檢測

中圖分類號:TP393? ? ? ? 文獻標識碼:A

文章編號:1009-3044(2021)07-0052-02

1 介紹

基于FPGA的嵌入式接口模塊具有靈活度高、集成性高等優點,可以支持150Mbps至6.5Gbps多種通信速率[1],實現不同的接口功能。但當硬件功能電路出現異常時,故障往往難以進行迅速定位和排查。尤其在接口模塊通信功能故障時,上層主機系統此時完全無法訪問接口模塊,無法精準定位故障位置,對于故障排查和設備維修造成了極大不便。本文提出的雙網絡總線接口模塊圍繞FPGA設計實現,采用雙路網絡總線設計,通過FC總線及CAN總線同時將產品狀態進行上報,能夠對模塊自身硬件狀態進行有效的實時檢測。模塊中雙路網絡總線的設計可以確保在FC總線或CAN總線通信失效時,上層主機仍能通過另一路總線獲取當前的狀態信息,極大提升了產品的測試性和維修性。

2 故障實時檢測機制

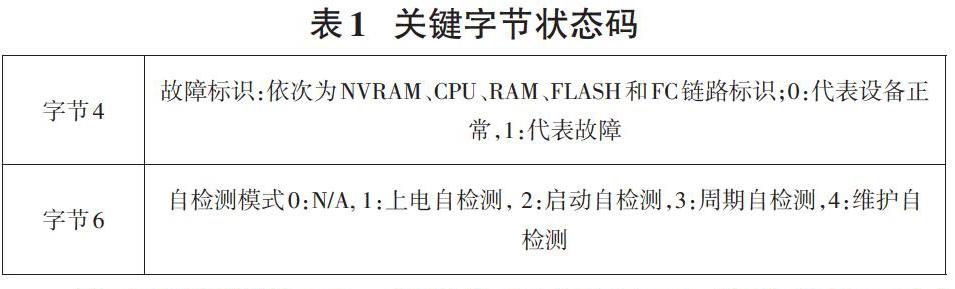

本文設計的故障實時檢測機制,檢測的主要對象為接口模塊自身硬件的狀態信息,包括FPGA內CPU的運行情況,SRAM、NVRAM和FLASH的寫讀狀態,以及FC總線的鏈路狀態信息。CPU每兩秒進行一次自檢測,檢測后在NVRAM讀寫正常的前提下將結果記錄在NVRAM中,并將表示狀態信息的8字節狀態碼,通過FC總線上報至主機后端的中央維護系統,同時通過CAN總線上報至主機前端的傳感器系統。部分關鍵字節狀態碼見表1。

接口模塊使用FPGA提供的高速串行I/O,能夠滿足FC網絡總線要求的2.125Gbps的速率要求,通過FPGA內嵌的PowerPC處理器硬核及FLASH存儲器完成維護軟件及應用處理軟件的執行,模塊的邏輯內部通過接口控制器、存儲器管理器實現對串行接口和存儲器的管理,PowerPC處理器運行Vxworks操作系統,負責完成雙路網絡總線的接口控制及初始化、中斷處理、數據轉換與組幀和傳輸管理等工作。通過串行接口實現對相關接口參數的配置,包括FC的端口ID配置,FC消息ID配置、CAN總線速率、CAN消息號等。最終軟硬件組合共同工作完成FC-ASM[2]協議處理及CAN接口通信管理,實現雙網絡總線的對外通信及故障檢測功能。

3 雙網絡總線接口硬件設計實現

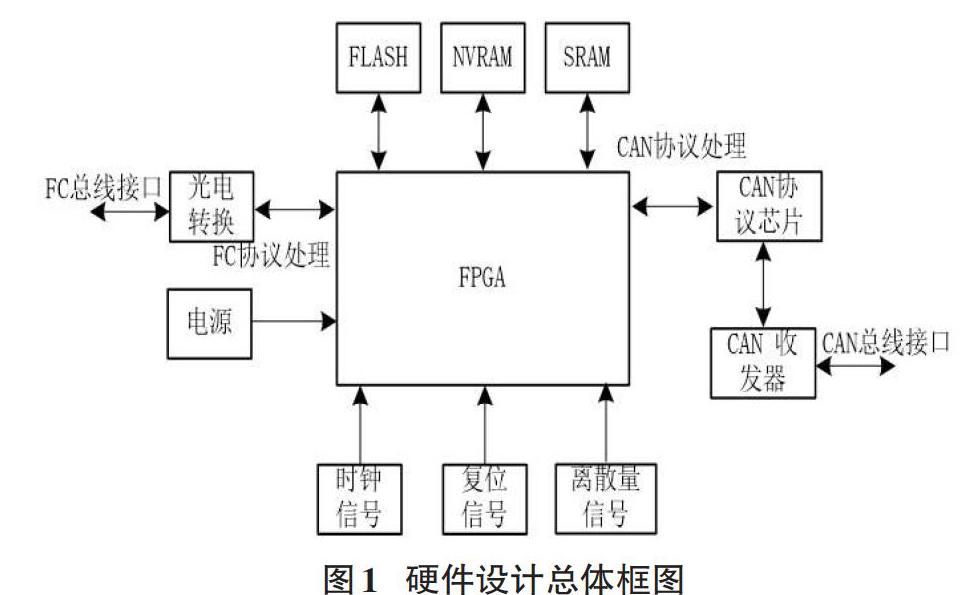

在接口模塊硬件設計中,圍繞FPGA,搭建電源、時鐘、存儲和光電轉換等功能電路,總體結構框圖見圖1。

模塊使用Master SelectMAP模式對FPGA進行配置,并對FPGA內部高速串行I/O管腳的供電進行了濾波設計,每路都增加了一個指定的電容和磁珠以確保良好的紋波特性。為了確保FC及CAN雙路總線的正常通信,產品使用40MHz、212.5MHz以及16MHz三種時鐘,分別為系統時鐘、FC工作時鐘以及CAN接口工作時鐘,由三個晶體振蕩器提供,所有晶體振蕩器布局均靠近所用芯片,并采用LC電路進行供電設計,以提高時鐘品質。在FPGA外圍搭建了存儲電路,包括SRAM等FLASH芯片存儲維護程序、應用固件等信息,NVRAM用于存儲故障信息或其他系統要求的關鍵信息,便于系統綜合過程中的故障排查。產品配置硬件離散量1個,為地面調試使能信號,用于切換模塊運行模式。該信號經過驅動器隔離后引入FPGA,PowerPC啟動對應的應用程序前讀取該信號狀態,以確定工作模式,并啟動相應的應用程序。GSE為低時,為維護測試狀態;GSE為高時,運行應用程序。FC電信號與光信號的轉換則通過光電收發器件實現,通過FPGA的高速串行接口,使用交流耦合方式,連接到光電收發器,轉換為光信號之后,通過MT接口形式引出到接口模塊外。

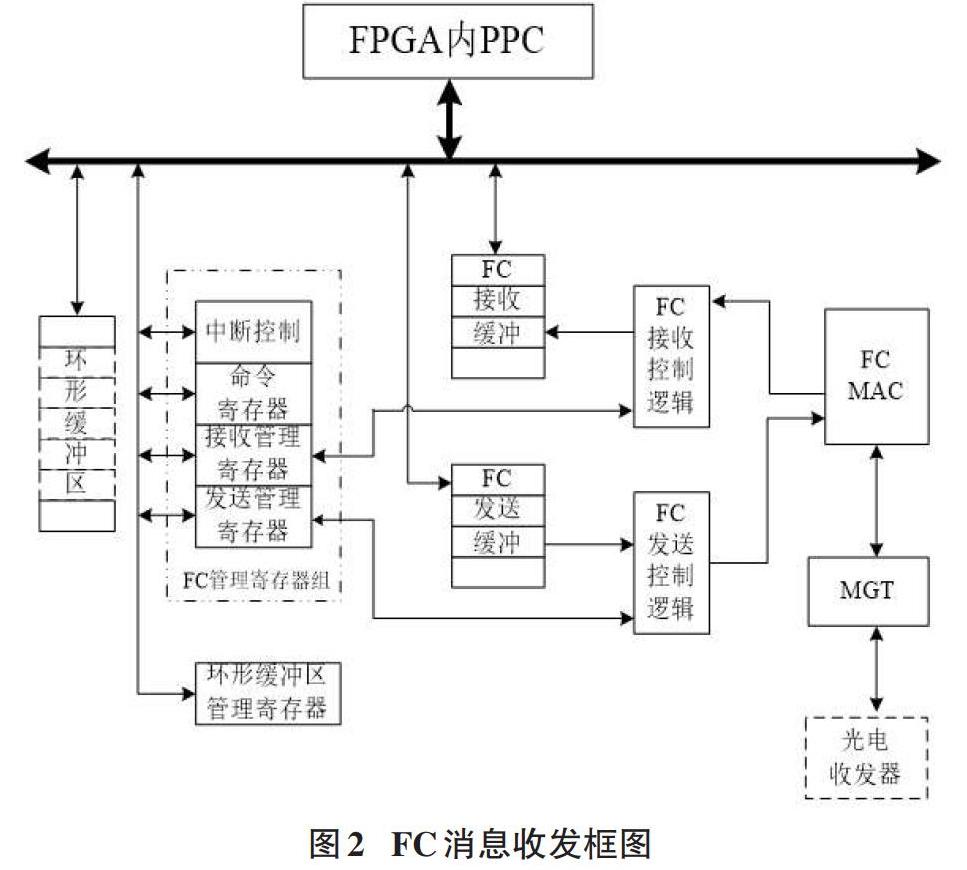

其中FC總線接口的MAC部分功能使用自研的IP核實現,支持FC-1和FC-2部分功能,支持點到點和交換結構[3],包括FC端口狀態機、可選的緩沖區到緩沖區信用管理。對上提供應用邏輯的數據收發接口,對下提供用于連接光電收發器或電連接器的高速差分信號,可提供線速的數據發送能力。基于FPGA外圍電路中MGT實現FC接口信號的串/并轉換、8B/10B編碼、時鐘恢復以及CRC校驗等工作。FC網絡總線對外通信的具體流程如圖2。

接口模塊的CAN接口用于和傳感器控制模塊之間進行數據交互,通信速率1Mbps,兼容ISO 11898標準,使用CAN協議芯片以及收發器芯片實現該接口[4],數據幀格式采用CAN2.0B標準幀格式,具備高層協議標識和數據校驗能力,并且能夠對數據進行分段傳輸。接口電路使用專用光電耦合器件進行隔離保護,在實現可靠數據通信的前提下,對電路進行有效保護,硬件設計框圖如圖3所示。

CAN總線接口通過CAN驅動器對外提供電信號,CAN協議處理單元實現對CAN報文信息的解析和封裝。CAN控制邏輯負責維護CAN總線狀態機,將報文信息發送至CAN總線,同時將從CAN總線接收到的報文信息寫入CAN的接收緩沖區,并將CAN接收中斷上報處理器。PowerPC處理器通過一系列CAN管理寄存器實現對CAN總線鏈路控制及CAN報文信息收/發管理的操作,最終實現CAN總線的對外通信及故障實時檢測。

4 結束語

本文提出了一種雙網絡總線接口模塊故障實時檢測的硬件設計和實現方法,通過圍繞FPGA搭建硬件電路,實現了FC和CAN的雙路網絡總線通信功能,能夠對模塊自身的CPU、SRAM、NVRAM、FC鏈路等硬件信息進行實時檢測和獲取,并能通過雙路網絡總線進行實時上報。對于上級主機系統而言,一旦發現故障,能夠迅速定位并進行故障排查,大大提升了系統的測試性、安全性和維修性。

參考文獻:

[1] 劉召慶,康婷颋,惠進,等.基于FPGA的FC總線通訊板的設計與驗證[J].電子設計工程,2018,26(8):97-101.

[2] INCITS TR 31-20020, Information Technology-Fibre Channel Avionics Environment-Anonymous Subscriber Messaging (FC-AE-ASM)[S].2008.

[3] 武華,石海洋,楊媛媛.CAN與光纖通道網關的設計與實現[J].電腦知識與技術,2015,11(12):49-51.

[4] 馮源,豆海利,閆海明.基于CPLD的DSP與CAN控制器的接口設計與實現[J].現代電子技術,2015,38(8):66-69.

【通聯編輯:代影】