寄生電容自適應抑制的飛法級電容傳感器讀出電路

李致銘,蘭哲沖,金楷越,張杰,張鴻

(西安交通大學微電子學院,710049,西安)

電容傳感器具有高靈敏度和易于集成的優勢,廣泛應用在觸摸屏、加速度計、指紋識別及聲音識別等領域。物聯網和可穿戴設備等應用系統對電容傳感器集成度要求推動傳感器工藝尺寸不斷縮減至微米(10-6m)量級,這使得傳感器的電容變化量隨著工藝尺寸縮減至飛法(10-15F)量級。傳感器應用環境中的鍵合線、焊盤、印制電路板(PCB)與靜電防護器件帶來的寄生電容通常達到皮法(10-12F)量級。在此情況下,大寄生電容上產生的寄生電荷可以輕易干擾甚至吞沒傳感器電容上的信號電荷,從而嚴重限制了電容傳感器讀出電路的信號處理范圍和精度[1-6]。

傳統的電容傳感器讀出電路通常采用周期調制方式[7]或雙斜坡變換方式[8-9]。前者將傳感器的電容變化量轉換為方波信號周期的變化量,再用時間數字轉換器(TDC)得到數字輸出;后者通過積分實現電容-電壓(C-V)轉換,再通過模數轉換器(ADC)得到數字輸出。這兩種方案都需要在片上集成額外的固定電容來抵消寄生電容的影響,難以適應不同應用場景寄生電容可能出現較大變化的情況。為了在不同寄生電容情況下實現精確的電容測量,文獻[10]采用了可變的參考電容CREF陣列,并用ADC的輸出結果反饋選擇不同大小CREF來適應寄生電容的變化。這種方案本質上也是采用自動增益控制的思想,但其整體結構的反饋必然大大降低讀出電路的轉換速度。

本文提出了一種基于開關電容C-V轉換且帶有自動增益控制的全差分電容傳感器讀出電路。通過設置合理的開關頻率,開關電容C-V轉換電路可以實現比傳統方案更寬的電容測量范圍,而全差分結構能抑制寄生電容對電容測量的影響。電路中設帶有3位ADC的自動增益控制放大器,以自適應地調整不同寄生情況下有用信號的放大倍數,提高整個讀出電路的動態范圍。放大器的輸出由一個帶動態元件匹配(DEM)的12位逐次逼近(SAR)ADC量化。為了抑制噪聲的影響,在數字后端采用了對多次轉換結果進行平均的降噪方法。所提出的讀出電路在2~10 pF的寄生電容下,能夠實現1 fF的測量精度,單次測量時間為1.2 ms,總功耗為1.8 mW。

1 讀出電路結構和原理

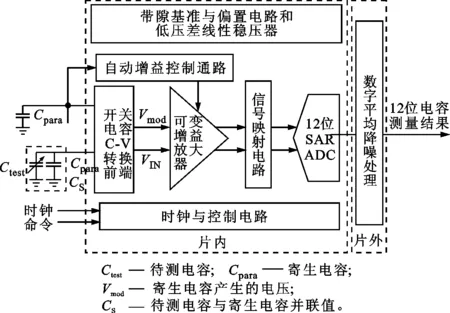

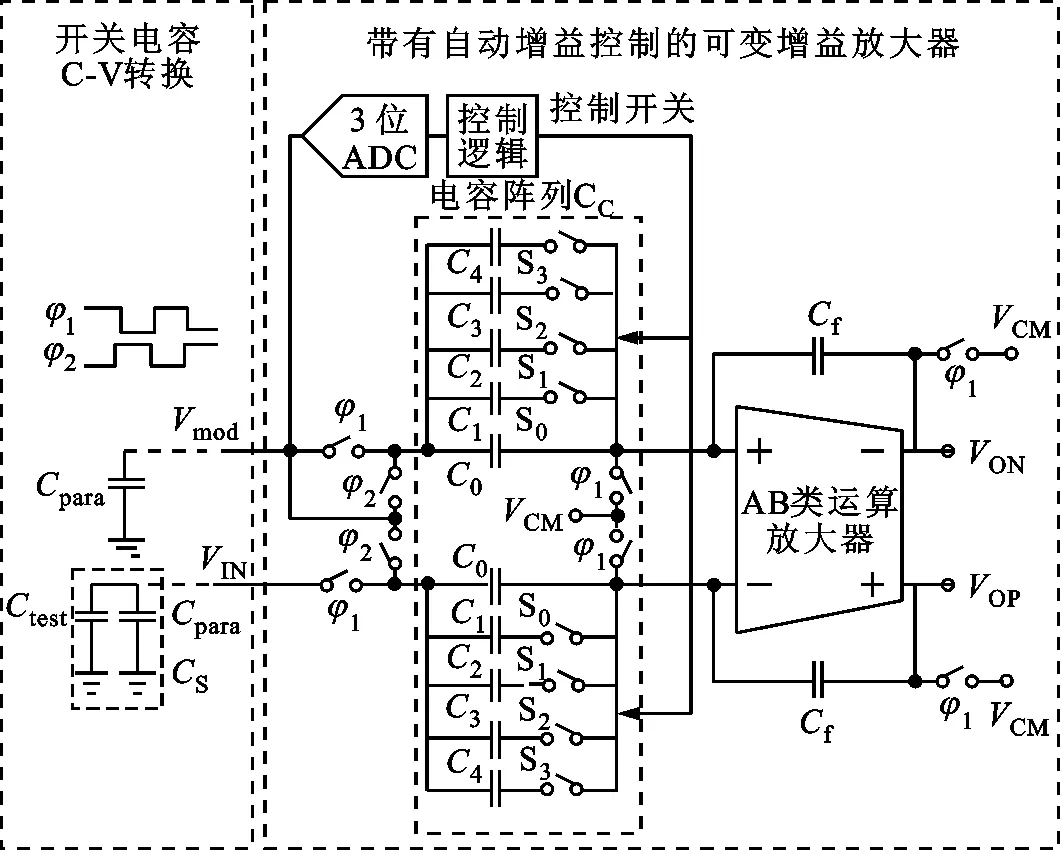

本文提出的飛法級電容傳感器讀出電路主要包括開關電容C-V轉換前端、帶自動增益控制的放大器、SAR ADC等模塊,其整體電路拓撲結構如圖1所示。由圖可見,電路中包含兩路相同的C-V轉換電路,其中一路接電容傳感器,另一路空置。通過匹配性設計保證兩路具有相同的結構,從而具有相同的寄生電容。兩個C-V轉換電路將寄生電容與傳感器電容一起轉換成電壓信號,再通過全差分的可變增益放大器將兩路的差值電壓放大。在兩路完全匹配的情況下,這種結構可實現寄生電容的完全抑制。實際情況下,即使兩路存在其他環境因素帶來的失配,也可以通過兩步測量法輕易地消除寄生電容的影響。在該結構中,若應用場景使寄生電容發生變化,則C-V輸出的有用電壓與總電壓的比值將發生大的變化。若采用固定的放大倍數,則難以適應大的寄生電容變化范圍。為了解決該問題,本文利用3位的SAR ADC對參考通路的電壓進行量化,利用量化結果選擇放大器的檔位,以合理的倍數對信號進行放大,從而自動適應寄生電容的變化。可變增益放大器的輸出由12位的SAR ADC進行量化。一次測量中進行多次采樣和量化,并對結果取平均值,從而顯著降低電路和環境中噪聲的影響。

圖1 整體電路拓撲結構Fig.1 System architecture

1.1 前端開關電容C-V轉換電路

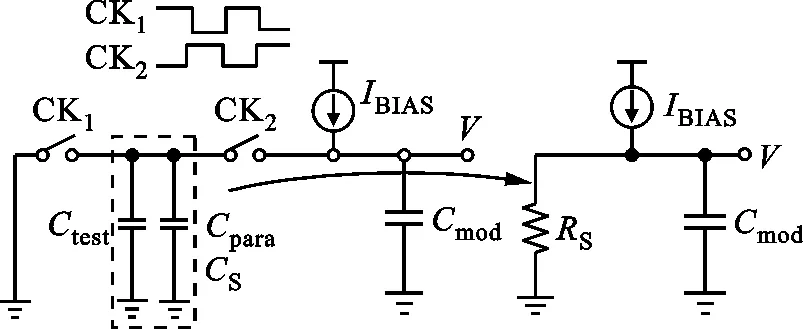

本文的C-V轉換電路基于開關電容周期性充放電可等效為電阻的基本原理來實現[11]。將一個一定值的參考電流IBIAS流入開關電容結構,即可將電容轉換為電壓,C-V轉換電路前端基本原理如圖2所示。

圖2 C-V轉換電路前端基本原理圖Fig.2 Schematic of frontend C-V converter

可以證明,當周期為fS的兩相不交疊時鐘CK1和CK2控制電流IBIAS對寄生電容Cpara與待測電容Ctest之和CS進行充電和放電時,其平均電荷消耗與時間的關系可以用一個電阻RS來等效

(1)

整個結構的平均輸出電壓可以表示為

(2)

式(2)表明,等效電阻與電容和控制時鐘的頻率積成反比。可以用一個高精度的電流對該開關電容結構進行充電,通過產生的電壓大小,對待測電容和寄生電容之和進行測量轉換。本文中,電流源采用片上的基準電路實現[12]。同時為了穩定轉出的電壓,需要一個片外的大電容Cmod來濾除紋波。

式(1)還表明該電路具有可配置性強的特點,通過適當改變時鐘的頻率以及電流源的大小,即可用于具有不同總電容的應用場景,使輸出電壓保持在后續電路能處理的合理范圍。

1.2 全差分寄生電容抑制電路

在寄生電容較大的應用場景中,待測電容Ctest的值相對于Cpara過小,Ctest引起的電壓變化僅是疊加在寄生電容產生的電壓Vmod上的一個微小電壓。以典型電路參數為例,若寄生電容為10 pF,時鐘頻率為20 MHz,IBIAS為40 μA,則可算出僅寄生電容輸出的電壓為0.2 V。被測電容1 fF的輸出電壓變化僅約為20微伏(10-5V)量級,也就是說有用的電容信號完全淹沒在寄生電容產生的電壓中。如果直接測量,在1.8 V的供電下,需要ADC位數達到20位以上才能分辨1 fF電容的電壓變化,這大大增加了ADC的設計難度和整體電路開銷。為了解決這一問題,通常的做法是對信號進行放大。然而,不同的應用環境寄生電容可能產生較大的變化。例如,基于上述例子的參數,寄生電容2~10 pF的變化對應直流電壓Vmod的變化范圍為0.2~1.0 V。若直接對信號進行放大,必然受到電源電壓的限制。如果降低IBIAS或增大fS,又會嚴重衰減信號。因此,如何消除寄生電容引起的直流電壓的影響是飛法級高精度電容傳感器讀出電路設計的難點。

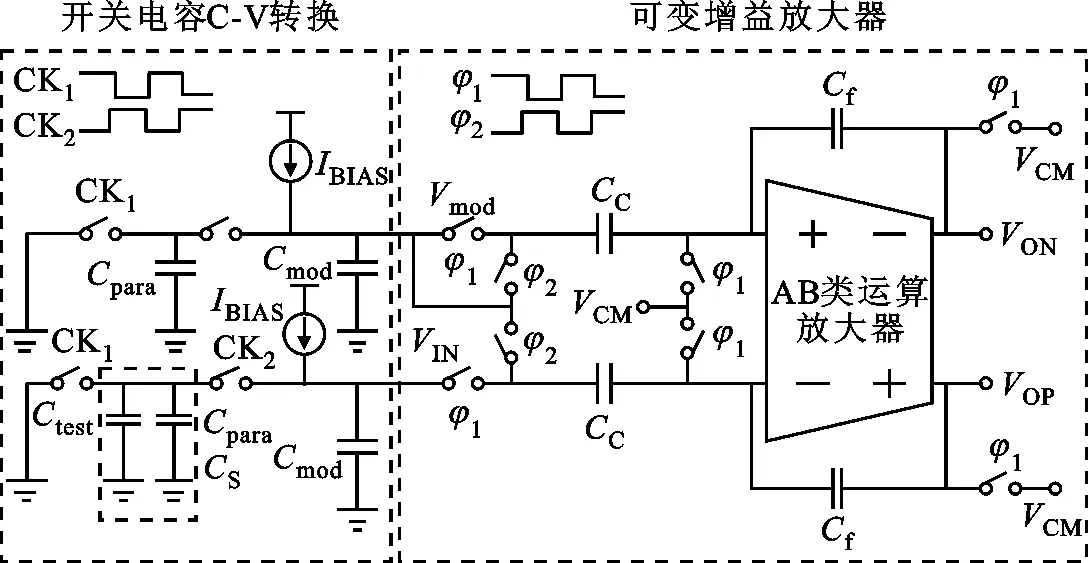

圖3 全差分放大結構Fig.3 Fully differential amplifier circuit

針對這一問題,本文提出了如圖3所示的全差分放大結構處理C-V轉換得到的差值放大信號,并且通過開關電容運算來抵消寄生電容產生的共模電壓。圖中的VIN為主通路寄生電容與待測電容產生的電壓;VCM為運放的共模電壓;VOP和VON分別為運放的正負輸出電壓;φ1與φ2為可變增益放大器的控制時鐘;CC與Cf分別為輸入電容與反饋電容。本設計設置了一路完全對稱的空載通路作為對照,其寄生電容與主通路一致。相同條件下空載通道充電產生的電壓即等于主通道的寄生電容產生的直流電壓。這一對電壓由全差分可變增益放大器處理后,輸出的差值就是放大后的傳感器電壓。如圖3所示,在φ1為高的相位,VIN與Vmod對CC進行充電,運放正負輸入端的電容積累的總電荷分別為

QP1=(Vmod-VCM)CC

(3)

QN1=(VIN+Vmod-VCM)CC

(4)

在φ2為高的相位,電容陣列CC的左極板復位為Vmod。電荷分享完成后,運放輸入節點虛短,且電壓為VX,可得運放輸入節點電荷為

QP2=(Vmod-VX)CC+(VX-VON)Cf

(5)

QN2=(Vmod-VX)CC+(VX-VOP)Cf

(6)

由電荷守恒即QP1=QP2,QN1=QN2,可得到輸出電壓與傳感器對應的輸入電壓的比值為

(7)

由上述推導可以看出,寄生電容產生的電壓Vmod被完全消除了,同時放大增益由CC與Cf的比值確定,可以設計得很準確。本設計中,近40倍的增益就能夠將20微伏(10-5V)量級的信號放大到0.5 mV以上,因此后端用一個12位的SAR ADC即可進行量化。

該設計的優勢在于可以通過差分運算消除寄生電容的影響,從而大大提升讀出電路對寄生電容的容忍能力,同時有效利用較低的工作電壓范圍。另外,全差分結構設計相對于單端C-V電路,能更好地抑制其他共模干擾。

1.3 自動增益控制

雖然上述的全差分電路能夠消除寄生電容產生的共模電壓,但是不同寄生電容條件下有用信號VIN的值與寄生電容Cpara有關

(8)

由式(8)可以看出,當寄生電容較大的時候,電容變化引起的電壓變化更小,因此對不同寄生電容情況下,增益的處理是不同的。本文設計了一個自動增益控制方案,通過檢測Vmod的大小來選擇放大器的放大倍數,從而能在寄生電容不同的情況下,自適應地將傳感器電壓放大到合適的輸出范圍。為了能自適應地選取增益檔位,本文采用如圖4所示的自動增益控制電路實現檔位自適應控制,該支路包括一個簡單的3位ADC與相應的譯碼電路。圖中的CC由電容陣列C0~C4實現,并由開關S0~S3進行控制。

圖4 自動增益控制的實現電路Fig.4 Automatic gain control circuit

考慮到功耗和轉換速度的要求,3位ADC選擇SAR ADC結構來實現。由分析可知,寄生電容在2~10 pF時,前端檢測電路輸出的直流電壓范圍為0.2~1.0 V,該SAR ADC在面對0.2~1.0 V的輸入信號時可以產生8個碼值的變化。通過這8個不同的量化碼值則可以設置5個調節增益檔位,可覆蓋2~10 pF寄生電容范圍內1 fF~1 pF電容的測量需求。

上述方案以較小的面積和功耗實現了自適應增益控制,并且由于是開環結構,相對于文獻[10]具有測量時間短的優勢。

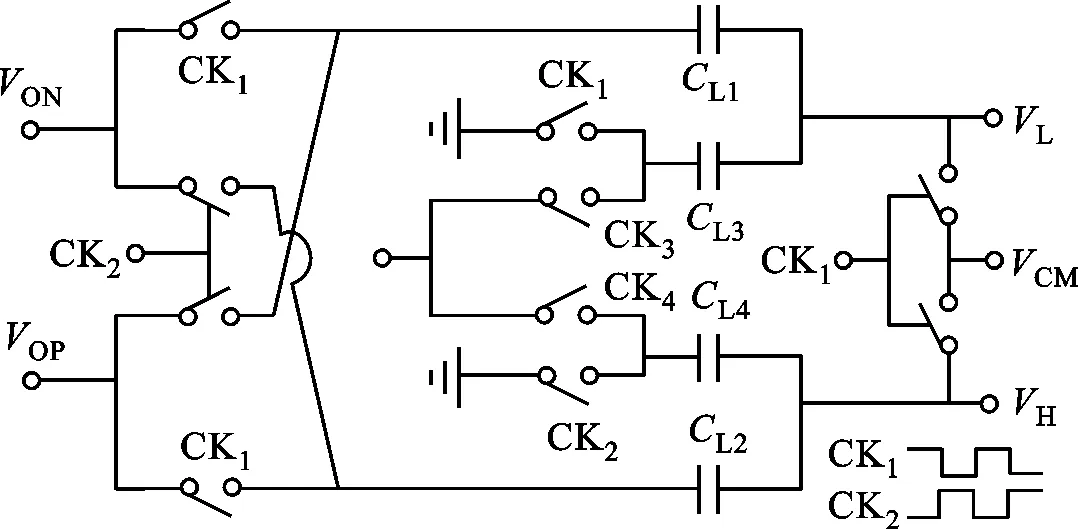

1.4 信號范圍映射電路

通過前面的推導,由式(7)可知該前端輸出的信號始終有VON大于VOP,為了有效利用全差分ADC的動態范圍,并且降低對ADC的性能要求,本文設計了一個信號映射電路[13],將VON-VOP變為雙極性信號,從而有效利用ADC的轉換范圍。信號映射電路的結構如圖5所示。

圖5 信號映射電路的結構Fig.5 Signal mapping circuit

可以看出,VOP和VON通過4個開關在不交疊時鐘信號的控制下傳遞到CL1和CL2的左極板。在CK1和CK2兩個相位,CL1和CL3以及CL2和CL4保持電荷守恒。因此,如果CL1~CL4具有相等的值,則可以得出CK2時的差分和共模輸出分別為

(9)

為了讓VON與VOP在轉換過程中保持穩定,信號映射電路的時鐘CK1與CK2的頻率快于可變增益放大器的工作頻率,在φ2為高的相位實現信號映射。ADC在CK2相位對信號進行采樣和量化,即可得到電容測量結果。

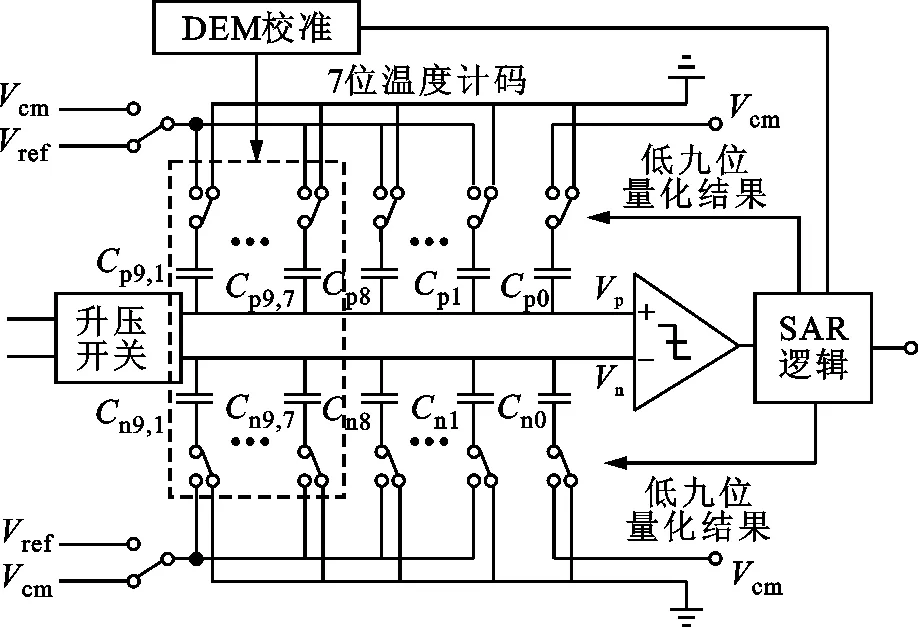

1.5 基于DEM校準算法的12位SAR ADC

為了降低功耗并縮短轉換時間,本文選擇SAR ADC來對前端的輸出電壓進行模數轉換。ADC的設計精度為12位,采樣時鐘為200 kHz。

為了盡可能地降低ADC中電容陣列失配產生的誤差,本文采用了DEM校準的技術對電容失配進行補償。該結構將傳統的3位二進制權重電容陣列轉化成如圖6所示的7位溫度計編碼的單位電容陣列,并用基于交換原則的DEM校正算法來選擇相應的電容[14-15]。采用DEM算法可提高ADC的無失真動態范圍(SFDR),進而提高ADC的有效精度。

圖6 DEM的電容映射示意圖Fig.6 Capacitor mapping diagram of the DEM method

整個SAR ADC的基本電路結構如圖7所示,數模轉換器(DAC)陣列采用電容復用的切換策略[16-17],這種切換策略能復用電容陣列,從而使總電容減小一半。采樣開關采用柵壓自舉開關,以提高SAR ADC的線性度和信噪比。

圖7 本設計SAR ADC基本電路結構圖Fig.7 SAR ADC structure in the proposed circuit

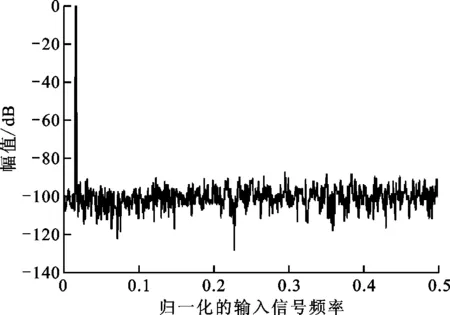

在輸入信號為3.3 kHz的正弦輸入信號的條件下,ADC輸出的動態頻譜圖如圖8所示,從頻譜圖可以計算得到,ADC的信噪失真比(SNDR)為70.82 dB,SFDR為87.55 dB,有效位數ENOB為11.47位。

圖8 輸入信號為3.3 kHz、采樣頻率為200 kHz時 ADC的動態頻譜 Fig.8 ADC output spectrum for 3.3 kHz sinusoid input signal at 200 kHz sampling rate

2 噪聲分析

所設計的讀出電路的等效輸入噪聲主要由前端電路的KT/C噪聲、運放噪聲以及ADC產生的量化噪聲3部分組成,總噪聲的表達式如下

(10)

其中ADC的噪聲由可變增益放大器的放大倍數進行抑制。在傳感器寄生電容為2 pF時,提供增益的電容(CC)大小為32 pF,對于開關電容結構,kT/C噪聲均方電壓為11.4 μV。

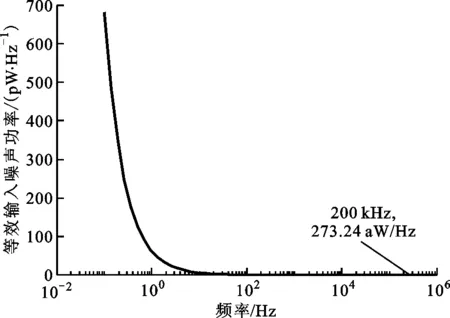

運算放大器的等效輸入噪聲頻譜仿真結果如圖9所示。噪聲在200 kHz處為273.24 aW/Hz(假設以1 Ω電阻為負載),對測量的影響非常小。ADC的噪聲經過可變增益放大器放大倍數的抑制,可以忽略不記。

圖9 等效輸入噪聲頻譜仿真結果Fig.9 Input-referred noise spectrum

相對于Sigma-Delta ADC過采樣方案,SAR ADC的缺點在于容易受到噪聲以及采樣時刻各種干擾的影響。為了進一步消除噪聲以及其他干擾對測量精度的影響,本文在片外采取多次測量求平均值的方法,能夠顯著地降低噪聲和干擾的影響。

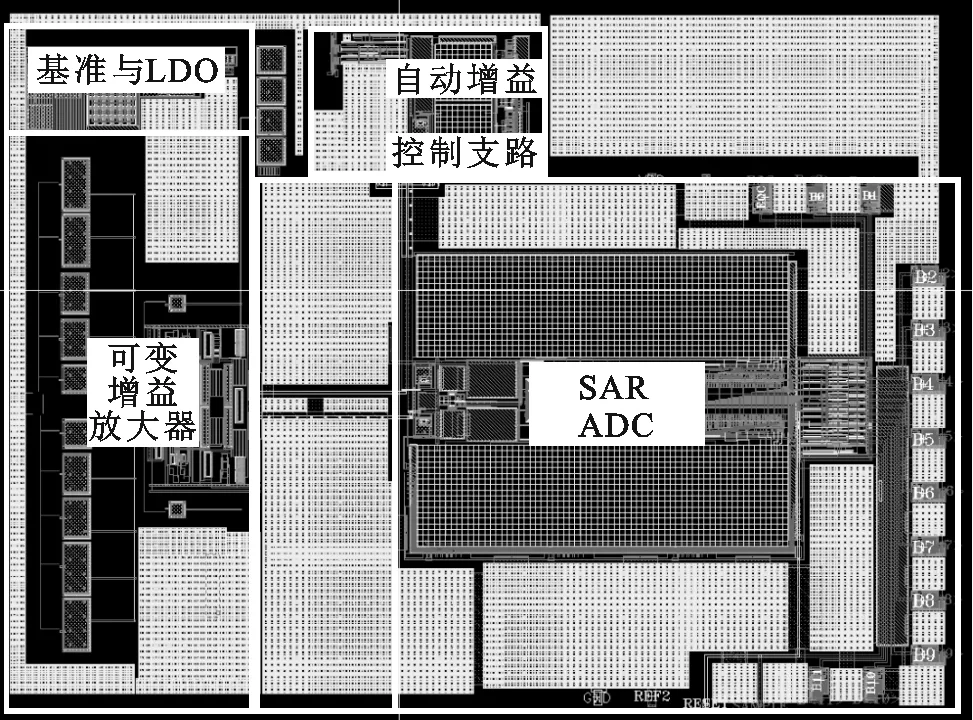

圖10 整體版圖結構Fig.10 Layout structure

3 仿真結果

本文的讀出電路采用0.18 μm CMOS工藝設計,整體版圖結構如圖10所示,核心電路面積為1.2 mm×0.89 mm。整個電路采用3.3 V供電,內部各模塊的電壓由片上的基準與片上電源供電,整體功耗仿真結果為1.8 mW,測量時間為1.2 ms。若定義轉換能量為功耗與測量時間的乘積,可以算出本設計轉換能量為2.16 μJ。

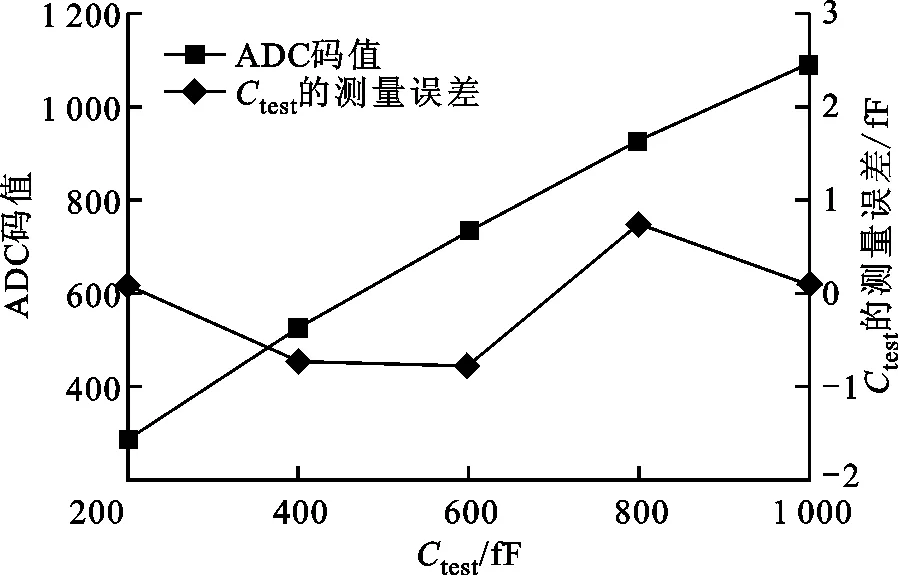

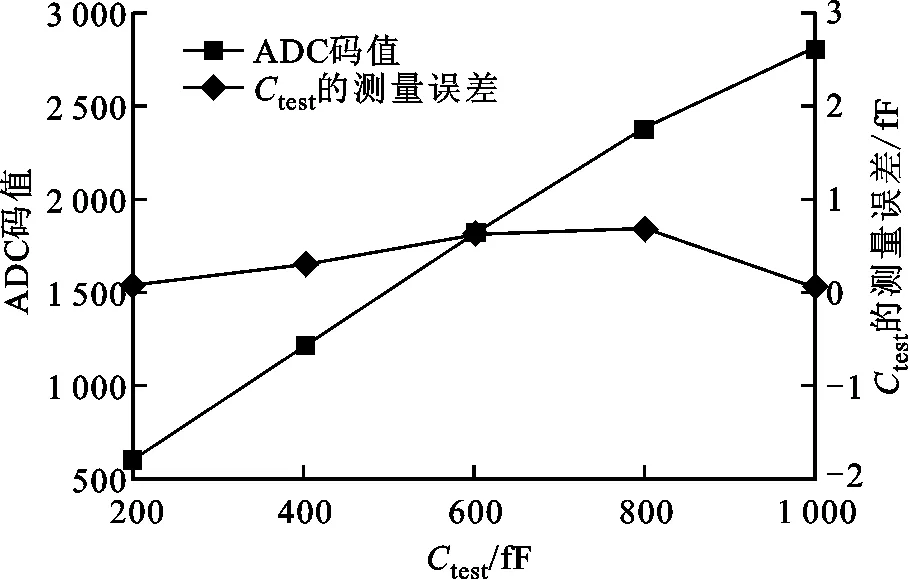

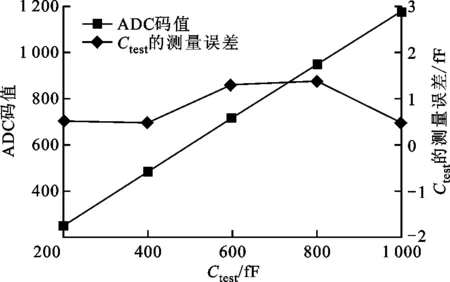

由前文可知,整體電路對電容的量化表達式為

(11)

式中:Cout為量化結果,G為整個系統的增益。對應的測量曲線經過處理如圖11所示。Cpara值較大時,可看出測量曲線的線性度更好,Cpara值較小時則線性度差,這是因為測量曲線在Cpara值較小時,近似關系不夠理想,但是這一問題對測量并沒有造成影響。通過擬合曲線對測量結果進行誤差標定可以得到如圖11的結果,可以看出本文所提出的結構測量精度小于1 fF。

(a)Cpara為2 pF

(b)Cpara為5 pF

(c)Cpara為10 pF圖11 電容測量曲線Fig.11 Capacitance measurement curves

為了與國際同類電容測量電路的性能進行對比,電容測量電路的信噪失真比定義為

(12)

式中:輸入范圍為DR,測量精度為A。品質因數為

(13)

式中WT為轉換能量。計算出整體SNDR為70.05 dB,品質因數為842.182 pJ·步-1。表1中列出了本文設計的讀出電路與其他文獻的性能對比,可以看出本設計的測量時間較短,測量精度和能容忍的最大寄生電容也有一定的優勢。

表1 電容數字轉換電路性能對比表

4 結 論

本文提出了一種能自適應抑制寄生電容的飛法級電容傳感器讀出電路,其電容-電壓轉換基于開關電容電路實現,從而可通過設置合理的時鐘頻率增大電容檢測范圍。電路采用帶3位自動增益控制的全差分放大器放大傳感器信號,同時自適應地抑制大寄生電容產生的電壓的影響。與現有文獻相比,本文的電路消除寄生電容的代價較小,而且具有很強的適應性,在大寄生、高精度電容測量和傳感器模數轉換領域有較好的應用前景。