基于FPGA的六維并聯機構的數據采集系統設計

孫嘉霖,李艷輝,霍 琦,李 昂

(中國科學院長春光學精密機械與物理研究所,長春 130033)

0 引言

在大口徑空間光學望遠鏡中,由于加工中存在誤差,環境因素導致的材料形變,都會對望遠鏡的成像效果產生影響,無法達到預期的成像要求[1]。因此,為了滿足高精度望遠鏡位姿調整的六維并聯機構就應運而生,而位姿的調整需要接收6組編碼器數值。

傳統的系統設計將現場可編程邏輯門陣列(Field Programmable Gate Array,FPGA)與編碼器端直接連接,通過BISS-C協議能夠正確地接受單個編碼器的數據來進行電機控制[2]。但在實際的運動控制的應用條件下,單個編碼器的數據不足以反映整個運動控制系統的運動狀態。因此,需要并行采集多個編碼器的數據來滿足對精密機械的控制[3]。而對于多路編碼器的數據采集,趙洪深等[4]采用FPGA和多路選擇器進行組合來進行數據采集的,但由于多路選擇器的使用,喪失了編碼器數據接收的實時性,無法滿足電機控制過程中編碼器數據實時性的要求。張立等[5]使用FPGA對多路數據進行并行采集,并用單片機進行數據處理和傳輸的,但針對于六足平臺的控制來講,FPGA編程的靈活性更強,更適合用來進行運動控制程序的設計開發及驗證。而如果只用一片FPGA芯片進行多組編碼器數據的并行處理,不僅占用了大量IO端口,增加了主控FPGA的運算量,而且由于時序信號(MA)與數據信號(SLO)差分處理,控制端與六維并聯機構間連接線纜數量為24根,線纜數量較多,給整個運動控制系統增加了負擔[6]。

基于上述原因,本文設計的系統由2片FPGA來進行實現,編碼器端FPGA負責六維并聯機構支腿上的編碼器數據采集,將采集到的6組編碼器數據整合后,等待控制端的時序信號MA來到時,將實時更新整合的編碼器數據發送到控制端FPGA處。如此設計該系統后,軟件方面上減少了六維并聯機構運動控制端FPGA的運算處理量,使得運動控制單元能夠提供更多的運算處理單元,提供給控制算法,留給控制算法更大的空間來進行優化處理運動過程中的問題。硬件方面上,減少了控制端與六維并聯平臺間連接線數量,由原來的24根線纜減少為4根,同時也減少了占用的控制端FPGA的端口。最后通過實物驗證實驗,驗證了編碼器端FPGA能夠正確接收6組編碼器數據,并進行校驗,控制端FPGA能夠接收并解算出6組編碼器數據,數據傳輸過程穩定可靠。

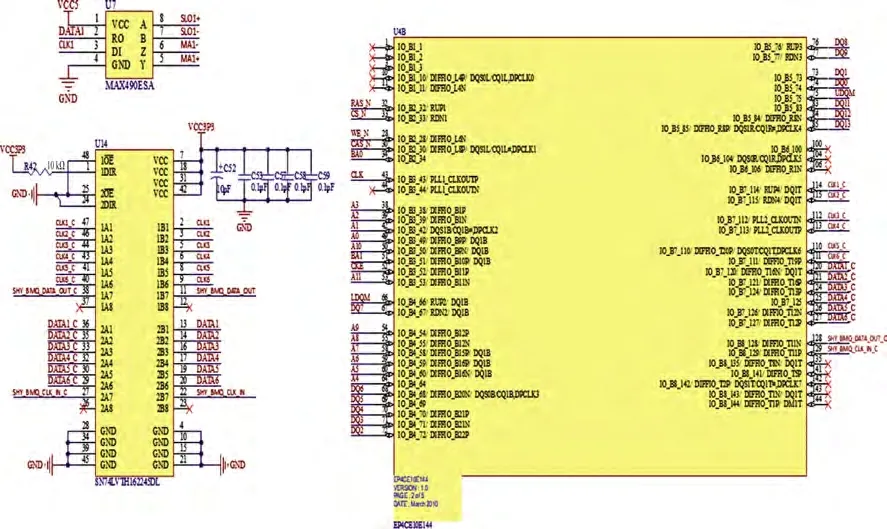

圖1 FPGA硬件電路原理Figure1 FPGA hardwarecircuit schematic diagram

1 硬件電路設計

該數據傳送系統的硬件分為編碼器端FPGA和控制端FPGA兩部分組成。

首先介紹編碼器端FPGA硬件電路的設計,硬件原理如圖1所示,以其中一個編碼器數據接收為例,編碼器數據直接接收端接收編碼器發出的時序MA的差分信號(MA1+和MA1-)并接收數據SLO差分信號(SLO1+和SLO1-),4條信號線通過MAX490EAS將差分信號SLO與MA轉化為單端信號DATA1與CLK1。該單端信號通過具有三態輸出的3.3 V-ABT-16位總線收發器SN74LVTH162245DL,將單端信號DATA1與CLK1轉化為可直接連接芯片引腳的DATA1_C與CLK1_C,來進行編碼器數據的收發,該部分芯片采用的是Altera公司的EP4CE10E22C8N。

編碼器數據間接接收端為進行試驗驗證,采用的是SPARTAN-6系列的開發板替代了六足平臺的控制電箱,FPGA芯片型號為XC6SLX45。

2 數據收發原理及FPGA軟件設計

2.1 CRC校驗的基本原理及計算

CRC檢驗的基本原理就是通過在正常的二進制k位數據后面,通過固定的運算關系,生成一個r位的校驗位,構成一個n=k+r位的數據,通過在接收端檢測接收到的數據關系,來判斷在傳輸數據的過程中,是否發生錯誤[7]。CRC校驗的基本原理可以用下式來表明:式 中: M=xTu(x),u(x)=un-l-1xn-l-1+…+u1x+u0;r=n-k;R=vr-1xr-1+…+v1x+v0;g(x)=gn-kxn-k+gn-k-1xn-k-1+…+g1x+g0。

M(Message)為傳輸信息部分的多項式,R(Remainder)為校驗部分的多項式,r為檢驗部分的位數,k為信息字段的位數,G為約定生成的多項式。對于發送端來說,通過需要傳輸的信息M和確定的G,可以生成對應信息M的一個校驗字段R。將R附加在M后面構成新的多項式V=Mxr+R,將新的多項式V發送到接收端。對于接收端來說,將接收到的V與G用模二除法進行運算,余數為0,則表示傳輸信息正確。

2.2 FPGA軟件流程設計

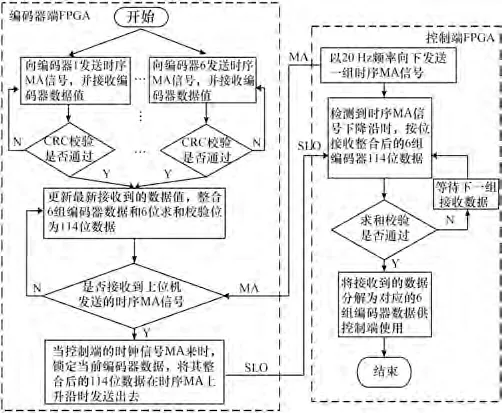

編碼器數據采集系統軟件流程如圖2所示。

圖2 編碼器數據采集系統軟件流程Figure2 Flow chart of system software of encoder data acquisition system

首先,編碼器端FPGA接收6組編碼器,并進行CRC校驗,校驗成功后,編碼器端FPGA對6組編碼器數據進行整合,6只光電編碼器軟件處理后得到各自18位數據,其中,前15位為有效二進制數位(高位在前,低位在后),后3位為該編碼器當前時刻狀態值(可以用此值判斷當前編碼器狀態是否異常)。這樣,每一數據包包含6只光電編碼器108位數據,編碼器端FPGA將從108位數據最高位起,每6位為一段,通過這個樣的方式獲取18段6位數據,將18段數據累加求和,最后以累加和的6位數據作為求和校驗位,高位在前,低位在后。當接收到控制端FPGA發送的時序MA信號時,送出這108位數據和6位的求和校驗位。

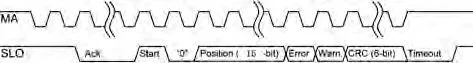

2.3 編碼器接收數據時序圖

編碼器端的FPGA與編碼器間的通信是采用Biss C模式的通信協議對6只編碼器的數據進行采集。6只編碼器的MA發送及SLO接收都是由一片FPGA進行控制,接收到編碼器數據后,對數據進行CRC校驗,檢驗通過后更新當前編碼器的返回值。各個編碼器的接收數據時序圖如圖3所示。

圖3 編碼器接收數據時序圖Figure3 Encoder receives thedata timesequencediagram

在MA沒來到的時候,SLO一直處于高電平狀態,完成確認周期Ack后,會進入高電平Star位和“0”位并傳輸數據,數據傳輸完畢后,SLO會進入低電平超時周期Timeout,編碼器準備好進行下一個周期的數據傳輸時,SLO會置為高電平來提示FPGA端接口[8]。

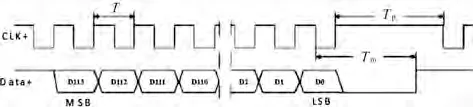

控制端FPGA讀取數據采用SSI串行的方式進行數據輸入,時序圖如圖4所示。

圖4 控制器讀取數據時序圖Figure4 Thecontroller reads thedatasequencediagram

當時序的上升沿到來時,編碼器端FPGA開始發送整合后114位數據,其中Tm為低電平持續時間,約30μs,Tp為時鐘持續高電平,這里Tp≥Tm。在每次SSI通訊完畢后,首先對接收到的數據進行校驗位校驗,如果校驗通過,則將該組數據保留用以六足平臺的控制,否則舍棄該組數據,等待下一組數據的到來[9]。

3 實驗結果及分析

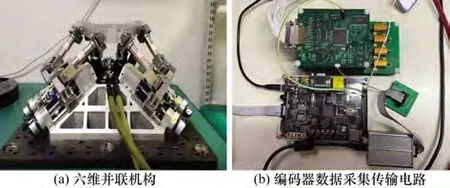

該編碼器數據采集系統將應用于六維并聯機構上采集編碼器數據,六維并聯機構及2塊FPGA編碼器數據采集傳輸板如圖5所示。

圖5 六維并聯機構與編碼器數據采集傳輸電路Figure5 Six-dimensional Parallel platform and encoder data collection transmission circuit

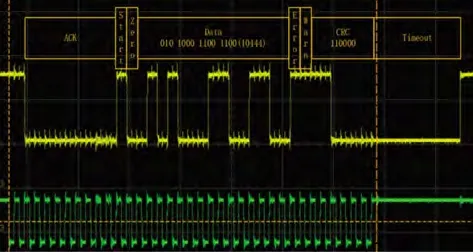

采集單個編碼器數據的數據傳輸過程如圖6所示,當編碼器接收到時序信號MA時,會按照圖2所示時序向編碼器直接接收端通過SLO發送相應編碼器數據,所傳輸的數據用二進制表示為“010 1000 1100 1100”,轉化為十進制表示為10444。編碼器端CRC校驗采用的校驗多項式為x6+x1+x0,生成的校驗碼為“110000”。

圖6 編碼器1數據接收波形Figure6 Encoder 1 datareceive waveform

圖7所示為兩個FPGA之間的數據傳輸過程。當接受到控制端FPGA發送的時序信號MA時,采集端FPGA會將整合好的114位數據通過數據SLO發送出去。由于示波器屏幕顯示限制,將該信號用ChipScope進行抓取分析,如圖8所示,傳輸的114位數據信號以十六進制顯示為“7944DBB766B3BF0F39108E”。

圖7 SSI協議傳輸過程示波器采集信號Figure7 SSIprotocol transfer processoscilloscopecollection signal

圖8 控制端接收數據過程波形Figure8 Control end receivesthedataprocess waveform

圖9所示為通過Quartus中的Signal Tap和ISE的Chip Scope來抓取到的數據傳輸過程中的信號。由圖可知,控制端FPGA可以正確的接收到由6組編碼器數據整合后的114位數據,并以編碼器1為例,對數據進行解算,接收到的編碼器數據與傳送前的編碼器數據碼值一致,均為10444。

圖9 SSI協議發送端與接收端數據對比Figure9 SSIprotocol sendingend and receiving end datacontrast

4 結束語

經過實物實驗驗證,編碼器數據采集端FPGA通過BISSC協議,并經過CRC校驗,能夠正確地采集6組編碼器的當前碼值,通過對采集到的編碼器數據進行整合,控制端FPGA通過SSI協議與求和校驗,能夠正確解算出所傳輸過來的編碼器數據。該方案能夠很好地解決直接接收的多編碼器數據方案中傳輸線纜過多,占用FPGA端口過多與單獨FPGA處理6組編碼器數據運算量大的問題。實驗證明,該系統工作狀態穩定,數據傳輸正確,能夠滿足六維并聯機構控制所需要的編碼器數據采集需求。