光纖通信在航電系統上的應用*

施天宇,鄭秀宏

(深圳技術大學中德智能制造學院,廣東深圳 518118)

0 引言

航空電子系統是現代飛機的重要組成部分,其核心組成部分為航電總線,負責各航電設備之間的數據信息傳輸[1],現在的航空電子系統已從簡單的集中控制發展到復雜的分布式系統,形成了以ARINC429、MIL-STD-1553為代表的電子系統聯網接口標準,使數據總線更加規范化。但是隨著軍用數據鏈的不斷完善和作戰指揮網絡的構建,系統間和單元間的信息交流越來越頻繁,導致總線網絡對帶寬的要求越來越高,傳統的數據總線已遠遠不能滿足系統間通信要求,急需要一種更高速率和更有效的總線傳輸模式。近年來,光纖(FC)通信已廣泛應用到民用領域,其所占市場份額也逐日增加,同時由于其容量大、衰減小、體積少、質量輕和抗電磁干擾強等優點,在軍事上應用越來越多[2-3]。目前國內對于光纖通信技術在機載航電設備上應用的有關文獻相對比較零碎,且基于理論分析較多,更多集中在整機的總線系統的分析,缺少針對單個航電設備中光纖通信設計的研究,也較少分析設計中出現的問題及解決方案。本研究主要針對基于S6連接器作為對外航插的航電設備,其在實現光纖總線通信應用設計中實際遇到的部分設計難點,并提出相對應的解決方案,希望能給相關航電設備的設計者提供一種設計思路及參考,幫助解決光纖通信在航電系統設計中的問題,推進光纖通信在機載總線中的應用。

1 光纖通信設計技術難點

1.1 光模塊的選型

自從1966年高琨[4]提出光纖作為傳輸介質,光電技術已經發生了天翻地覆的變化,光源的種類就有很多種,其中尤以LED光和激光源最為盛行。單模、多模技術日新月異,如何選取滿足要求的光模塊,而且還需要滿足各項環境要求,充滿了挑戰。

1.2 光模塊的硬件設計

1.2.1 PCIe設計

光纖屬于高速信號,必須依靠高速串行總線進行數據通信,傳統的PCI總線已經不適合,需采用PCIe設計,但設計時有以下難點。

(1)隨著PCIe總線速度的上升,則對硬件的設計要求越來越高,AC濾波電容的選擇,直接影響單位時間數據幀的長度。

(2)PCIe總線速度上升,則對其時鐘的精度要求越來越嚴苛,如何確保周期抖動、相位抖動、頻率精度和穩定度都在一個合理的范圍,是設計中的一大難點。

(3)串行數據RX和TX一般都是采用差分傳輸,可以降低共模噪聲,但如何合理的對數據總線進行去加重和預加重,保證交流RMS和共模DC的在合理范圍,優化差分回波損耗都需要值得深思。

1.2.2 光模塊的原理及PCB設計

因光模塊運行的速度至少需要上吉(G)的速度,且光模塊用于實現光電轉換的器件,其PCB布局、走線不僅僅需要滿足電氣性能[5],還應該考慮光的特性,這也是設計的一大難點。

1.3 光纖電纜的安裝設計

航電系統都有對外的連接器,本文研究的對外連接器采用S6矩形連接器,所有的信號都要與其互聯,但光信號必須依靠光纖電纜進行傳輸,如何確保光纖的彎曲率半徑,需要進行認真研究。

2 解決方案

光模塊技術雖然屬于新技術,但經過技術分析,確定了設計思路,明白設計難點,最終通過以下技術方式完成突破。

2.1 光模塊選型

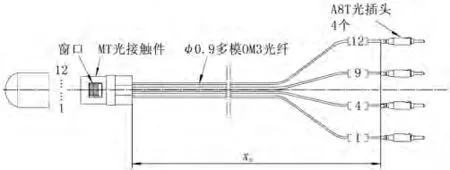

因光纖子卡的協議通常采用FPGA自定義Aurora協議,對于光模塊采用的傳輸介質并沒要求,即選擇多模和單模無要求(因光模塊無論是單模還是多模,最終的電信號都是采用高速接口,即CML電平)。在這樣背景下,通過研究2種通信媒介,關注物理結構的區別,光纖介質的差異,成本的不同,再通過了解實際光纖信號需要傳輸的長度,最后可以確定通信的媒介。在研究中選擇850 nm波長、傳輸距離小于或等于300 m的多模光纖。通過學習,了解LED光源與激光光源的差異,雖然LED光源在成本上具備一定的優勢,但為了產品具有更高的穩定性和可靠性,最后確定使用激光光源;實際使用中光纖子卡的單端口通信速率為2 GB/s,為了提高額度,光模塊需要具備一定的裕量,另外根據研究要求需滿足2路光纖總線接口,最終確定選擇傳輸速率為3.125 GB/s的四路并行收發一體的光模塊,即中航158廠的4EOLTR-85-512523M-0.035 m,如圖1所示。

圖1 光模塊

2.2 光模塊的硬件設計

2.2.1 PCIe設計

(1)高速串行總線協議規范一般都會推薦AC濾波電容,一般都為10~100 nF,如何選擇有效的電容值,必須結合數據包進行前期預判,從而提高設計精度,推進研發進度。依據經驗公式:

式中:C為交流耦合電容值;RNUM為最大容許的連0或連1的比特位數;R為負載的阻抗,一般取50Ω;T為數據速率,設計中按照2 GB/s,即T=0.5 ns。

經了解,比特位最大的長度為100,因此可以算出Cmin=7.8 nF,依據電容E-24標準系列,可將AC濾波電容確定在10 nF;

(2)周期抖動、相位抖動都與時鐘密切相關。高精度的時鐘選型和高速PCB設計相輔相許。時鐘的周期抖動需要控制在100 ps以內,相位抖動最大則為上下偏差50 ps,實際設計中所用的CPU芯片有支持單端時鐘源輸入,但肯定對噪聲很敏感,不適合。所以應選擇穩定的差分時鐘源,采用LVDS交流耦合方式,布局時緊靠負載端,嚴格控制線徑阻抗為100R,P/N端誤差控制在5 mil。一般都知,PCB的表層信號傳輸快于內層,其中表層傳輸的時間延遲為140~180 ps,而內層走線則需要180 ps,但考慮到表層的阻抗不便控制,布局的時候緊靠負載端,依據信號仿真,最后確定為內層走線。

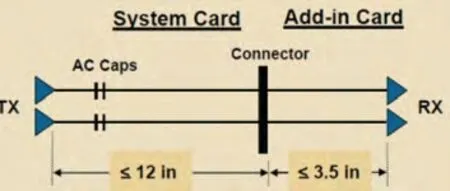

(3)預加重和去加重技術主要應用在高速串行接口,預加重和去加重技術都是為了解決傳輸信號中高頻信號的衰減。因為在高速信號傳輸中,高頻的分量衰減要比低頻分量衰減大很大,傳輸線路表現的是一個低通濾波器,所以必須采用預加重技術,在傳輸線的始端增強信號的高頻成分,即增加信號上升沿和下降沿處的幅度,維持其它地方幅度不便;去加重則是保持高頻信號上升沿和下降沿技術,其他地方減弱。依據信號仿真結果,考慮系統功耗,最終采用去加重技術,按照PCIe高速走線信號規則,長度符合圖2所示,完成PCIe從原理到PCB設計的全過程,并為后續XFS-6A系統打下良好基礎。

圖2 PCIe長度規范

2.2.2 光模塊的原理及PCB設計

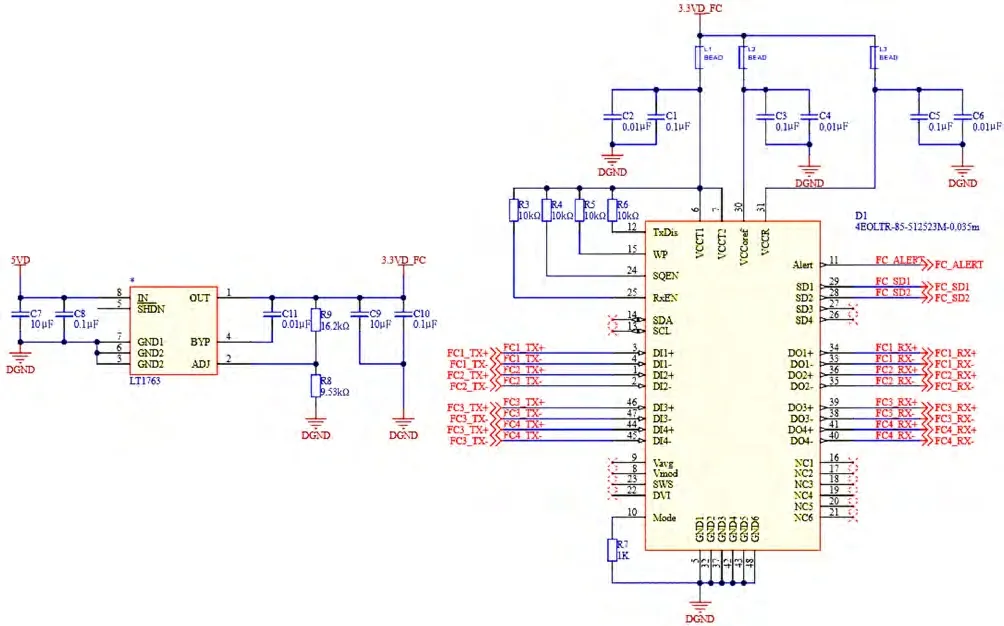

光模塊的硬件原理設計中光纖電信號與FPGA的高速接口互通,根據實際情況選擇單路或多路并行收發[6]。利用光模塊的自帶的自檢電壓告警信號(FC_ALERT)來監測光模塊是否正常工作,并通過FC_SD1和FC_SD2 2個信號對光纖電纜接收的光信號的有無進行監測,當接收端光功率高于閾值,輸出高電平,反之輸出低電平,發出光電告警信號。工作電源采用LDO設計,將數字電壓5 V轉成光模塊專用的3.3 V(3.3 V_FC),減少紋波,便于光模塊穩定工作[7]。圖3所示為光模塊的原理。

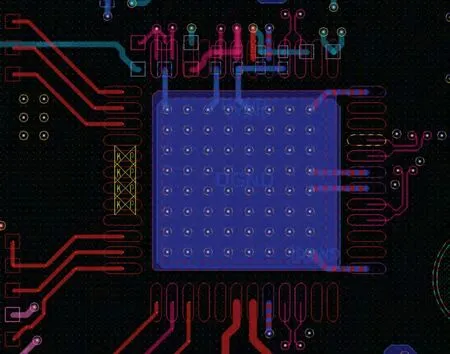

因系統的特殊性,光模塊不能直接與外部互聯,必須選擇良好的光纖跳線進行轉接。光模塊與光纖子卡采用的是高速串行總線,設計中必須按照高速原則進行走線設計,設計中采用3 W原則,控制差分對等長誤差為10 mil(實際PCB設計誤差控制在3 mil內),差分對內的P/N誤差為5 mil(實際PCB設計誤差控制在2 mil內),參考層為完整的GND平面[8]。圖4所示為PCB的實際設計圖,表1所示為實際PCB設計時FC差分對長度。

圖3 光模塊的原理設計

圖4 光模塊PCB設計

表1 FC差分對實際PCB設計長度

2.3 光纖電纜的安裝設計

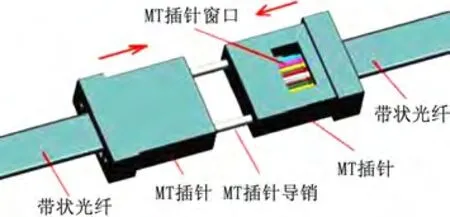

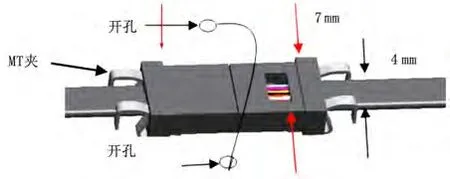

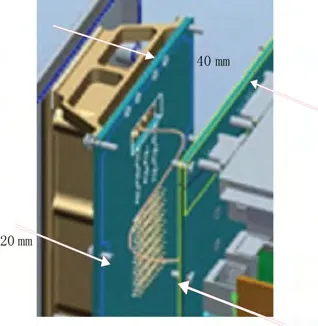

從圖1可知,必須進行相關線纜轉接,結構固定方能實現系統的組裝。加上為保證光模塊工作可靠性[9],光纖最小彎曲半徑要求為20~25倍光纖直徑,如此方能使光的耗散率、色散位移、衰減系數等指標達到最小。設計中采用多種數模工具建模分析,最終采用圖5所示的光纖線纜,光纖電纜直徑為0.9 mm,光纖線纜一端為4個A8T光插頭,可以直接插入S6矩形連接器;另一端為MT插針,與光模塊的MT插針一端對接。如圖6所示,將裝有導銷的MT插針(光纖電纜一端)與沒有安裝導銷的MT插針(光模塊一端)對接。如圖7所示,通過MT夾將對接好的2個MT插針固定,并在PCB板上開對稱的圓孔,用捆線將MT夾固定在PCB上,兩孔間距為10 mm。圖8所示為光纖電纜在結構組裝時示意圖,為滿足光纖最小彎曲半徑要求為20~25倍光纖直徑,即最小彎曲半徑為18 mm,則在產品整機結構設計時,需注意將2塊PCB板卡間距必須控制在36 mm以上,實際設計兼顧考慮減小設備長度與降低重量問題,取間距40 mm,2塊PCB板卡用矩形框架件固定,其間用捆線(圖7),將光纖電纜固定在矩形框架件側面,形成光纖電纜弧度,滿足光纖最小彎曲半徑要求,實現光模塊的組裝工作。

圖5 光纖線纜

圖6 MT夾對接方式

3 結束語

圖7 MT夾使用及固定方式

圖8 光纖系統的結構組裝

光纖通信是一種具有高實時性、高可靠性、高帶寬的開放式網絡,在帶寬、數據延遲、傳輸距離、可靠性、錯誤檢測、優先級等方面具有得天獨厚的優勢。本文在以S6矩形連接器作為對外連接器的研究前提下,通過分析,指出實際設計中出現的技術難點,對光模塊選型、硬件設計和光纖電纜的安裝進行研究設計,并在最終實際產品的驗證下,實現了光纖通信在航電設備上的應用,證明了本文提出的解決方案的可行性。并通過光纖總線的運用,減輕機載產品質量,增強的抗電磁干擾能力,帶寬高可以提高飛機內部數據信息傳輸速率,提高產品的競爭性。