改進型自偏置帶隙基準源電路設計

譚傳武,傅宗純

(湖南鐵道職業技術學院電務學院,湖南株洲 412001)

商用5G 技術促進了各行各業走向智能化,全國已開通5G 基站共12.6 萬個[1-2],5G 基站要求低時延、大連接、高速率等特點去匹配各行各業智能化的應用需求[3],然而5G 基站的耗電量高居不下,各行各業在智能化推進的同時,也要考慮耗電量等硬件和服務成本[4-5]。因此,降低5G 基站的能源消耗是目前推進智能化最為緊迫的課題。基站的電源管理芯片是能源的核心元件[6-7],其帶隙基準源的穩定性和功耗直接影響芯片的綜合性能,進而直接影響基站的能源消耗[8],因而5G 低功耗技術成為了目前的研究熱點。

5G 技術商用以來,研究者在降低基站功耗上面都做了很多相關研究。中國電信股份有限公司廣東研究院何峣發表了"業務流量特征對5G 基帶芯片功耗的影響分析"的研究成果[9],通過研究典型移動業務的流量特征,能夠準確地分析其對5G 基帶芯片功耗的影響,并且能夠為終端的功耗優化提供依據,但不能直接降低終端功耗;北京郵電大學鄒林琳提出了一種新型的自適應傳輸策略[10],通過引入傳輸與空閑雙模式,讓收發機選擇更好的信道條件來完成數據傳送,該方案基于信道條件自適應地選擇傳輸或空閑模式,以實現節約能量的目的,但自適應的傳輸策略實現過程較復雜。因此,該文在基站的電源管理芯片上進一步研究,改進帶隙基準源電路結構,進而降低芯片本身的功耗,來達到降低基站功耗的目的,在傳統的帶隙基準源結構上進行改進,設計一種結構簡單、功耗低的帶隙基準結構,旨在為降低5G 基站的能耗提供改進思路。

1 帶隙基準的基本原理

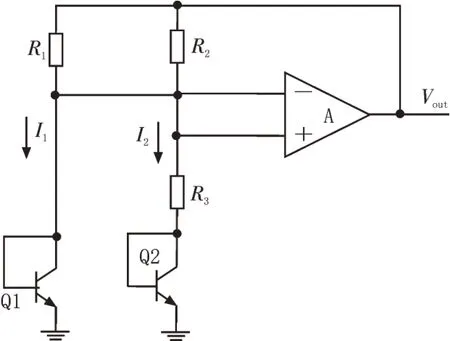

帶隙基準電壓產生是依據硅鍺等材料的PN 結電壓與工藝和溫度無關的特性[11-12],利用ΔVBE的正溫度系數(電阻)與晶體管VBE的負溫度系數相互匹配,實現零溫度系數的基準電壓[13-14]。傳統的帶隙基準電路結構如圖1 所示。

圖1 傳統帶隙基準的基本結構

結合運放的虛短和虛斷理論[15-16],從圖1 可知,應用運放輸入端“虛斷”理論可得:

假設運放的開環增益足夠大,可得:

選擇適當的n與R2、R3的值,可以使式(6)為0,可近似認為基準輸出與溫度無關。

2 帶隙基準電路設計

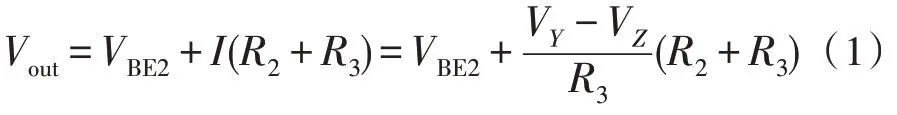

運放結構設計如圖2 所示,運放使得兩個輸入點的電平相等[17-18]。第一級采用共源共柵結構保證電路的高增益,同時把雙端信號單端化[19-20]。第二級采用共源放大器,兩級之間接一個2 pF 的MOS 電容,迫使主極點向原點靠近[21];電路設計時將運放輸出級的電阻值減小,目的是讓次極點與主極點遠離,達到提升運放穩定性的效果。

圖2 運算放大器

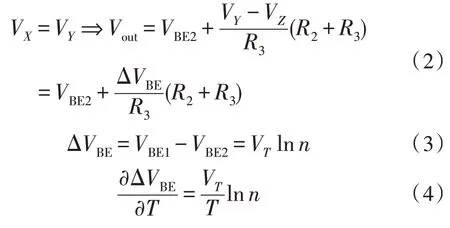

該文改進了傳統的帶隙基準電路,如圖3 所示,由運放的虛短理論可得[22],DPNP15B 與DPNP14B 的電壓被強制相等,由電阻大小可得,流過PNP 管I5 和PNP 管I4 的電流之比為10∶13,而I5 和I4 的個數比為8∶2,可得ΔVBE電壓如式(7)所示。

圖3 帶隙基準源電圖

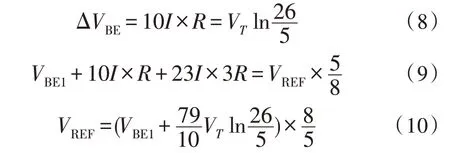

假設流過I5 的電流為10I,則流過I4 的電流為13I,設PNP 管I5 上方電阻為R,則I4 處電阻為3R,可得VREF(BP17D)的計算如式(8)、(9)、(10)所示。

基站的電源管理芯片要求帶隙基準低功耗,以達到省電、高效的目的。改進的帶隙基準電路是自偏置結構,DPNP1B 為偏置電壓(由帶隙產生),BP17D為帶隙輸出,包含帶隙核心、運放和偏置電路三部分。

改進的帶隙核心電路中,對I5 和I4 上的電阻進行了改進,并聯了同阻值的若干個電阻,用于調整帶隙電路基準的穩定性。

改進的偏置電路中,用同樣尺寸的27 kΩ電阻進行串并聯組合,用于調整偏置電流,使得輸出電流恒定,偏置電路與基準輸出構成負反饋,保證了偏置輸出的穩定性,同時保證了帶隙電壓的穩定性。

3 帶隙基準仿真

對帶隙基準電路進行Hspice 仿真,在常溫下將電源電壓從2 V 變換到5 V,結果如圖4 所示。電壓穩定在1.18 V 左右。

圖4 帶隙輸出對電源電壓變化的仿真

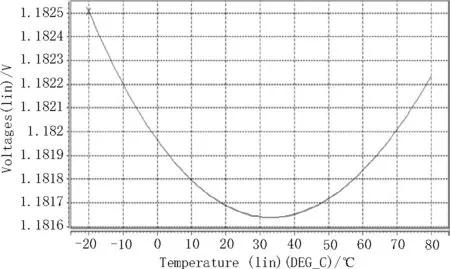

設定溫度從-40~+125 ℃變化,掃描仿真結果如圖5 所示,在溫度變化下,帶隙輸出為1.181 6~1.182 5 V,溫度系數僅5.45 ppm/℃,基準隨溫度變化影響極小。

圖5 帶隙輸出對溫度變化的仿真

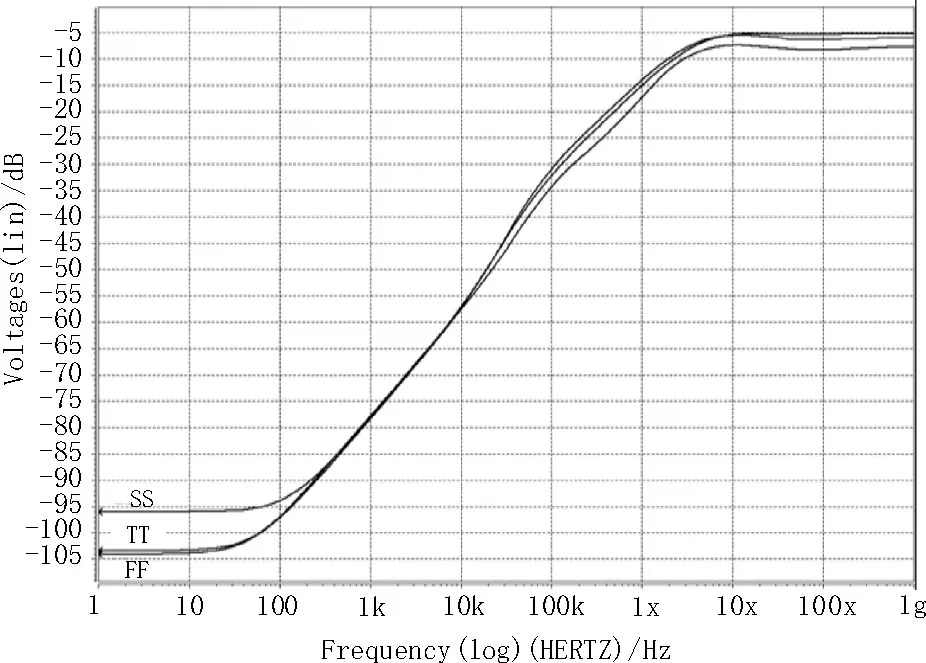

對基準源電路進行電源抑制比仿真,結果如圖6所示。

圖6 基準源電路的PSRR仿真

由圖6 可以看出,在TT、FF、SS 3 種工藝角下,電源抑制比達到95 dB 以上,電路具有很強的低頻電源紋波抑制能力。

4 結束語

針對目前5G 基站高功耗的問題,該文提出改進電源管理芯片中帶隙基準的結構方案,依據方案改進了傳統的帶隙基準源的結構,設計了一種結構簡單、功耗低的自偏置帶隙基準電路。該電路無啟動電路既節省了芯片面積,又達到了降低功耗的目的,能廣泛應用于電源管理芯片中,為降低5G 基站高功耗問題,提供了解決思路。