一種新型SPI NAND控制器設計?

陳 亮,蔡聲鎮

(1.福州理工學院計算與信息科學學院,福建 福州 350506;2.福建師范大學數學與信息學院,福建 福州 350117)

閃存介質(NAND Flash)因其低延時、高并行、低能耗、體積小等特點受到了廣泛關注,基于閃存介質構建的閃存存儲系統是當前的研究熱點,構建形式多樣[1]。存儲系統主要由主機、存儲設備構成;閃存設備主要由閃存介質、閃存控制器兩部分構成。Open-Channel SSDs,Denali 等為新型的閃存控制器架構[2],根據應用需求,將閃存轉換層(flash translation layer,FTL)、垃圾回收等功能從存儲設備移植到主控端實現,從而提升存儲系統整體性能。

SPI NAND Flash 為嵌入式領域的閃存設備,主要用于嵌入式系統的代碼存儲和數據存儲,其主流的存儲容量為1 Gbit/2 Gbit/4 Gbit,典型的傳輸速率為30 Mbit/s,50 Mbit/s,80 Mbit/s 等[3]。圖1 所示為傳統的SPI NAND 存儲系統,閃存介質相關的介質管理,壞塊管理,地址映射等功能均放在主控端實現。該架構的優點是簡化SPI NAND Flash 內部控制器,不足是存儲容量小、傳輸速率低、不同廠商協議命令復雜繁多不統一。隨著物聯網技術的迅猛發展和人工智能等復雜計算或邊緣計算的引入,嵌入式設備對性能和存儲容量的需求呈現大幅增長。如何實現大容量、高速率和簡化及統一協議命令,已成為SPI NAND Flash 需要急迫解決的問題。

圖1 傳統SPI NAND 存儲系統

本文借鑒Open-Channel SSDs 的設計思想,提出了一種新型SPI NAND 控制器的設計方法,針對SPI NAND 存儲系統架構和控制器軟件進行優化設計[4],可實現較大幅度提升上述主流SPI NAND Flash 在存儲容量、傳輸速率和主控命令復雜度等方面的性能指標。

1 系統架構設計

主控端處理器性能和內存資源都優于SPI NAND 控制器,為了高效實現主控端的閃存介質相關功能,在系統架構設計上,需要對SPI 接口和Flash 閃存接口進行硬件加速設計。同時主控端不再考慮閃存介質的特性,可以簡化并統一SPI 接口傳輸指令。對控制器的功能和性能進行合理分布,使用模塊化設計理念,整個架構分為前端、FTL、后端三個模塊,模塊之間通過32 位AXI 總線連接,每個模塊處理各自任務,流水作業,形成高效緊湊的SOC 系統,見圖2。

圖2 SPI NAND 控制器頂層架構

前端模塊主要負責與主機的接口指令協議處理和數據在Central Buffer 和主機之間高效傳輸。FTL 模塊主要由CPU 實現主控端的閃存介質相關功能,比如地址映射、垃圾回收、損耗均衡等。后端模塊主要根據FTL 模塊的地址映射算法,實現Flash 顆粒管理和數據在Central Buffer 和Flash 顆粒之間高效傳輸。

2 功能模塊設計

2.1 SPI 控制器設計

SPI 接口指令簡化為數據傳輸和控制指令,在傳統SPI 控制器基礎上[5-6],實現了協議控制邏輯,將命令解析軟件功能通過硬件來實現,加速SPI 接口指令處理能力。協議控制邏輯格式化硬件解析SPI 接口命令,區分指令類型,提取指令中地址和數據長度等信息,并按照自定義格式傳遞給處理器。

圖3 所示SPI 控制器框圖,SPI 控制器通過32位AXI Master 總線與SOC 系統連接,采取DMA 方式進行數據的高效傳輸;通過32 位的AXI Slave 總線和SOC 系統連接,支持軟件配置SPI 控制器。靈活配置SPI 接口工作在標準模式(1 bit 傳輸),雙線模式(2 bit 傳輸),四線模式(4 bit 傳輸);工作模式可在主設備/從設備模式切換。

圖3 SPI 控制器

2.2 Flash 控制器設計

傳統的SPI NAND 存儲系統,對Flash 顆粒的介質管理通過主機軟件來實現。通過硬件方式實現Flash 管理,可降低對處理器性能要求,提高Flash 顆粒讀寫鏈路的吞吐量。尤其將BCH 糾錯算法,采用硬件引擎實現,降低糾錯運算延遲,提升Flash 讀操作效率。

Flash 控制器的主要功能是管理Flash 顆粒,完成對顆粒的reset、erase、read、write 操作。圖4 為Flash 控制器框圖,主要由Page Buffer,BCH ECC 引擎,die 控制邏輯,die 仲裁邏輯,以及兩組32 位的AXI 總線接口構成。BCH ECC 引擎為Flash 控制器的核心部分,設計為8 bit/512 byte 的糾錯能力,支持SLC 和部分MLC 顆粒[7],為了提升Flash 控制器的性能,采用兩個die 控制邏輯,將讀寫Flash 顆粒的命令進行并行化設計,每一個die 控制邏輯對應映射到顆粒中的一個die,并通過die 仲裁邏輯進行調度操作[8]。

圖4 Flash 控制器

2.3 Central Buffer 的設計

Central Buffer 模塊作為數據緩存,用于SPI 控制器和Flash 控制器之間大批量數據交互,并為控制器軟件實現地址映射,均衡算法,垃圾回收等功能提供硬件基礎。靈活的Central Buffer 設計,對控制器整體性能起到關鍵作用。其采用雙口RAM 結構設計,分別擁有A 和B 兩組獨立讀寫接口,A 端口與SPI 控制器同頻,由SPI 控制器、CPU、系統DMA共享;B 端口與Flash 控制器同頻,由Flash 控制器使用(見圖2)。

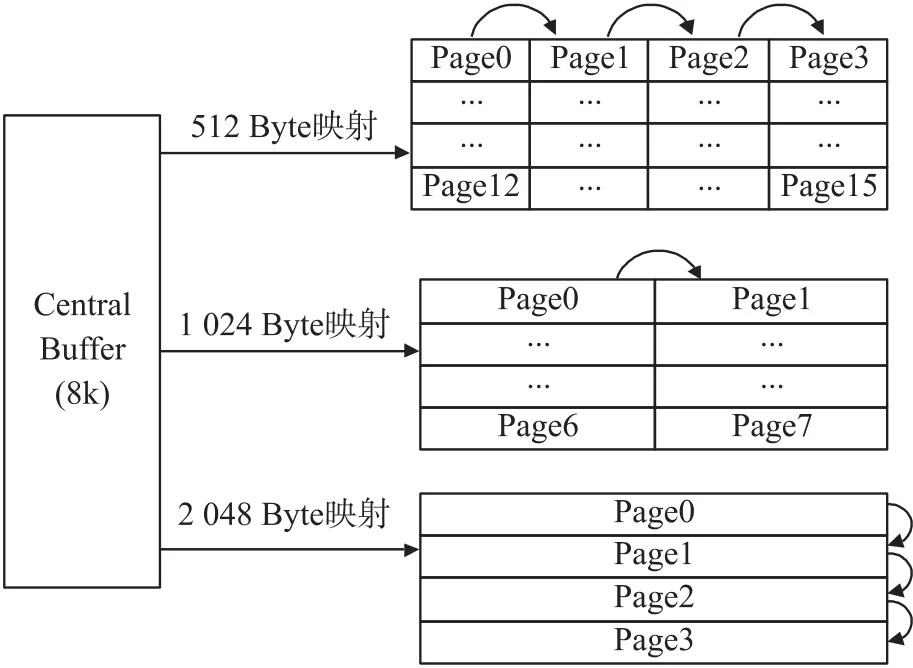

考慮SLC 和MLC 顆粒的特性,其Page 一般為512/1 024/2 048 字節。嵌入式設備的文件系統一般以sector(512 字節)為最小的單元。根據顆粒和文件系統的需求,Central Buffer 的容量設計為8 kB,將Central Buffer 按照512/1 024/2 048 字節的頁進行靈活劃分,采用鏈表的數據結構進行調度管理[9],如圖5 所示。

圖5 Central Buffer 映射

2.4 系統帶寬設計

SPI 協議的端口時鐘SCK 范圍為10 MHz~104 MHz,支持標準模式和雙線、四線、八線模式,端口傳輸速率從10 Mbit/s 到最高832 Mbit/s[10]。MLC 和SLC 顆粒采用ASYNC 和ONFI1.2 協議,支持異步模式和同步模式,同時支持NV-DDR 技術,即允許顆粒采用雙沿觸發采樣數據的技術,端口傳輸速率從10 Mbit/s 最高可達100 Mbit/s[8]。

考慮對未來高性能的需求,將SPI 端口的最高傳輸速率定義為8 線模式,驅動時鐘為104 MHz,則其傳輸速率為104 Mbit/s。Flash 端口的最高傳輸速率定義為NV-DDR 的模式2[8],其傳輸速率為100 Mbit/s。SPI 端口和Flash 端口的速率是匹配的。對于控制器內部系統互聯的AXI 總線,采用32 bit 位寬和50 MHz 時鐘,則AXI 總線的傳輸速率為200 Mbit/s,可滿足線速的設計要求。

2.5 軟件設計

通過SPI 控制器和Flash 控制器的硬件加速功能,架構上的CPU(32 位RISC 處理器),在不降低性能條件下,實現對Flash 顆粒相關的復雜管理移植,把SPI NAND 抽象為類似RAM 的訪問模式,屏蔽顆粒底層的復雜信息;同時給嵌入式設備主控提供統一的指令協議,從而達到簡化嵌入式主控的驅動設計。SPI NAND 控制器的軟件架構如圖6所示。

圖6 軟件功能

控制器內的CPU,實現SPI NAND 存儲系統的核心功能,包括對SPI 接口的控制,自定義協議的解析處理,Cache/Buffer 的管理,算法的映射,NAND Flash 的管理等功能。尤其是FTL 的算法映射功能[11],包含地址映射[12],垃圾回收[13],損耗均衡[14]和壞塊管理。

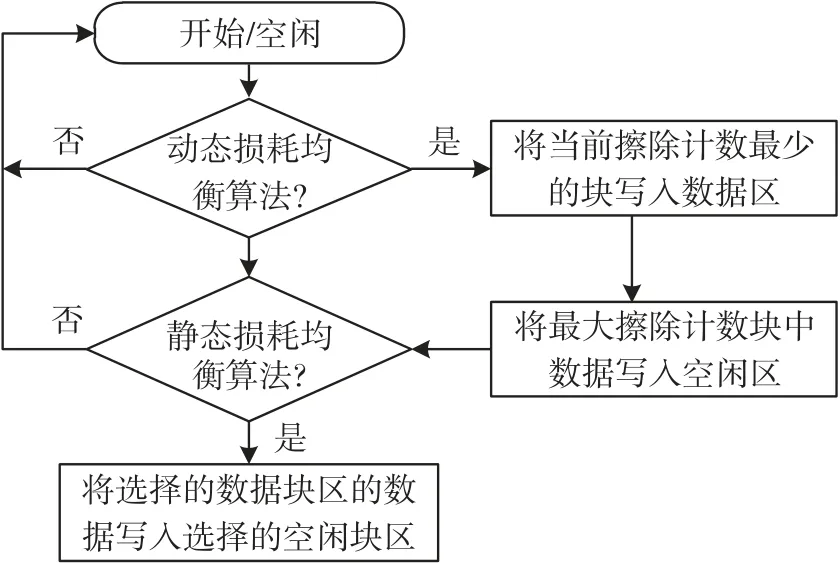

以損耗均衡為例,在SPI NAND 使用過程中,存在用戶數據及其訪問行為冷熱不均,導致顆粒一些物理塊長期不被使用,而另一些物理塊被頻繁使用的情況,長此以往將導致某些塊提前壞掉,嚴重影響SPI NAND 的壽命。損耗均衡通過軟件監控顆粒上每個塊的擦除次數以及塊上數據的存入時間,然后控制所有的擦除次數在平均擦除次數附近偏移,一旦超過設定的最大偏移值,則該塊閑置不用。損耗均衡按照算法執行的系統空間分布情況,可以分為動態損耗均衡[15]和靜態損耗均衡[16],通過兩種均衡算法的結合,SPI NAND 中的物理塊均衡使用,提高使用壽命。算法流程如圖7 所示。

圖7 損耗均衡流程

3 性能測試與分析

3.1 測試環境搭建

為了驗證本文SPI NAND 控制器的性能,采用工業界最主流和具有代表性的旺宏公司的SPI NAND 顆粒MX35LF[10],在FPGA 開發板搭建了性能測試平臺,如圖8 所示,由主控端、設備端構成。主控端由一塊Xilinx 公司的Artix-7 開發板實現,為了盡量消除主控端軟硬件對測試的影響,采用兩組完全一樣的SPI 接口,接口SCK 時鐘均工作在50 MHz,Microblaze 處理器工作在200 MHz。設備端由另外一塊Artix-7 開發板和MX35LF 顆粒子板構成,SPI NAND 控制器通過Verilog 代碼設計和驗證,燒寫到另外一塊Artix-7 開發板。SPI0 支持主/從設備兼容模式,通過軟件實現自定義協議,通過改進型SPI 接口和實現了SPI NAND 控制器的FPGA 開發板相連接。SPI1 支持主設備模式,通過傳統SPI接口和MX35LF 顆粒子板相連。根據MX35LF 的數據手冊,在讀取數據時,MX35LF 顆粒Trd 為25 μs,在寫入數據時,MX35LF 顆粒Tprog 設置為320 μs。整個測試平臺的測試代碼均運行在Microblaze 處理器上。

圖8 測試平臺

3.2 控制指令

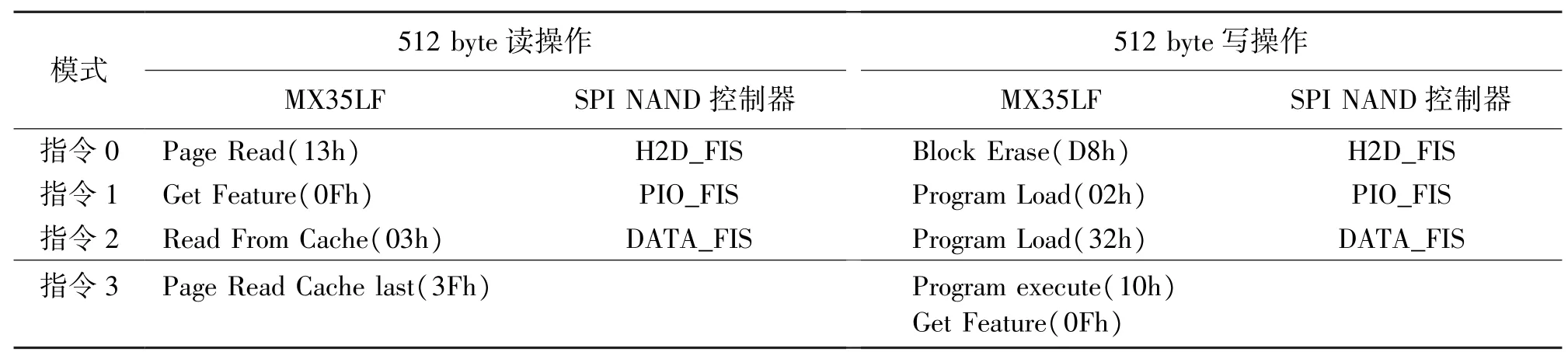

在SPI NAND 控制器和MX35LF 進行讀寫的對比測試過程中,同樣的讀操作,MX35LF 需要4 條指令完成,不同的讀方式,還需要額外6 條指令;同樣的寫操作,MX35LF 需要4 條指令完成,不同的寫方式,還需要額外2 條指令,而SPI NAND 控制器的讀寫操作是一致的,只需要支持2~3 條指令,明顯簡化并統一了主控端的驅動。相關的指令比較如表1所列。

表1 指令系統比較

3.3 存儲容量

Flash 控制器的尋址范圍是決定Flash 存儲器存儲容量的關鍵指標。MX35LF 的尋址位寬為24 bit,同時最小粒度為1 字節;本文的SPI NAND 控制器尋址位寬為28 bit,最小粒度為512 字節,支持的存儲容量是MX35LF 的213倍,通過Flash 控制器并行連接多個die 的方式,可以支持高達128 GB 的存儲容量。

3.4 傳輸速率

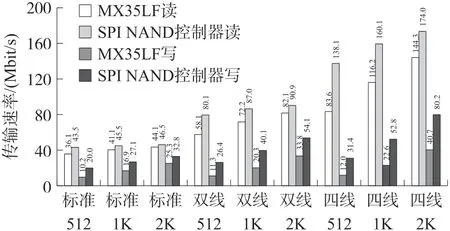

設置SPI0 和SPI1 的SCK 為50 MHz,對SPI NAND 控制器和MX35LF 分別進行讀寫數據測試,數據的粒度分為512 byte、1K、2K 三個檔次,SPI 分別配置為標準(50 Mbit/s)、雙線(100 Mbit/s)和四線(200 Mbit/s)模式,圖9 所示為讀數據和寫數據的性能比較,顯然存在如下規律:

圖9 性能比較

(1)由于讀寫數據時,每次傳輸的命令長度是固定的,隨著傳輸數據長度變長、傳輸線數變多,命令所占傳輸時間比例降低,因此有效數據傳輸速率隨數據長度提升。

(2)MX35LF 部分命令不能通過改變線數實現并行傳輸,隨著傳輸數據長度變長,自定義存儲設備傳輸速率的優勢越明顯。

(3)對于寫操作,由于NAND Flash 顆粒特性決定了Tprog 時間比較長,而且無法進行并行寫操作。SPI NAND 控制器采用了Central Buffer 的設計方法,以及Flash 控制器支持雙die 引擎,支持對NAND Flash 顆粒的并行操作,整體性能比MX35LF 提升一倍左右。

4 結論

本文介紹了一種新型的SPI NAND 控制器的設計和實現,重點描述了SPI NAND 控制器的架構設計以及SPI 控制器、Flash 控制器、Central Buffer 的設計和軟件設計。通過測試驗證,與當前主流Flash存儲設備進行性能比對,在讀寫數據方面效率獲得顯著提升。證明了架構的合理性和高效性。