基于Zynq-7000 的實時視頻圖像處理系統框架設計

張祖昊,王云光

(1.上海理工大學 醫療器械與食品學院,上海 200093;2.上海健康醫學院 醫療器械學院,上海 201318)

0 引言

數字圖像處理技術在機器視覺和計算機視覺技術領域起著至關重要的作用。越來越多的領域不斷對圖像處理提出新的要求,在圖像處理算法復雜性持續增加的同時還要滿足圖像分辨率和每秒傳輸幀數(Frames Per Second,FPS)[1-3]要求。醫療領域的電子內窺鏡需要在手術時將人體內部的畫面實時且清晰地輸出到顯示屏上[4-5]。目前電子內窺鏡的分辨率普遍在1 280×720 以上,因此對系統帶寬、數據吞吐率要求較高,軟硬件協同工作是最佳的解決方案。朱炎均[6]使用ZedBoard 完成320×240 分辨率視頻實時處理,由于沒有使用DMA 技術,因此整體帶寬提升不多;李振宇[7]使用Zynq 完成VGA 格式1 280×720 分辨率視頻實時處理,但是由于輸出的不是HDMI 信號,因此應用范圍較窄。雖然傳統的FPGA 可以利用其并行特性提高系統吞吐率,但在開發圖像處理算法時使用Verilog 效率很低[8-9],ARM+DSP 難以解決該問題。

本文采用Xilinx 公司的Zynq-7000 系列可編程(System On Chip,SOC)ARM+FPGA 異構設計作為視頻圖像處理平臺,該平臺主要由處理系統(Processing System,PS)和可編程邏輯(Programmable Logic,PL)兩部分構成[10]。其中PS部分包含兩塊ARM Cortex-A9 雙核處理器,負責系統控制;PL 部分由Xilinx 7 系列FPGA 構成,負責視頻信號采集、處理、緩存和輸出工作。系統采用OV5640 作為圖像傳感器,HDMI 顯示器作為視頻輸出,使用Xilinx 公司的Vivado HLS作為圖像處理算法開發工具,將C/C++轉換成RTL Verilog代碼并封裝成IP,可在提高系統整體帶寬和吞吐率的同時,大大加快圖像處理算法的開發速度。

1 系統整體框架

系統由采集、處理、緩存、顯示4 部分組成,系統結構如圖1 所示。系統由PS 和PL 通過AXI4 總線連接協同完成。采集部分使用Zynq 的PS 端對OV5640 攝像頭的寄存器組發送不同寄存器值,完成攝像頭初始化工作。再通過Zynq的PL 端自定義OV5640 完成數據采集工作;圖像處理使用Xilinx HLS 開發工具,將C/C++轉換成Verilog 語言并封裝成IP,使用PL 將其例化;視頻緩存使用Xilinx 官方提供的VD?MA(Video Direct Memory Access)IP,實現3 幀畫面緩存,以避免畫面閃爍和撕裂等現象;視頻顯示通過Zynq 的PL 端輸出IP,將視頻信號以HDMI 的時序輸出。

2 Zynq-7000 系列設計流程

由于Zynq 將ARM 與FPGA 集成在一起,開發工作既要設計ARM 的應用程序,又要設計FPGA 部分的硬件邏輯設計,因此Zynq 開發需要遵循軟硬件協同開發方式,以達到提升開發效率和產品性能目的。Zynq-7000 系列嵌入式開發步驟如下:①在Vivado 中創建新的工程;②使用IP 集成器創建處理器系統;③生成頂層HDL 并導出設計到SDK;④創建應用測試程序;⑤設計驗證[11]。其中Vivado 是FP?GA 的硬件開發,生成的頂層HDL 文件就是硬件設計生成的結果。將其導入到SDK 后再創建應用測試程序,進行相應的軟件開發。測試程序根據HDL 提供的BSP(Board Sup?port Package)板級支持包中提供的硬件資源完成指定任務。合理分配硬件和軟件的任務分工也是軟硬件協同開發十分重要的一步,本設計將OV5640 攝像頭和VDMA 初始化配置工作交給軟件處理,剩下所有視頻信號采集、處理和輸出工作全部交給硬件完成。

3 Vivado 硬件部分設計

圖2 為使用VivadoIP 集成器創建的Block Designer 工程圖,其中的核心模塊是ov5640_capture_data_0,ov5640_so?bel_0,axi_vdma_0 和DVI_Transmitter_0,分別對應采集、處理、緩存和顯示。下面分別從數據流通路和控制流通路介紹該硬件設計原理。

Fig.2 Vivado block design圖2 Vivado 塊設計

當PS 將OV5640 配置完成后,其數據引腳就會在每個像素時鐘周期輸出一個8bit 的數據信號到ov5640_cap?ture_data_0 模塊的cam_data[7:0]輸入引腳。該模塊功能是采集攝像頭輸出的數據并將其從RGB565 格式轉換成視頻流RGB888 格式輸出。然后數據從ov5640_capture_data_0 的cmos_rgb 引腳輸出到v_vid_in_axis4s_0 模塊的vid_io_in 引腳。該模塊功能是將視頻信號轉換成AXI4-Stream 視頻協議信號[12]。經過轉換后數據從v_vid_in_axis4s_0 的video_out 引腳輸出到HLS 圖像處理模塊的INPUT_STREAM 引腳,該模塊功能就是對視頻信號進行實時處理,可以嵌入一層或多層不同的HLS 模塊實現不同的圖像處理算法。經過圖像處理后,數據從HLS 模塊的OUT?PUT_STREAM 引腳輸出到axi_vdma_0 的S_AXIS_S2MM 引腳。該模塊在PS 對其初始化配置完成后即可直接對DDR3進行讀寫操作,實現畫面的幀緩存功能[13]。VDMA 和DDR3 之間還需要通過AXI SmartConnect 和Zynq 的AXI HP總線進行連接,因此數據會從axi_vdma_0 模塊的M_AX?IS_MM2S 引腳流出到axi_smc 模塊的S01_AXI 引腳,再從M00_AXI 引腳流出到Zynq 模塊的S_AXI_HP0 引腳,此時即完成畫面幀緩存的數據通路。然后進行畫面輸出顯示數據流。當一幀畫面緩存完成后,DDR3 中的數據就會通過Zynq 模塊的S_AXI_HP0 輸出到axi_smc 模塊的M00_AXI引腳,再從S00_AXI 引腳輸出到axi_vdma_0 模塊的M_AXI_MM2S 引腳,完成VDMA 模塊對DDR3 的讀操作。axi_vdma_0 接收到DDR3 數據后再從M_AXIS_MM2S 引腳輸出到v_axi4s_vid_out_0 模塊的video_in 引腳,該模塊功能與v_vid_in_axi4s_0 的功能相反,是將AXI4-Stream 協議信號格式轉換成視頻流信號格式[14]。經過v_axi4s_vid_out_0模塊轉換后從vid_io_out 引腳輸出到DVI_Transmitter_0 模塊的Video_In 引腳,該模塊功能是將視頻流信號轉換成HDMI 信號格式輸出到HDMI 接口上,最后通過TMDS 引腳輸出到HDMI 顯示器,完成畫面輸出顯示的數據通路。

控制流通路所有的控制信號均由Zynq 模塊發出,系統需要完成的控制有:①OV5640 初始化配置;②VDMA 初始化配置;③整個系統的復位和時鐘信號。OV5640 的控制流通路通過Zynq 模塊的GPIO_0 引腳輸出到emio_sccb 引腳,來往于OV5640 的寄存器中寫配置信息。VDMA 時鐘控制流通路通過Zynq 模塊的M_AXI_GP0 引腳輸出控制信號到ps7_0_axi_periph 模塊的S00_AXI 引腳,該模塊是AXI Inter?connect 的一個實例,可讓Zynq 模塊同時與多個AXI4 總線協議模塊互聯,在ps7_0_axi_periph 輸出端分出4 個AXI 輸出引腳,分別用來控制VDMA、axi_dynclk_0 和v_tc_0。其中axi_dynclk_0 是動態時鐘生成器實例,用來管理整個系統時鐘信號;v_tc_0 是視頻時序生成器實例,用來控制HD?MI 輸出時序。復位控制流通路通過Zynq 模塊的FCLK_RESET0_N 引腳輸出到rst_ps7_0_50M 模塊,該模塊是處理器系統復位實例,用來控制整個系統的復位工作。系統控制流通路通過這些控制信號使整個系統完成采集、處理、緩存和顯示功能。

4 HLS 圖像處理設計

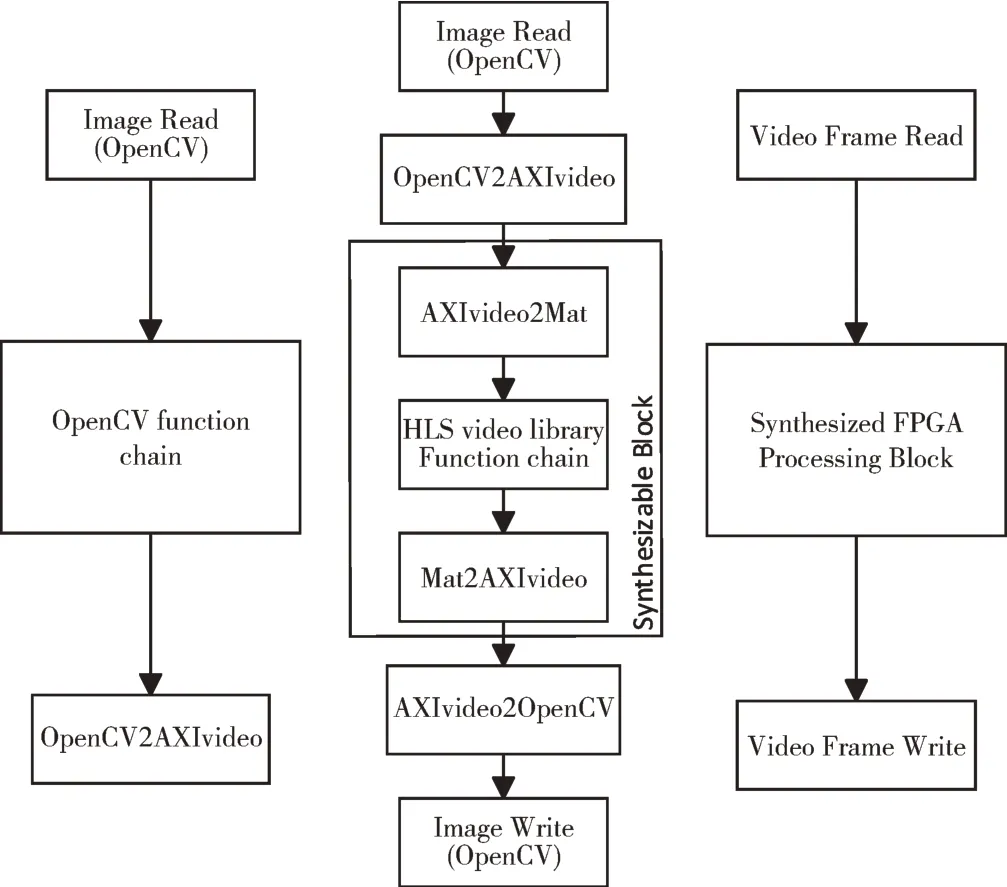

本系統圖像處理模塊使用Vivado HLS 開發,在HLS 中移植了大量的OpenCV 函數庫,可以調用移植后的OpenCV函數庫對圖像進行處理[15-16]。但是需要注意的是,HLS 中的OpenCV 函數庫與OpenCV 函數庫并不完全相同。OpenCV 函數是不能直接綜合的,因此必須由可綜合的庫函數替換,主要原因是OpenCV 函數涉及到動態內存分配,在FPGA 中動態內存分配是不可綜合的行為。圖3 為使用OpenCV 與HLS 視頻庫進行圖像處理流程。

Fig.3 Image processing flow of Opencv and HLS video library圖3 OpenCV 與HLS 視頻庫圖像處理流程

與傳統OpenCV 圖像處理相比,使用HLS 視頻庫進行圖像處理需要將OpenCV 格式的數據轉換成AXI 視頻格式,該操作通過IplImage2AXIvideo 函數完成;然后將AXI 視頻格式轉換成Mat 格式,該操作通過AXIvideo2Mat 函數完成;之后就可調用HLS 中移植的OpenCV 函數庫進行圖像處理。這里調用的是Sobel 強邊緣檢測對圖像處理效果進行測試,處理完之后再將Mat 格式轉換成AXI 視頻格式,最后還原成OpenCV 格式,這樣就完成了使用HLS 中OpenCV視頻庫對視頻圖像進行處理的過程。可以通過這個過程在PC 上使用一張圖像驗證圖像處理算法效果。當驗證通過之后,再把圖中方框部分封裝成一個RTL 級IP 核,嵌入到前面的Vivado 硬件設計的Block Design 采集模塊和緩存模塊中間,即可以實現實時視頻圖像處理功能。

圖4 為PC 上使用HLS 進行Csimulation 處理的效果圖片,實現的是水平Sobel 梯度算子的掩膜計算。可以看到,經過圖像處理后,右圖很好地將原圖中垂直邊緣檢測出來,效果顯著。

Fig.4 Simulation processing effect of HLS video library on PC圖4 PC 上HLS 視頻庫仿真處理效果

5 SDK 軟件部分設計

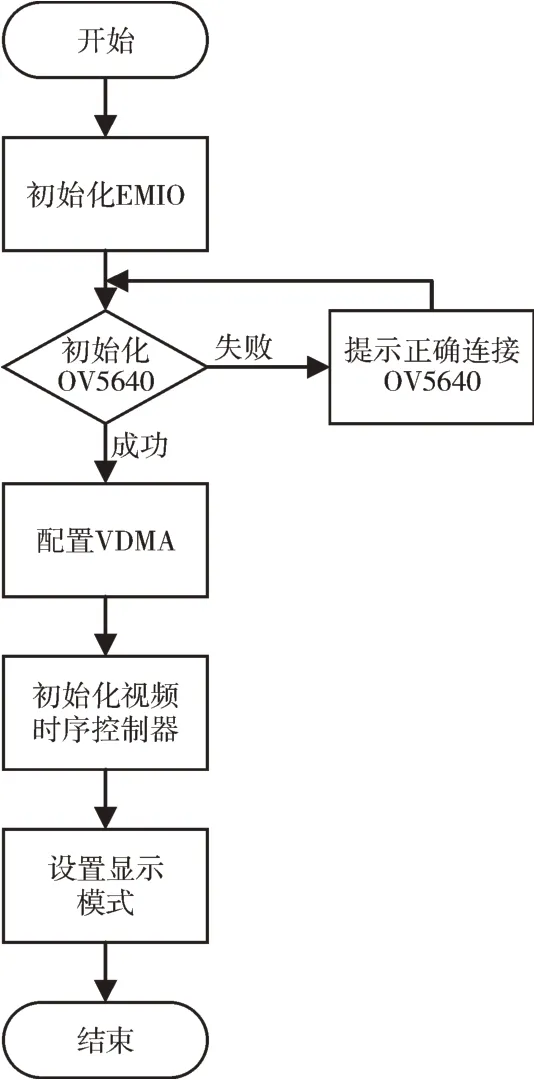

SDK 軟件部分需要完成的工作有:①初始化EMIO;②初始化OV5640 攝像頭;③配置VDMA;④初始化顯示時序控制器;⑤設置顯示模式。圖5 是SDK 應用程序設計流程。

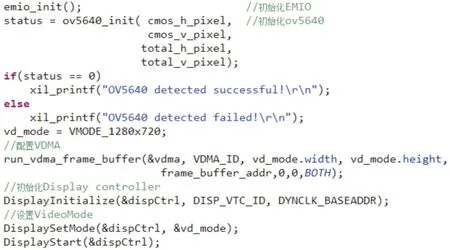

SDK 中所有的工作都是通過調用BSP(Board Support Package)中的庫函數完成的,而該BSP 是根據前面的Vivado硬件設計部分提供的。首先初始化Zynq 上的兩個EMIO 引腳,將其用作SCCB 通信引腳,因為這里只需要對OV5640進行寫寄存器操作,所以這里的時鐘線和數據線都設置成輸出管腳,這里封裝了一個emio_init 函數用于初始化EMIO 引腳;然后初始化OV5640 攝像頭,通過調用一個封裝好的ov5640_init 函數,先檢查ov5640 是否正確連接,如果檢查通過則調用sccb_write_reg16 函數,往ov5640 不同的寄存器地址內寫入不同的寄存器值。這里OV5640 被配置成DVP(Digital Video Port)輸出接口、1 280×720 分辨率和30FPS(Frame Per Second)。接下來配置VDMA,調用一個封裝好的run_vdma_frame_buffer 函數,該函數內部包括配置幀緩存地址、寫通道配置、讀通道配置、開啟寫通道和開啟讀通道配置等。VDMA 配置成3 幀圖像緩存功能。初始化視頻時序控制器調用DisplayInitialize 函數,包括VTC(Video Timing Controller)和動態時鐘配置。通過Display?SetMode 函數設置顯示模式和啟動顯示圖像,采用Display?Start 函數啟動VTC 開始工作輸出圖像到HDMI 接口。圖6是SDK 主要調用的函數截圖。

Fig.5 SDK initialization engineering application process圖5 SDK 初始化工程應用程序流程

Fig.6 Functions mainly called by SDK application圖6 SDK 應用程序主要調用的函數

6 系統測試

本設計使用Alinx 公司的AX7Z020 開發板作為測試平臺。為測試整個系統工程,方便后期使用,還需將程序固化到Flash 中,以免每次啟動工程都需要通過JTAG 接口燒寫。Zynq 啟動由ARM 主導,包括FPGA 程序的加載,啟動階段如下:①階段0。在上電復位或熱復位之后,處理器首先執行BootRom 中的代碼,此為最初啟動設置。BootRom存放了一段不可更改的代碼,在非JTAG 模式下執行,代碼包含Quad-SPI、SD 的驅動,還有一個很重要的作用是把階段①的代碼搬運到OCM 中,就是FSBL 代碼(First Stage Boot Loader);②階段①的作用是初始化PS 端配置,也就是在Vivado 工程配置Zynq 核,包括DDR、MIO、SLCR 寄存器。如果有PL 端程序就加載PL 端bitstream,加載bare-metal 應用程序到DDR 存儲器,交接給bare-metal 應用程序[17]。因此,根據上面描述,需要再生成一個FSBL 引導程序,完成MIO 分配、時鐘、DDR 控制器、SD、QSPI 控制器初始化工作,再通過啟動模式查找bitstream 配置FPGA,然后搜索應用程序加載到DDR,最后交給應用程序執行。將FSBL 引導程序和整個工程生成的bitstream 文件放在一起,再生成一個boot.bin 文件放到SD 卡的根目錄下,將開發板設置為SD卡啟動模式,連上電源和顯示屏,打開電源開關,就能看到如圖7 的測試結果圖像。

Fig.7 Test results圖7 測試結果

7 結語

本文在Zynq-7000 開發平臺AX7Z020 上使用Xilinx Vivado 開發工具實現了CMOS OV5640 攝像頭采集數據,通過HLS 工具實現Sobel 快速邊緣檢測算法,通過Video In to AXI4-Stream 和AXI4-Stream to Video Out 將視頻信號在通用信號格式和AXI4-Stream 專用信號格式之間進行轉換,通過VDMA 實現視頻信號的3 幀DDR 緩存功能;通過自定義HDMI 輸出IP 將畫面顯示到顯示屏上,最終通過SDK 應用程序控制整個FPGA 工程運行。采用軟硬件協同的設計方法使系統更具有可控性和靈活性。同時,在該系統框架上可以很方便地進行圖像處理算法驗證和研究工作。

但是,本文只完成了整個視頻圖像處理數據流和控制流的設計工作,沒有在PS 和PL 硬件之間留出控制接口,因此當程序運行起來后無法通過PS 實時控制PL 端。下一步研究工作是在PS 端設計UI 界面,通過UI 來實時控制PL 端的工作情況,如此可以使得系統針對不同圖像問題執行不同的圖像處理算法,并在后續引入自動圖像評估和加載不同算法等功能。