超寬帶無線電監測接收機快速掃描的FPGA實現*

涂 建,董增虎

(1.中國電子科技集團公司第三十研究所,四川 成都 610041;2.成都凌德科技有限公司,四川 成都 610041)

0 引 言

無線電監測是對于無線信號的各項特征進行測量,而進行測量的前提是能夠準確地捕獲信號,對信號進行準確地采集并且測量。由此可見,更高的捕獲概率是關鍵技術之一,如何提升捕獲概率就成了各方亟須提升的關鍵技術點。快速掃描技術是提升信號捕獲概率的關鍵技術之一,超寬帶無線電監測接收機的掃描速度十分關鍵,對于用戶快速發現有效信號的作用十分巨大[1]。

傳統的無線電接收機采用軟件控制本振掃描的方法,可以實現的掃描速度指標在10 GHz/s左右;主要流程如圖1所示。

(1)CPU根據掃描的頻段計算響應參數;

(2)CPU在取得掃描參數后,CPU將控制參數發送給硬件和低速本振;

(3)CPU獲取頻譜信息;

(4)CPU獲取頻譜數據,至此一次掃描結束,后續轉至(2)繼續開始下一次掃描。

從掃描過程來看,硬件與中央處理器(Central Processing Unit,CPU)之間需要頻繁交互才能夠實現一次頻譜的掃描,其時間消耗是相當大的,即使對流程進行優化,掃描速率的提升也十分有限,故提升的關鍵點應該在于減少硬件與CPU之間的交互。本設計采用FPGA序列化器控制掃描流程和快速本振兩個關鍵技術來實現掃描速度的提升,實現了傳統掃描技術無法實現的掃描速度,在掃描速度技術上實現了突破,實現了無線電監測接收機掃描速度大于500 GHz/s。

1 系統結構

1.1 系統原理

寬帶無線電監測接收機主要由射頻模塊和數字模塊組成[2-3](見圖2)。射頻模塊包括通道單元和快速本振單元。通道單元實現信號濾波和通道切換的功能,快速本振單元實現本振的快速切換功能。通道單元包括通道輸入電路、一/二混頻器、一/二中頻濾波放大電路、射頻衰減與通道增益控制等組件;本振單元包括第一本振、第二本振、控制模塊、電源和狀態監測等組件。在本設計中,本振的切換時間小于 200 μs。

射頻接收單元對輸入的射頻信號進行放大、濾波、混頻等模擬域處理,將射頻信號轉換為中頻信號,供數字處理單元進行后續的信號處理。

數字處理單元由模數轉換單元、數字信號處理單元、大容量存儲單元、數據緩存單元、非易失性存儲單元、硬件看門狗電路、自動監測電路、連接器這8個關鍵組件組成。數字處理單元對輸入的模擬中頻信號進行模數變換、數字信號下變頻、快速傅里葉變換(Fast Fourier Transform,FFT)等信號處理。

數字處理模塊單元主要完成中頻信號的模數轉換(Analog-to-Digital Converter,ADC)信號處理、數字信號下變頻、快速傅里葉變換,以及處理后的信號數據的存儲、緩存或發送傳輸。

數字信號處理單元的核心部件是現場可編輯門陣列(Field-Programmable Gate Array,FPGA)+ARM,本設計采用ZYNQ SOC FPGA的架構,ZYNQ集成了高性能的FPGA和雙核ARM,其主要技術指標分為ZYNQ ARM主要性能指標和ZYNQ FPGA主要性能指標。

ZYNQ ARM主要性能指標如下。

(1)CPU頻率最高800 MHz。

(2)CPU核心數量2個,CPU類型為ARM Cortex-A9,32 kB一級緩存,512 kB二級緩存。

(3)16/32 bit DDR3/DDR3L/DDR2/LPDDR2存儲器接口;1 GB 8/16/32位寬存儲器。

(4)2個10/100/1000 Mb/s以太網接口,符合IEEE Std 802.3 和IEEE Std 1588 R2.0標準。

ZYNQ FPGA主要性能指標為以下5點。

(1)可編程邏輯單元444 kB,查找表(Lookup Talbe,LUTs)為277400,觸發器(Flip-Flop,FF)為554800。

(2)塊存儲器(Block Random-access Memory,BRAM)為26.5 MB。

(3)數字處理單元(Digital Signal Processing,DSP)為 2020。

(4)峰值數字處理性能(Peak Digital Processing Performance,PDPP)為 2622GMACs。

(5)高速外設組件互連(Peripheral Component Interconnect Express,PCI Express)接口為 Gen2 ×8。

本設計的關鍵在于快速本振的切換和序列化器的FPGA設計[4-5]。本文重點講解寫的序列化器的FPGA設計。

1.2 序列化器的FPGA實現

圖3為F P G A的實現框圖,其中包括序列化器模塊、射頻模塊(Radio Frequency Module,RFM)、FFT模塊、數據發送模塊。由于采用Zynq的架構,ARM與FPGA之間可以采用共享內存的方式進行交互,大大提升了數據傳輸的帶寬,降低了系統交互的延時,對于提升掃描效率有很大的益處。ZYNQ ARM與FPGA之間通過高性能/帶寬可擴展接口(Advanced eXtensible Interface-High Performance,AXIHP)進行海量數據的傳輸;AXI HP為FPGA邏輯資源(Program Logic,PL)的雙倍速率同步動態隨機存儲器(Double Data Rate Synchronous Dynamic Random Access Memory,DDR SDRAM)和片上存儲器(On Chip Memory,OCM)提供高帶寬的數據路徑,每個HP接口包括兩個先進先出(First Input First Output,FIFO)緩存,用于讀寫傳輸。PL到內存互連高速AXI HP端口路由連接到兩個DDR內存端口和一個OCM存儲器端口。AXI HP接口也被稱為AFI(AXI FIFO接口),以強調它們的緩沖功能。PL電平移位器必須通過LVL SHFTR EN啟用后,才能進行PL邏輯通信。ZYNQ ARM與FPGA之間的低速通信通過AXI Lite接口進行通信,主要實現對于FPGA內部寄存器的配置功能。

FPGA模塊與射頻模塊之間通過串行外設接口(Serial Peripheral Interface,SPI)總線進行通信,這里的SPI總線采用差分的設計方式,可以實現最高100 MHz的通信速率,實際應用中使用50 MHz作為通信速率。

圖3中模塊功能如下所述。

(1)序列化器模塊:實現掃描的關鍵模塊,實現快速掃描的掃描序列化控制。

(2)射頻SPI模塊:射頻模塊的SPI控制。

(3)FFT模塊:FFT采集轉換模塊。

(4)數據發送模塊:將掃面的FFT數據發送到微控制單元(Microcontroller Unit,MCU)。

序列化器模塊是本設計的關鍵,圖4為序列化器的FPGA內部模塊組成。序列化器模塊包括寄存器單元、序列化RAM、控制模塊、射頻控制單元、數據收集模塊等模塊。最終的數據交互采用共享內存的方式實現,由于設計采用的是Zynq架構,FPGA與ARM之間可以使用共享內存的機制來傳輸數據,大大節省了數據傳輸的時間,提升了掃描的速率。

寄存器單元是用來配置控制單元,下載控制序列到序列化RAM,啟動/停止掃描模塊。序列化RAM單元來存儲控制序列,實現控制序列的讀寫,這里采用的是一個雙口RAM來實現。數據采集模塊是用來收集FFT數據,負責啟動和停止FFT掃描,并將采集到的FFT數據通過AXI總線轉存到共享內存中,這個模塊也是序列化器的關鍵模塊,是負責采集的關鍵。射頻控制單元是接收控制序列中射頻控制碼,并將射頻控制碼發送給射頻單元。控制模塊實現了對于控制序列的執行控制,控制模塊從序列化RAM中讀取控制碼,識別控制碼后并進行分發。控制碼分為采集控制碼、射頻控制碼和延時控制碼3類。采集控制碼發送給數據收集塊,實現采集的控制;射頻控制碼發送給射頻控制單元,實現射頻的頻率、幅度控制;延時控制碼控制模塊內部的計時器模塊消耗,實現序列化中的延時功能。

1.3 序列化器的流程

序列化器的主要流程如圖5所示。

序列化器流程:

(1)MCU計算掃描需要的參數;

(2)MCU發送計算的參數給FPGA,序列化器接收到參數后,準備開始啟動掃描;

(3)FPGA控制快速本振,等待本振切換完成,并且穩定;

(4)開始FFT采集轉換;

(5)等待FFT采集完成;

(6)發送FFT數據至MCU,并且同時切換到下一個掃描頻段,準備下一次FFT采集;

(7)判斷是否已經掃描完成所有的頻段,如果是結束掃描,再進行下一個頻段的掃描。

1.4 掃描速度計算

當數據采集時間為0.04 ms,FPGA提供的硬件FFT可以實現8 192點的FFT計算,本振調諧時間小于0.2 ms,系統控制數據傳輸緩存等開銷時間小于0.05 ms,本振調諧時間和系統控制數據傳輸緩存開銷時間相加得到整體每次掃描一個頻點的時間則小于0.25 ms。按照160 MHz帶寬計算,理論上可以得到640 GHz/s的掃描速度[6],考慮到程序實現的實際控制延時變化按照80%計算,實際可以實現的掃描速率大于500 GHz/s。

2 測試結果以及結論

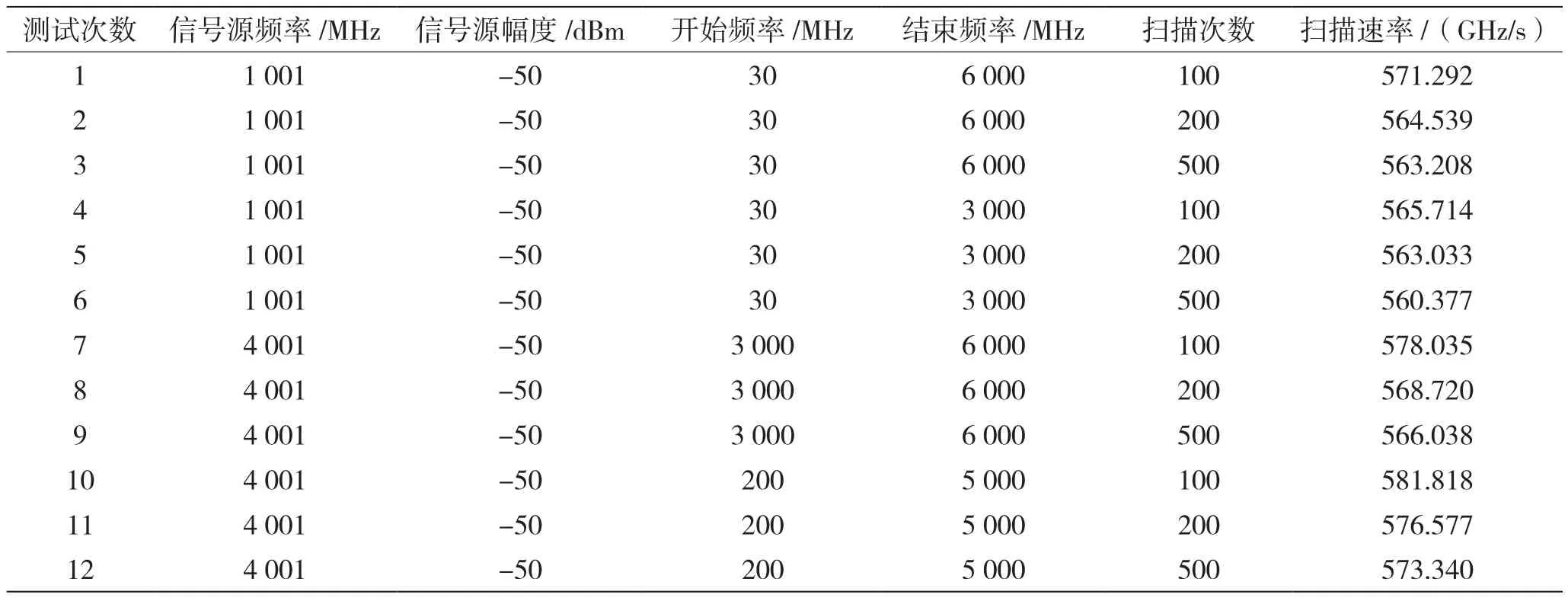

基于該原理設計了硬件平臺,并進行了詳細的測試,從不同帶寬和掃描次數進行了全面的測試。從表1的測試結果看,本文設計可滿足對于快速掃描的設計目標,實現了大于500 GHz/s的掃描速度,在實際應用中具有較大的實用價值,為無線電監測的應用提供了有力的支持。

表1 掃描速率測試結果

3 結 語

本文設計實現了無線電監測接收機快速掃描的FPGA方案和步驟,并對其過程中的步驟進行詳細地講解,最終實現了基于電荷泵快速切換技術的本振單元,實現了快速切換時間<200 μs;采用FPGA序列化器實現了掃描過程的精準化控制,加快掃描速度,實現快速掃描速度>500 GHz/s。