集成電路檢驗/失效分析過程芯片去層制備方法

汪小青,虞勇堅,馬 勇,劉曉曄,呂 棟

(中科芯集成電路有限公司,江蘇無錫214035)

1 引言

集成電路的芯片制造過程是通過掩模、光刻、離子注入、氣相沉積、電鍍、化學機械研磨(CMP)、腐蝕等多達幾十、上百道工序,在硅襯底表面生長出有著特定邏輯功能的物理圖形,這些物理圖形從材質上包括Al、Cu、Ti、TiN和W等金屬材料,以及單晶Si和多晶Si、SiO2和Si3N4等非金屬材料[1]。

集成電路在制造、試驗和應用過程中不可避免地會因為制造工藝、測試和環境應力、用戶使用、壽命損耗等各種因素發生失效[2]。失效分析工程師需要通過各種方法定位失效位置,查找失效原因,剖析失效機理,在失效分析過程中需要對失效的集成電路進行去層解剖分析。芯片去層制備是在了解集成電路芯片制造工藝的基礎上,采用化學腐蝕、機械研磨、離子刻蝕等技術手段逐層去除芯片各物理層次結構的過程。

在GJB548B-2005《微電子器件試驗方法和程序》方法2018.1“掃描電子顯微鏡(SEM)檢查”3.3節“樣品準備”中規定:“適用時,應采用不損傷其下層待檢查的金屬化層的腐蝕工藝(如化學或等離子腐蝕)去除芯片表面的玻璃鈍化層。”GJB4027A-2006《軍用電子元器件破壞性物理分析方法》和GJB5914-2006[4]《各種質量等級軍用半導體器件破壞性物理分析方法》4.3.5.4節“掃描電子顯微鏡(SEM)檢查”中,均將樣品制備的方法指向GJB548B-2005中的相應章節。在GJB3233-98[2]《半導體集成電路失效分析程序和方法》5.2.12和5.3.1.2.5節概要性地給出了去除鈍化層和PN結染色的方法。在以上標準中僅給出了對檢驗分析樣品的制備處理要求,并未提供具體的處理方法。除個別商業公司外,國內檢測機構很少具備集成電路芯片去層制備能力,并且因為商業秘密保護,可查詢獲取的相關資料很少,這就使得檢測機構在開展檢驗試驗或失效分析過程中缺乏參考依據,使得標準的相應內容缺乏可參考和可操作性。本文對集成電路芯片的物理層次進行了解剖分析,選用實際產品制備滿足檢驗要求和失效分析的各物理層次,樣品制備方法可以對GJB548B-2005、GJB4027A-2006以 及GJB3233-98進行補充,使其具有可操作性。

2 芯片的物理層次結構

芯片的物理層次結構從表面往下通常包括玻璃鈍化層(一般由Si3N4+SiO2構成)、所有金屬化層(Al或Cu)、所有的中間介質層(一般為SiO2及其包裹的通孔或接觸孔)、多晶(Polysilicon,一般簡稱Poly)層以及有源區層(襯底,大多為P型)。對于一個具有N層金屬布線的芯片來說,樣品制備過程中通常可以獲得N+2個用來觀察的物理層次,即N個金屬層、1個多晶層和1個有源區層。

在獲取用于觀察的物理層次時,需要選定一個合適的解剖層面,以保證樣片圖像中能夠同時觀察到多個層次信息。圖1為一個具有3層金屬、雙層多晶的集成電路芯片縱切面照片,當需要觀察第一層金屬(M1)及以下層次時,應在去除M2層后停止(圖中虛線位置),保留M1層上方的SiO2層和M1、M2層之間的通孔(W孔)。此時在光學顯微鏡下可以同時觀察到M1層、W孔(VIA12)及以下其他層次,這有助于判別失效發生的具體層次。

圖1 具有3層金屬布線的芯片物理層次結構(縱向切片)

3 去層制備方法

集成電路芯片的去層制備過程包括對表層玻璃鈍化層的去除、金屬化層的去除、阻擋層的去除、中間介質層的去除、底層多晶層的去除和有源區的制備。根據制造工藝和材料的差異,可以選用離子刻蝕、化學腐蝕和機械研磨等方法。

3.1 離子刻蝕法

離子刻蝕一般稱為干法刻蝕[3],去層制備過程最常用的是反應離子刻蝕(RIE),RIE的原理是輔助刻蝕氣體(如CF4、SF6)在工作腔體內電離后,在電場作用下與被刻蝕樣品之間發生的物理化學過程。RIE因氣體流量與腔體壓力不同,刻蝕效果可以是各向異性也可以是各向同性的。各向異性刻蝕使同一種材料沿單一方向均勻刻蝕(一般為平行電場方向),并因刻蝕氣體的選擇對不同材料具有不同的刻蝕速率,RIE較高的刻蝕選擇比能夠保留所需要的關鍵層次和圖形,見圖2。

圖2 RIE各向異性刻蝕

在去層制備過程中,去除集成電路芯片表面的玻璃鈍化層和中間介質層推薦選用離子刻蝕,這些層次的材質一般為Si3N4、SiO2。對于具有多層金屬化層的集成電路芯片,各層介質層的離子刻蝕時間可以通過介質層厚度與離子刻蝕速率之比計算獲取。

3.2 化學腐蝕法

化學腐蝕又稱為濕法刻蝕[9],是通過化學溶劑與芯片表面的材料之間發生的化學腐蝕反應,生成可溶性物質或氣體,達到去除芯片表面材料的目的,原理如圖3所示。

圖3 濕法刻蝕原理圖

影響化學腐蝕速度的因素主要有4個[5]:溶液濃度、反應時間、反應溫度和溶液攪拌方式。高的溶液濃度、反應溫度和溶液攪拌可以加快化學反應速度,但過快的腐蝕速度會發生嚴重的“底切”“鉆蝕”現象[6],導致難以控制腐蝕過程和終點,這就導致化學腐蝕法的應用局限性大大增加。

化學腐蝕法去層一般用于去除具有終點自停止的層次,例如去除具有阻擋層和W通孔的Al金屬化層。

3.3 機械研磨法

機械研磨去層法是3種去層方法中相對穩定的1種,是通過研磨機、研磨劑和拋光墊對芯片表面逐層去除的方法。相對于離子刻蝕和化學腐蝕法,機械研磨法具有更高的可控性,機械研磨法的另一個優點是檢驗和分析人員能夠在觀察過程中很好地識別區分層次,因處理后與上層金屬化層之間的通孔(W)呈現顯著的亮白色,而下層通孔(接觸孔)呈現暗色。

但是由于機械研磨法是同步去除芯片表面各區域和各類材料,并且局限于人工操作,對個人的技術要求更高。對于深亞微米芯片,金屬布線的材料、層數、線寬等是制約研磨去層通用性的因素。

4 去層制備試驗

本文以某型號集成電路芯片為例進行樣品去層制備試驗,該芯片具有3層鋁金屬化層,雙層多晶、0.35 μm工藝制程,玻璃鈍化層材料為Si3N4+SiO2的復合結構。

4.1 玻璃鈍化層的去除

玻璃鈍化層作為芯片表面的保護層,一般為Si3N4層和SiO2層的雙層次結構。推薦選用離子刻蝕(RIE)去除玻璃鈍化層,常見的輔助刻蝕氣體為CF4和O2的混合氣體,CF4對于SiO2和金屬鋁的刻蝕具有高選擇比,可以快速刻蝕SiO2而保留金屬鋁。經驗值為當射頻功率為80 W、CF4∶O2配比為2∶1、氣壓為15 Pa的情況下,刻蝕時間選擇3~5 min即可完全去除玻璃鈍化層。

反應化學過程見式(1)~(4)[7]。

在CF4的等離子體中加入少量O2,氧原子與CF4反應生成CO、CO2以及少量COF2,將消耗掉等離子體中的C原子,可以大大增加F原子濃度,從而加快對SiO2的刻蝕速率。

以圖1中的樣品為例,本次試驗中頂層Al金屬化層(M3)去除玻璃鈍化層前后的照片見圖4,去除玻璃鈍化層后M3裸露呈現亮白色。金屬化層之間的介質層成份一般為SiO2,介質層的去除可以同樣采用離子刻蝕法。

圖4 鈍化層圖像(左)與去除鈍化層后的圖像(右)

4.2 金屬化層的制備和去除

金屬化層的制備和去除分為Al和Cu兩種金屬化層的制備和去除。

對于采用鋁作為金屬化層的集成電路,推薦采用離子刻蝕法去除玻璃鈍化層(Si3N4+SiO2)和金屬化層中間的SiO2介質層后,再通過以下兩個步驟完全去除金屬化層。以圖1中案例為代表說明制備和去除M2層、M1等中間金屬化層的步驟。

4.2.1 化學腐蝕

圖4 的案例通過離子刻蝕暴露出頂層Al金屬化層(M3)后,可以采用化學腐蝕法去除金屬化層,腐蝕液一般采用商品鋁腐蝕液或者稀釋后的30%硫酸(H2SO4)或30%鹽酸(HCl),以上腐蝕液均可有效去除Al而不腐蝕SiO2介質層,Al與鹽酸反應的化學方程式為[6]:

反應過程中產生的氣泡會附著在鋁的表面,有可能局部抑制刻蝕的進行,造成刻蝕不均勻,可以在反應過程中通過增加攪拌或震動來避免或減輕刻蝕不均勻的問題。當M3層的金屬Al完全腐蝕后露出下方的Ti/TiN阻擋層時自動停止。

4.2.2 研磨去層

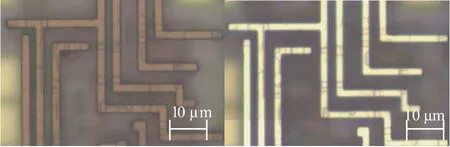

阻擋層的材質一般為Ti/TiN,去除阻擋層可以采用離子刻蝕也可以采用機械研磨法,推薦采用機械研磨法去除阻擋層,圖5為光學顯微鏡(OM)下0.35 μm制程的芯片M1金屬化層的研磨法制備效果圖。

圖5 0.35 μm工藝M1層圖像(OM)

對于0.18 μm以下采用Al或Cu工藝制程的集成電路芯片,一般全程采用機械研磨法制備中間所有的層次,當需要通過掃描電子顯微鏡(SEM)觀察Al或Cu金屬化層表面損傷或異常形貌時,則在去除上層金屬化層后,采用低氧或無氧離子刻蝕去除SiO2介質層直至下層金屬化層裸露,經表面蒸鍍導電材料后在SEM中進行失效位置觀察和識別。圖6為0.18 μm工藝制程金屬化層制備的SEM實際效果圖。

圖6 0.18 μm工藝M1層圖像(SEM)

4.3 多晶硅層的制備和去除

集成電路芯片上的多晶硅層一般用來制備CMOS管的柵極、電阻或者電容的極板。多晶硅層的制備推薦采用化學腐蝕法配合機械研磨法,化學腐蝕法去除金屬化層(M1),機械研磨法去除金屬化層下的阻擋層,可以保證多晶層和接觸孔的制備效果。圖7為集成電路芯片內部的多晶層數字單元照片,要求制備后的多晶柵極邊界、接觸孔、有源區邊界等關鍵位置無損傷、易區分。

圖7 多晶硅層制備效果圖

多晶硅層的去除主要采用化學腐蝕法,利用稀氫氟酸(HF)溶液進行刻蝕,反應過程為:HF將多晶硅層上下的SiO2介質層腐蝕掏空,多晶硅從芯片表面自然掉落去除,刻蝕速率可通過氫氟酸與去離子水的比例來調整。其化學反應方程式為[7]:

4.4 有源區層的制備

CMOS集成電路的數字單元是由PMOS管和NMOS管耦合組成,對于P型襯底硅集成電路,NMOS管直接在襯底上生長,而PMOS管則生長在N型阱內。在樣品制備過程中,有源區層可以通過PN結染色法來制備,可以區分出P型襯底、PMOS管、NMOS管、N阱區邊界。這是由于PN結染色液對P型注入區刻蝕較快并腐蝕出微孔洞,微孔洞產生光陷阱效果而呈現深色,而N型注入區由于刻蝕速率慢、表面保持光滑而呈現出白色,兩者之間對光照呈現顯著的反射率差異,造成顏色上的反差[8]。

GJB3233-98《半導體集成電路失效分析程序和方法》第5.5.1.2.5磨角染色中給出了PN結染色顯示液的配方,見表1。

表1 PN結染色方法

實踐證明Cu染色液配方在操作過程中不易控制,推薦采用Dash腐蝕液配方可以獲得更好的染色效果,通用性也更好[6]。

實際上,PN結染色技術不僅可用于判斷CMOS管和阱區邊界,還適用于P-、P+和N+等輕、重摻雜濃度區域的定性判斷。PN結染色技術同樣適用于模擬元件的區分和提取,例如PNP晶體管、NPN晶體管和阱電阻識別。圖8給出了數字單元有源區的阱及MOS管的染色效果。

圖8 有源區PN結染色制備效果圖

綜上所述,在芯片去層制備方法中,離子刻蝕法適用于去除玻璃鈍化層(Si3N4+SiO2)和金屬化層中間的SiO2介質層,機械研磨法適用于金屬化層和阻擋層的去除;多晶硅層的制備推薦采用化學腐蝕配合機械研磨法,PN結染色推薦選用Dash腐蝕液進行刻蝕。

5 總結

本文探討了集成電路芯片內部各層次的去層制備方法,為滿足集成電路檢驗和失效分析對芯片內部各層次的制備需求,分別從玻璃鈍化層去除、金屬化層制備與去除、多晶層制備與去除、有源區染色4個方面提出了具體的制備方法,通過實例說明了選用離子刻蝕、化學腐蝕和機械研磨法的物理層次、材料和試驗條件。本文的成果為GJB548B-2005、GJB4027A-2006以及GJB3233-98中相應檢驗和分析過程提供了具體實施方法,有助于推動標準中相應條款的實際應用。