基于FPGA的數碼噴墨印花系統

力雪梅,季誠昌,孫以澤

(東華大學機械工程學院,上海 201620)

數碼噴墨印花對印花圖片的數據處理速度、進布與噴頭小車運動控制有較高要求。市面上的數碼噴墨印花系統采用ARM 處理器處理印花圖片數據,控制印花過程,效果較好,但處理速度較慢。因此需開發可滿足高速印花數據處理與較好控制效果的系統架構。FPGA 為現場可編程門陣列,能解決定制電路不足的問題,克服原有可編程器件門電路數有限的缺點,使硬件易于操作,應用于數碼噴墨印花系統時能簡化系統結構。本研究以PC 機與FPGA 技術相結合處理印花圖片與控制印花過程。

1 數碼噴墨印花系統架構

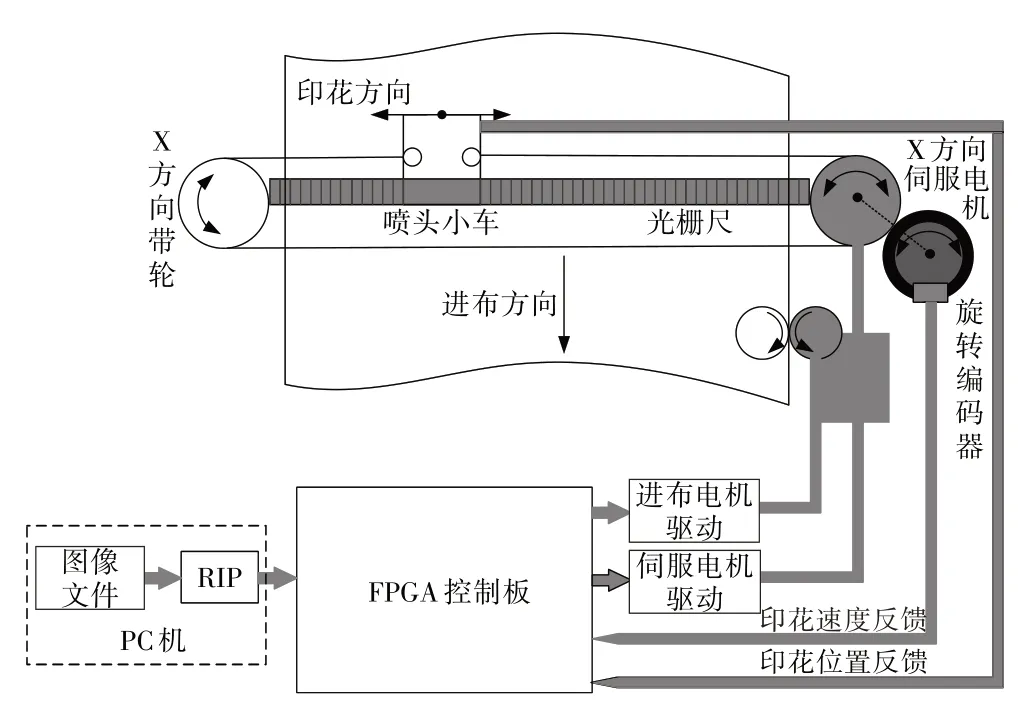

數碼噴墨印花首先將計算機或印前輸入設備產生的彩色圖文信息傳遞到噴墨設備,在計算機控制下計算相應的通道墨量,噴墨成像裝置控制墨滴以一定速度由噴嘴噴射到承印物表面,最后通過油墨與承印物的相互作用,使油墨在承印物上再現穩定的圖文信息[1]。數碼噴墨印花系統整體架構如圖1 所示。從計算機獲取待印花圖像,利用PC 機完成前期處理,生成可用于印花的圖片數據格式,FPGA 控制板接收圖像信息并控制印花噴頭,驅動噴頭與進布機構相互配合進行印花。

圖1 數碼噴墨印花系統的整體架構

為保證印花精度,需要保持噴頭印花速度與進布速度同步。采用伺服電機控制進布,控制板根據印花速度和位置的反饋信號相應調整伺服電機的轉速與印花速度匹配,完成打印。本系統主要通過設計FPGA 控制板的軟硬件完成圖像前期處理、數據傳輸與存儲,控制噴頭實時噴墨印花等,確保系統在噴墨印花過程中穩定、準確地還原印花圖像,精準印花。

2 數碼噴墨印花系統的需求

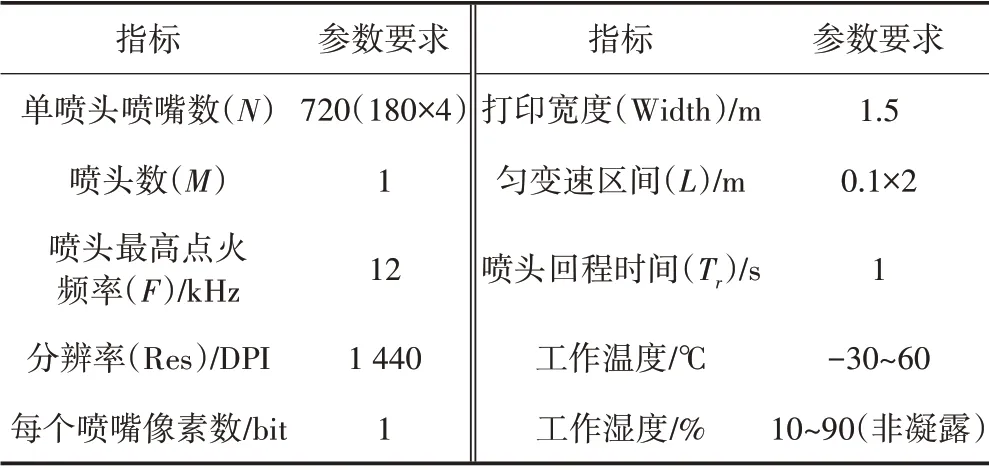

了解系統需求是系統設計的前提。由表1 可知,印花過程中,噴頭在印花介質兩端存在勻變速階段,使噴頭在開始印花時達到正常的噴印速度,結束印花時速度減慢,每個勻變速區間長度為0.1 m,因此每一行的勻變速區間長度=0.1 m×2=0.2 m。在一行印花數據噴印完成后,噴頭需回程并開始下一行噴印,為了提高印花效率,應盡可能提高噴頭的回程速度,縮短回程時間。不同印花系統因結構與控制方法不同,噴頭回程時間不同。在本印花系統中,噴頭回程時間為1 s,相比其他印花系統時間較短。噴頭在勻變速區間及回程中不噴墨,只在勻速期間噴墨印花。

表1 系統噴印參數要求

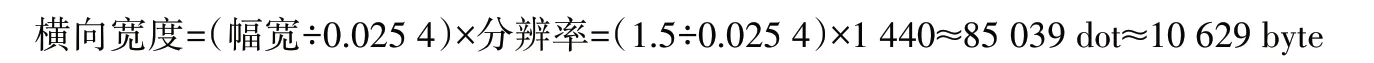

數碼噴墨印花系統設計主要體現在圖片數據容量及數據傳輸速率兩個方面。本系統用一個四色噴頭進行印花,由表1可知,打印寬度(印花幅寬)為1.5 m,則一次掃描中,印花橫向寬度計算式[2]如下:

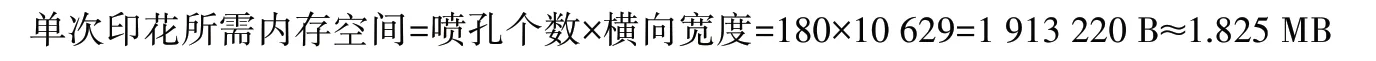

本系統采用的印花噴頭每列含有180 個噴孔,因 此單次印花所需內存空間計算式如下:

一個四色噴頭一個印花行程所需內存空間計算式如下:

在實際印花過程中,為保證印花數據不丟失,數據傳輸與存儲準確,系統選用的存儲器應大于以上數值且有富余,便于日后系統的調試與升級。

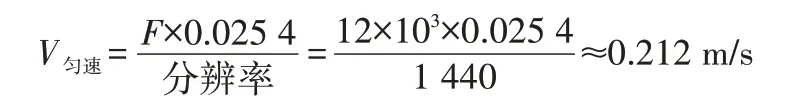

在系統運行過程中,光柵頻率應小于噴頭最高點火頻率F,因此,噴頭小車勻速運動的最快速度(V勻速)計算式如下:

噴頭在噴印單行印花圖片時所需的時間(T單行)計算式如下:

印花圖片處理系統需要在單行印花的9.96 s 內完成下一行印花數據的處理與傳輸,同時做好數據準備。因此,要確保印花數據的傳輸速度大于圖片數據的輸出速度,印花圖片數據處理最低速度(Vs)的計算式如下:

在設計數碼噴墨印花系統時,除了使系統滿足以上圖片數據容量及數據處理、傳輸速度要求外,還應使系統的運行具有較高的穩定性及可靠性。

3 硬件設計

在數碼噴墨印花系統中,FPGA 模塊的主要功能是利用USB 接口接收PC 機處理后的印花圖片數據,并進行圖像數據存儲、讀取等處理,然后將圖像數據同步傳輸到印花噴頭接口進行噴印,故FPGA 控制板的硬件模塊設計主要包括對USB、DDR3 SDRAM、SPI FLASH 以及噴頭驅動模塊等的電路設計和整合。FPGA 控制板具體硬件結構框架如圖2所示。

圖2 FPGA 控制板硬件結構示意圖

圖2 中,SPI FLASH 為控制板上電時存儲啟動代碼,上電啟動后,噴墨印花圖片數據通過USB 傳輸給FPGA 控制板接收器并緩存在DDR3 SDRAM 中,待印花小車達到某印花行時,通過FIFO 將該行印花數據輸出給印花噴頭,噴頭驅動模塊驅動噴頭進行噴印處理,蜂鳴器與指示燈狀態反應印花系統運行狀態。

3.1 電源電路

電源的電路根據FPGA 控制板上各個模塊以及芯片的具體需要設計。本系統選用的芯片主要包括FPGA 芯 片XC6SLX16、USB 芯 片CY7C68013A-56、DDR3 SDRAM 芯片MT41J64M16LA-187E 以及D/A轉換芯片AD5424 等,供電電壓分別為1.14~1.26 V、3.00~3.60 V、1.50 V、2.50~5.50 V,結合供電電壓設計針對性的電源電路。

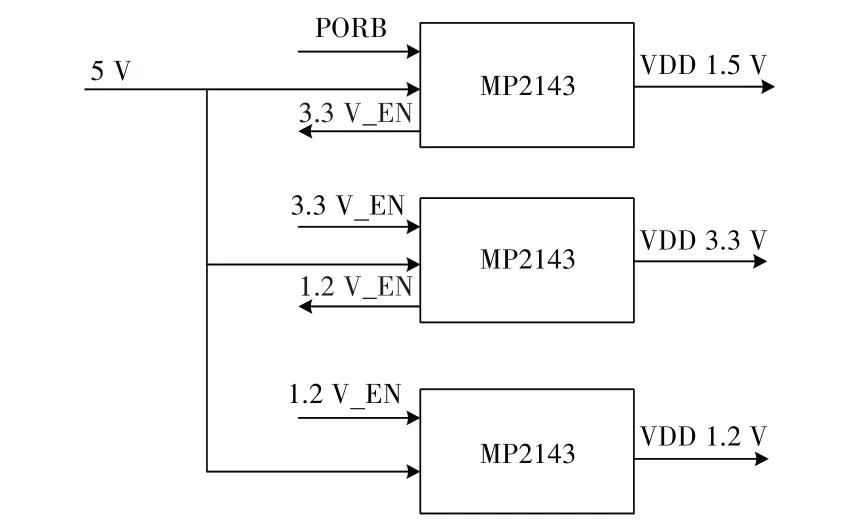

選用5 V 直流電源為電路板提供供電電壓信號。通過電壓轉換芯片將5 V 直流電源轉換成本系統芯片所需的1.5、3.3、1.2 V 等電壓信號。選用MPS 公司的開關電源MP2143 實現電壓轉換,輸入電壓可以為2.5~5.5 V,最大能支持3 A的負載電流,開關頻率可達1.2 MHz[3]。MP2143 有兩個管腳(上電使能管腳EN、電壓輸出正常時指示管腳PG),通過對兩個管腳的控制可以控制其上電時序,具體電壓分配如圖3所示。

圖3 電源模塊分配示意圖

由圖3 可知,以5 V 直流電源作為MP2143 輸入電壓,3.3 V_EN、1.2 V_EN 分別為3.3、1.2 V 電壓信號的使能管腳,經MP2143 轉換后,分別生成系統所需的1.5、3.3、1.2 V 電壓信號。

3.2 SPI FLASH

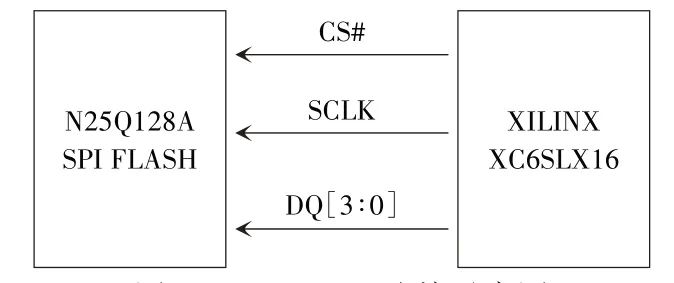

FPGA 控制板在上電啟動時需要從外部存儲來加載代碼。本系統采用SPI FLASH 作為外部存儲器,成本較低,電路設計也更加簡單,但是讀寫速度比總線FLASH 慢[4]。本系統對FPGA 控制板的啟動加載速度沒有特定要求,因此選用成本更低的SPI FLASH 作為程序存儲器。

FPGA 啟動代碼存儲器采用N25Q128A FLASH芯片(Micron 公司),容量大小為128 Mb,最高可以支持108 MHz的時鐘頻率。N25Q128A SPI FLASH 與XILINX XC6SLX16 芯片的連接如圖4 所示,通過對引腳的配置最終實現FPGA 從SPI FLASH 啟動。

圖4 SPI FLASH 連接示意圖

3.3 噴頭驅動

在實際的數碼噴墨印花過程中,FPGA 控制板在接收PC 機預處理的圖片數據后,同時產生兩路信號,其中一路信號將噴印數據與控制命令發送給噴頭接口模塊進行印花,另一路信號為高壓點火脈沖,但FPGA 控制板產生的信號為數字信號,需通過D/A轉換芯片轉換成模擬信號以輸出印花噴頭工作時所需的高壓點火脈沖[5],數碼噴墨印花系統的噴印噴頭驅動控制電路模塊構成如圖5所示。

由圖5 可知,噴印噴頭的驅動控制電路模塊主要由FPGA 模塊、D/A 轉換模塊、功率放大器模塊、噴頭接口模塊構成。其中,D/A 轉換模塊主要負責將FPGA產生、用數字串表示的高壓點火脈沖信號轉換成可被噴印噴頭識別的模擬信號,再將該信號發送給功率放大器,最后將放大后的電壓信號發送給噴印噴頭進行點火印花。

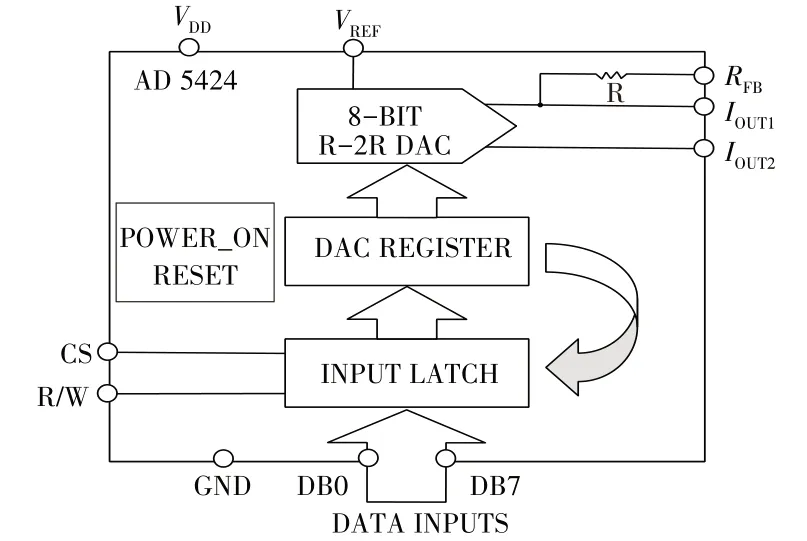

選用芯片AD5424 作為系統D/A 轉換芯片,適用于2.5~5.5 V 的電壓環境,是8 位電流輸出數模轉換器(DAC),其轉換后的輸出信號為電流信號。系統選用壓電式噴印噴頭,因此,選用驅動能力較好的SN10501芯片能將電流信號轉換成電壓信號。AD5425 型D/A轉換器功能圖如圖6所示。

圖6 D/A 轉換器功能圖

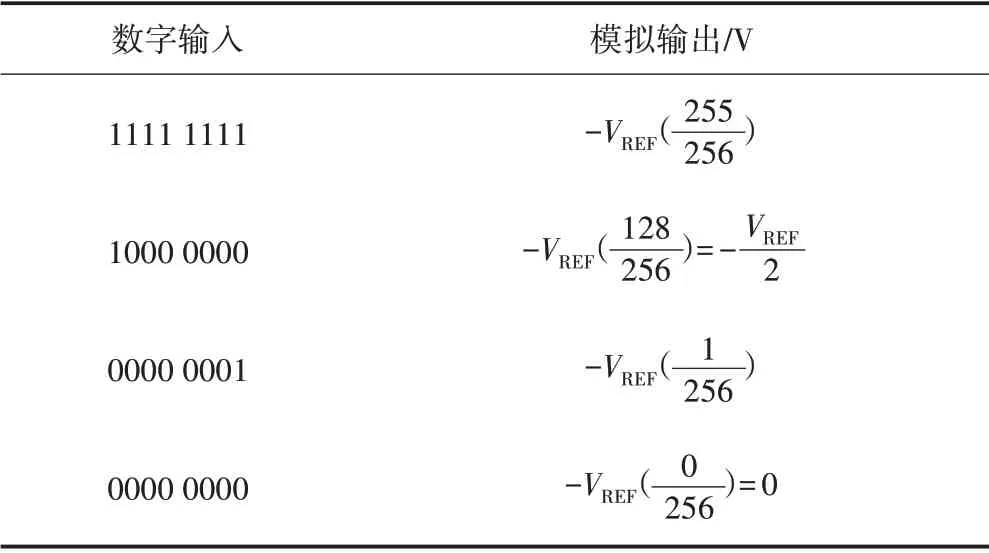

圖6 中,IOUT1代表經D/A 轉換器轉換后輸出的電流,IOUT2一般連接系統的模擬地,GND 代表接地引腳,RFB表示反饋電阻的接入引腳,VDD表示輸入引腳的供電電壓,VREF為輸入的參考電壓,DATA INPUTS 為數據輸入端口,DB0~DB7 為數字輸入端口,單極代碼表如表2所示。

表2 單極代碼表

表2 反應了數字輸入編碼與對應輸出電壓間的關系,噴頭點火脈沖信號經D/A 轉換器轉換后生成模擬信號,但高壓點火脈沖波形功率較小,達不到驅動噴頭點火所需的規定值,因此需將信號發送給功率放大器模塊放大。用OPA548 型功率放大器,可接受的單端供電電壓為8~60 V,可輸出較寬的電壓波動。

4 軟件設計

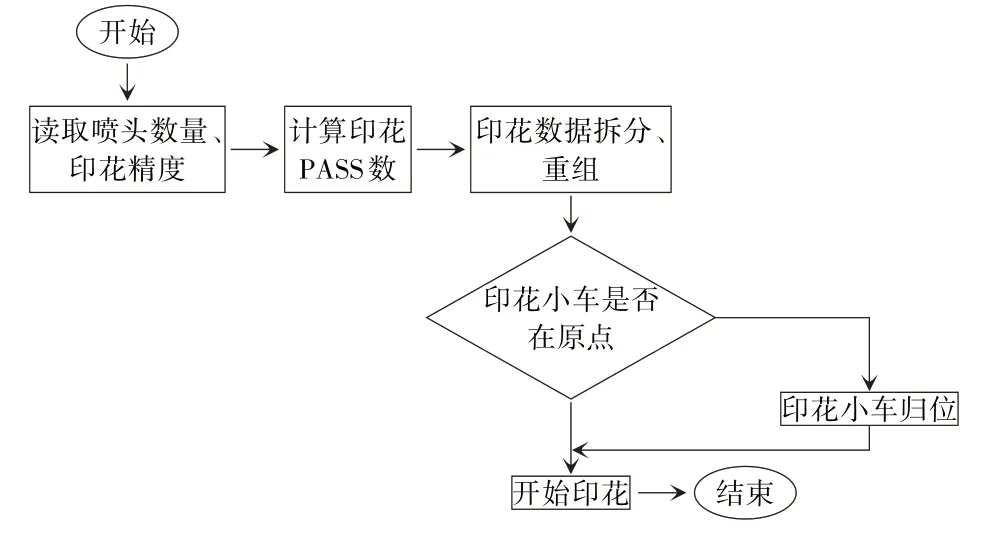

數碼噴墨印花系統的軟件實現主要包括印花圖片的數據處理及印花過程控制。印花過程控制包括讀取印花圖片信息、設置印花參數,根據印花參數對圖片進行數據處理、設置印花起始點,接收單次印花行程數據后進行X 方向的點火印花,完成該印花行程后進行Y 方向的進布操作,再進行下一行程點火印花。具體控制過程如圖7所示。

圖7 印花控制過程

印花圖片數據處理過程如圖8 所示。開始印花時,讀取噴頭的數量及印花精度要求,按照讀取數據計算印花PASS 數,根據計算結果對印花圖片數據進行拆分、重組,生成印花噴頭能識別的點陣信息[6],調整噴頭小車的位置開始印花。

圖8 印花圖片數據處理過程

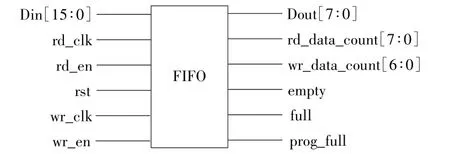

在某一行印花行程中,讀取該行的印花數據需通過FIFO 模塊保證印花圖片數據的發送與印花進程同步。本系統采用XILINX 公司的FPGA 芯片,其內部提供大量的存儲資源,通過這些存儲資源可生成FIFO存儲邏輯,進行深度以及位寬配置[7]后,利用ISE 開發平臺的IP 核生成項設計異步FIFO 模塊,生成FIFO模塊示意圖如圖9所示。

圖9 FIFO 模塊接口示意圖

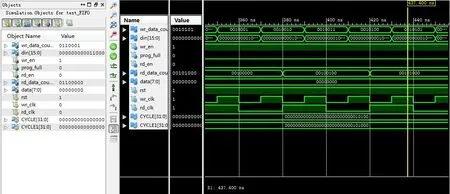

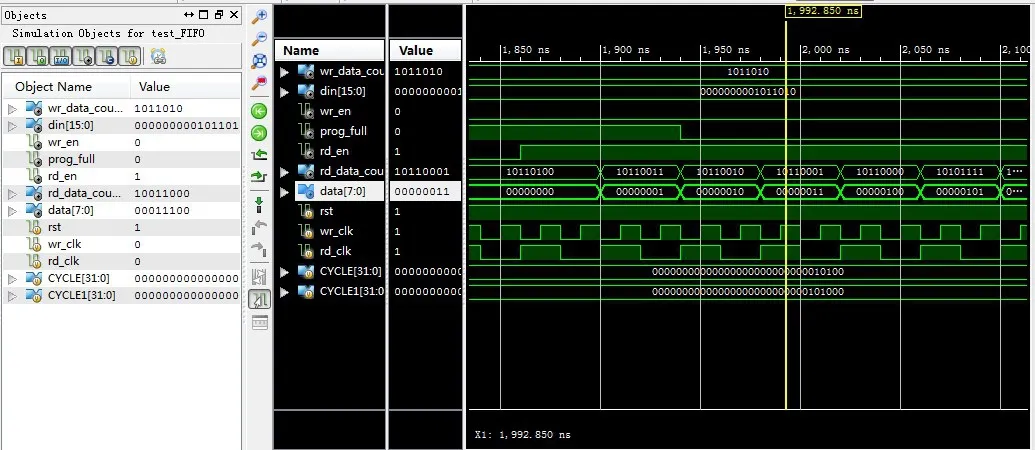

設置好FIFO 模塊后,對其讀寫操作進行仿真驗證。選用的印花噴頭每列含噴孔180 個,一次印花數據量為180×8 bit,因此,在進行位寬為16 bit 的寫操作時,為保證寫入數據量與一次印花數據量同步,將可編程滿信號prog_full門限定義為90(寫入數據達到90)時有效,此時不能再對FIFO 模塊進行寫操作。對FIFO 模塊進行寫數據仿真,結果如圖10所示。

由圖10 可知,在對FIFO 模塊進行寫入數據時,寫入使能置一,當數據量達到prog_full 的門限值90(一次印花數據已全部被寫入)時,prog_full 值被置1,不能再對FIFO 模塊進行數據寫入操作,保證一次印花數據大小與實際印花所需大小相同。

圖10 FIFO 模塊寫數據仿真

由圖11 可知,在讀使能rd_en 被置1 后,對FIFO模塊進行讀取數據操作,同時,代表可讀數據量的rd_data_count 值也在減小,直到將FIFO 內的數據全部讀出為止。

圖11 FIFO 模塊讀數據仿真

5 實驗驗證

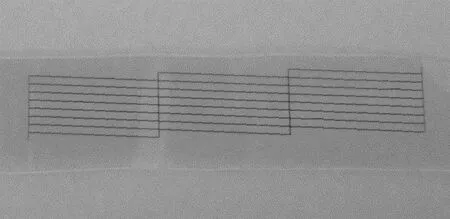

基于本文設計的數碼噴墨印花系統,在完成整體設計后對整個系統進行實驗驗證,測試其運行過程,分析其印花效果。影響最終印花質量的因素有很多,例如印花時室溫較低、噴墨墨管不干凈、保養不當、印花數據丟失等都會影響最終印花效果。針對上述情況,清洗印花機的噴墨管,對出現堵塞的噴頭進行吸墨清洗,以保證印花環境適宜,印花實驗結果如圖12 所示。由圖12 可知,各測試線條均排列整齊,未出現斷裂、錯位及消失等缺陷,且印花線條連續,印花不缺失,印花質量較高,由此可推斷,在印花過程中,各噴孔噴墨順暢并無堵塞。

圖12 噴嘴狀態測試條

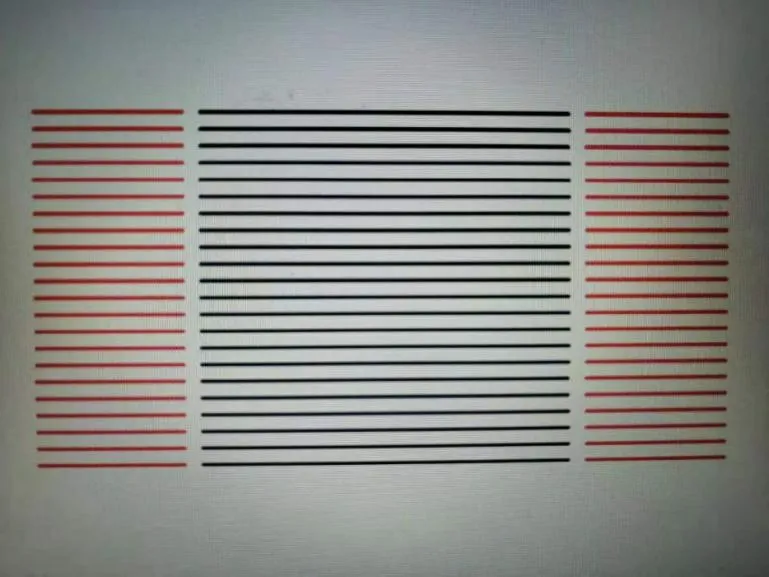

在保證各噴嘴狀態良好的情況下,還需對噴頭平行度進行測試,主要是為了保證在水平方向上,噴頭與噴印小車的導軌保持平行,否則會導致同一行噴嘴的不同顏色不在同一直線上,影響最終的印花質量。噴頭平行度測試條如圖13 所示,當噴頭與噴印小車的導軌不平行時,黑色與紅色線條不在同一直線上,此時可以調節噴頭架上的微調器,直到在同一直線上為止。

圖13 噴頭平行度測試

完成以上測試后對噴墨印花機進行整圖印花測試,結果如圖14 所示。印花圖片寬幅1.5 m,印花精度360×720 DPI。從印花結果可以看出,該數碼噴墨印花機可以滿足工業生產需求。

圖14 印花機整圖測試

6 結語

印花圖片的數據處理以及印花過程控制影響最終的印花質量,因此要求印花圖片的數據處理系統能夠準確、快速地對印花圖片數據進行拆分、重組,最終生成可供印花的圖片數據的點陣信息形式。針對印花過程中的數據處理與控制過程進行基于FPGA 的軟硬件設計,并對相關模塊進行仿真分析。調試與實驗驗證表明該噴墨印花系統可對圖片數據進行高效傳輸,并且能準確地用于印花工作。