一種寬溫度范圍的低溫度系數帶隙基準源設計

安景慧,吳晨健

(蘇州大學 電子信息學院,江蘇 蘇州 215000)

近年來,物聯網飛速發展,其產品已涉足工業監控、智能家居、運輸物流、智慧醫療等多個領域,實現了萬物廣泛互聯、人機深度交互,改變了人們的生活、工作和娛樂方式。半導體芯片是物聯網產業鏈不可或缺的重要部件之一,隨著物聯網應用場景越來越多樣化,芯片的精度和可靠性成為急需解決的問題。

帶隙基準源是物聯網系統中模擬芯片和數模混合芯片的基本組成單元,其主要作用是輸出一個不受工藝、電源電壓和溫度變化影響的穩定電壓。評判帶隙基準源性能好壞的指標有溫度系數、電源抑制比、直流功耗、面積等。指數曲率補償、對數曲率補償等各種曲率補償技術被用來改善輸出基準電壓的溫度特性[1-2],從而降低帶隙基準源的溫度系數。但是這些電路通常只能在-40 ℃~125 ℃甚至更窄的溫度范圍內工作,無法滿足軍工級芯片的要求。線性穩壓器、套疊電流鏡等電路結構被用來提高帶隙基準源的電源抑制比[3-5]。亞閾值設計、襯底驅動技術等被用來減小帶隙基準源的直流功耗[6-8]。然而這些電路在優化電源抑制比、減小直流功耗的同時犧牲了電路的溫度系數。

針對工作溫度范圍較大的物聯網應用場景對芯片溫度適應能力及可靠性的要求,筆者設計了一種在寬溫度范圍內正常工作的低溫度系數帶隙基準源電路,同時兼顧了電源抑制比和功耗等其他性能。基于改進后的Banba型帶隙基準源結構,電路利用工作在亞閾值飽和區晶體管的漏電流特性對雙極性晶體管的基極發射極電壓進行高階溫度補償,降低電路的溫度系數。利用分段溫度補償技術對較高溫度范圍內輸出基準電壓作進一步曲率補償,擴展整個電路的工作溫度范圍。

1 改進的Banba型帶隙基準源電路分析

傳統的Banba型帶隙基準源利用運算放大器的鉗位功能確保兩點的電勢相等[9]。這要求運算放大器具有較高的增益,從而增加電路的功耗和復雜性,且運放的失調會影響輸出基準電壓的精度。因此,筆者提出了無運放的Banba型帶隙基準源電路結構,如圖1所示。

圖1 低溫度系數帶隙基準源整體電路圖

晶體管NM9、NM10、PM7~PM10組成套疊威爾遜電流鏡,該結構輸出阻抗大,電流傳輸精度高,其功能是保持A、B兩條支路的電流大小相等以及A、B兩點電壓相等。電阻R2和R3的阻值相同,則流過兩電阻的電流相等,可以表示為

(1)

套疊電流鏡PMOS晶體管寬長比相等,不考慮溝道長度調制效應,則三條支路的電流大小相等。若晶體管Q1和Q2的發射極面積之比為1∶N,則流過電阻R1的電流為

(2)

其中,VT為熱電壓,等于kT/q,k是玻爾茲曼常數,值約為1.38×10-23J/K;q為電荷量,值約為1.6×10-19C。

電流IC具有負溫度系數,電流IP具有正溫度系數。電流IC和電流IP通過電流鏡鏡像到輸出電路,通過電阻RL轉換為輸出基準電壓Vref,其表達式為

(3)

通過調節R2和R1的比值以及N,可以實現對VEB1的一階溫度補償。

2 低溫度系數帶隙基準源設計

2.1 高階溫度補償電路設計

理論上,改進的Banba型帶隙基準源電路可以產生一個零溫度系數的輸出電壓。但是,雙極性晶體管的基極-發射極電壓的溫度特性具有高階非線性,其表達式為[10]

(4)

其中,Vg0是0 K時硅的帶隙能量,值約為1.12 eV;T為任意溫度,Tr為某一特定溫度;η和α分別為載流子遷移率和集電極電流的溫度依賴階數。

式(4)中的第3項表明了VBE的高階非線性。為了簡化分析,將式(4)以泰勒展開,得到

VBE=VG(Tr)-bT-cT2-… 。

(5)

當溫度在150 K(-123 ℃)到400 K(127 ℃)之間時,VG(Tr)在1.178 85 V到1.205 95 V之間變化,b介于9.025×10-5到2.733×10-4之間,c介于3.05×10-7到0之間。為了降低高階溫度項對輸出基準電壓的影響,設計了高階溫度補償電路,如圖1所示。

當晶體管的柵源電壓小于其閾值電壓但大于其本征電壓時,半導體表面已經反型,所以當外加漏源電壓后,MOS管也能導電,只是少子濃度較小,MOS管處于亞閾值區,對應的電流稱作亞閾值電流(I),表達式為

(6)

其中,C0是單位面積氧化物電容,μ是溝道載流子的有效遷移率,W/L是MOS管的寬長比,m和n是工藝相關的參數,VDS是晶體管的柵源電壓。當VDS≥4VT時,式中含VDS的項可以被忽略。

晶體管NM13和NM14工作在亞閾值飽和區。忽略晶體管體效應,根據式(6)可以得出流過電阻R4的電流為

(7)

其中,參數n不僅與工藝相關,也是溫度T的函數。將n用泰勒級數展開,n與溫度T的關系可以表示為

n(T)=E+FT+GT2,

(8)

其中,E、F都是正的常數。假設[(I14/I13)(W/L)13/(W/L)14]=α(α>1),將式(8)代入式(7)中,得到高階溫度補償電流IH的表達式為

(9)

從式(9)可以看出,電流IH具有正溫度系數的高階項,通過電流疊加可以實現對電壓VBE的高階溫度補償。

2.2 分段溫度補償電路設計

與一階溫度補償相比,經過高階溫度補償的帶隙基準源輸出電壓曲線通常接近正弦曲線,輸出電壓的溫度特性得到改善。隨著溫度的升高,輸出電壓會急劇增大;為了擴展帶隙基準源的工作溫度范圍,設計了分段溫度補償電路,如圖1所示。

電流IC,PW是由雙極性晶體管Q3產生的CTAT電流,電流IP,PW是通過電流鏡鏡像得到的PTAT電流。若定義電流IP,PW等于電流IC,PW時的溫度為TPW。當溫度低于TPW時,IP,PW小于IC,PW,節點Z的電壓降低,導致晶體管NM7工作在線性區,NMOS電流鏡中沒有電流流過。當溫度高于TPW時,IP,PW大于IC,PW,節點Z的電壓上升,從而在NMOS電流鏡產生補償電流IPW,其表達式為

(10)

2.3 整體電路設計

筆者提出的低溫度系數帶隙基準源由啟動和偏置電路、改進的Banba型帶隙基準源核心電路、高階溫度補償電路以及分段溫度補償電路組成,如圖1所示。

最終的輸出參考電壓等于總補償電流ICOM乘以負載電阻RL。總補償電流ICOM是電流IC、電流IP、高階補償電流IH和分段補償電流IPW的線性加權總和。因此,輸出參考電壓可以表示為

VREF=RL[k1(IC+IP)+k2IH+k3IPW]=RL[k1(IC+IP)+k2IH+k3(IP,PW-IC,PW)]。

(11)

通過改變權重k1、k2、k3可以使電路在寬溫度范圍內實現低溫度系數,且電壓值可以通過改變電阻RL進行調節。

3 芯片測試結果與分析

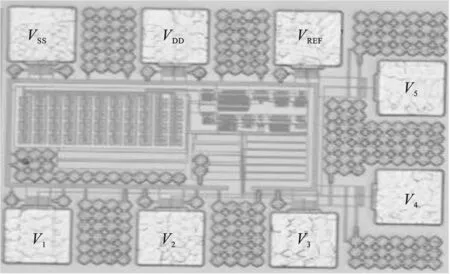

利用Cadence Spectre仿真軟件對提出的帶隙基準源電路進行了前仿真、版圖設計以及后仿真,最終采用TSMC 180 nm CMOS工藝進行流片。芯片顯微鏡照片如圖2所示。

圖2中V1~V5為電阻修調網絡控制開關焊盤,VREF、VDD、VSS分別為輸出參考電壓、電源、地焊盤,芯片核心面積為0.025 mm2。將帶隙基準源裸片用金線鍵合到測試PCB 板上,封黑膠加以固定,再對芯片進行測試。芯片測試環境如圖3所示。

圖2 帶隙基準源芯片顯微鏡照片

圖3 芯片測試環境

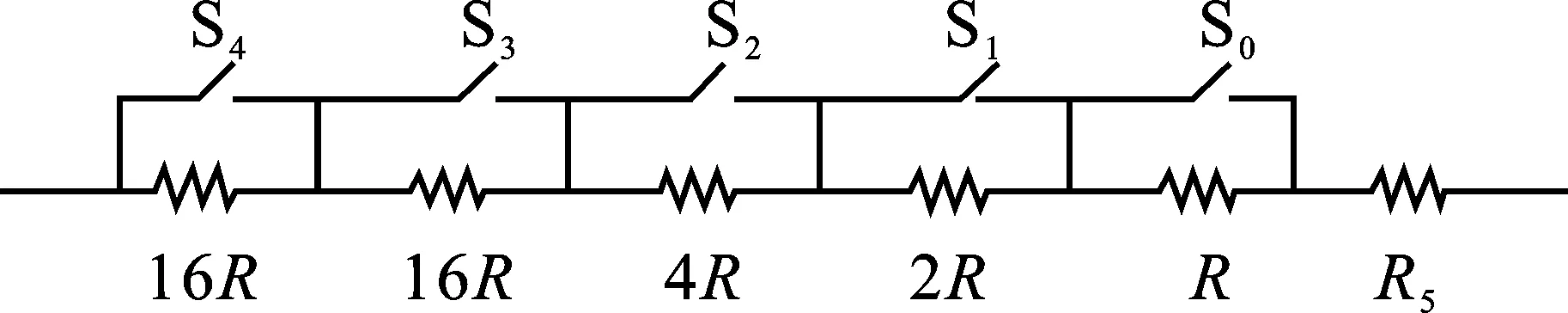

圖4 電阻修調網絡

為了減小工藝角變化對輸出基準電壓的影響,設計了一個5位電阻修調網絡,如圖4所示。通過控制開關S0~S4的開閉實現對電阻R5的修調,從而使帶隙基準源在較高溫度范圍內仍具有良好的溫度特性。當開關斷開時,修調電阻與電路串聯,分段補償電流IC,PW減小,由于式(11)中的系數k3小于0,因此輸出基準電壓減小。相反,當開關閉合時,修調電阻與電路斷開,輸出基準電壓增大。

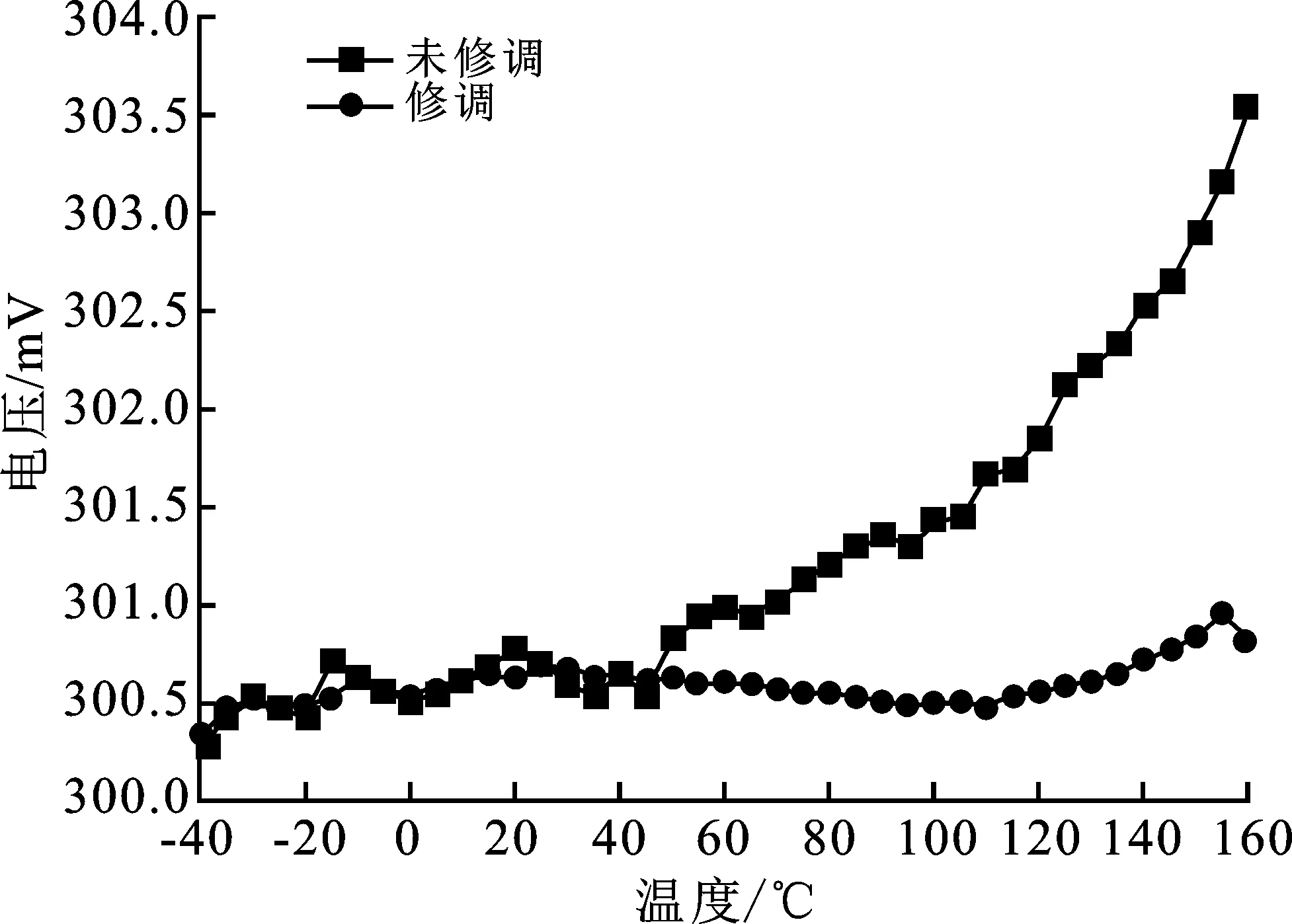

圖5 修調前后輸出參考電壓的溫度特性線

圖5展示了一個樣本芯片修調前后的溫度特性曲線。在低溫度范圍時,分段補償電路不工作,修調前后輸出電壓的溫度曲線接近。在高溫度范圍時,分段補償電路開始工作,電阻修調網絡使輸出電壓的溫度特性曲線得到了明顯改進,輸出電壓修調前后的變化最大為3 mV。

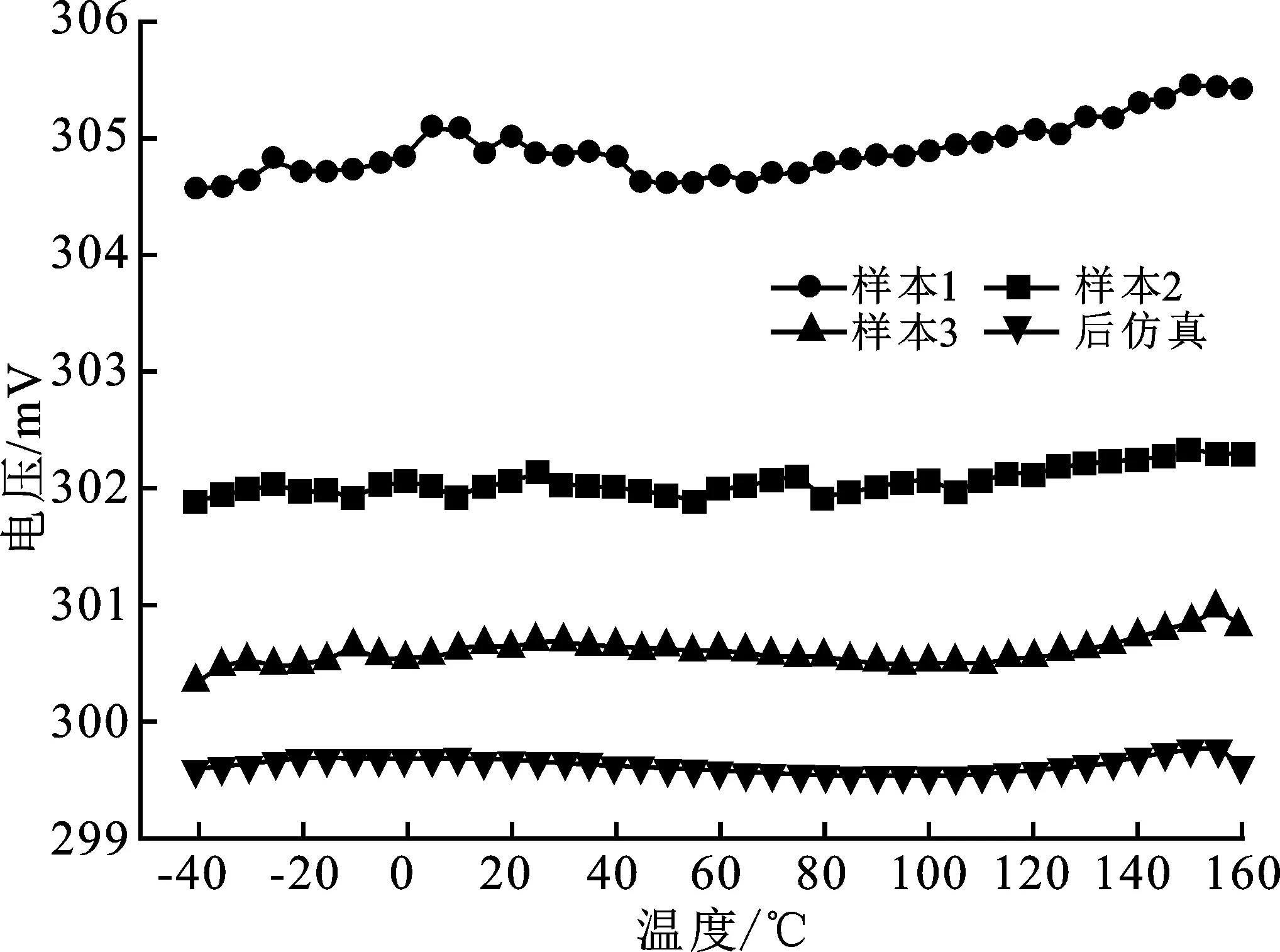

圖6給出了3個樣品芯片在-40 ℃~160 ℃溫度范圍內輸出電壓隨溫度變化的曲線。3個樣品在 -40 ℃~160 ℃寬溫度范圍內的溫度系數分別為14.5×10-6/℃、7.2×10-6/℃、10.3×10-6/℃,平均溫度系數為10.6×10-6/℃。從帶隙基準源的樣品測試曲線和后仿真曲線的對比可以看出,筆者提出的高階補償電路和分段補償電路得到了驗證。但是芯片實測的溫度系數比后仿真結果高2.6×10-6/℃,造成這一差異的原因有電流鏡失配、電阻失配和溝道長度調制效果等。

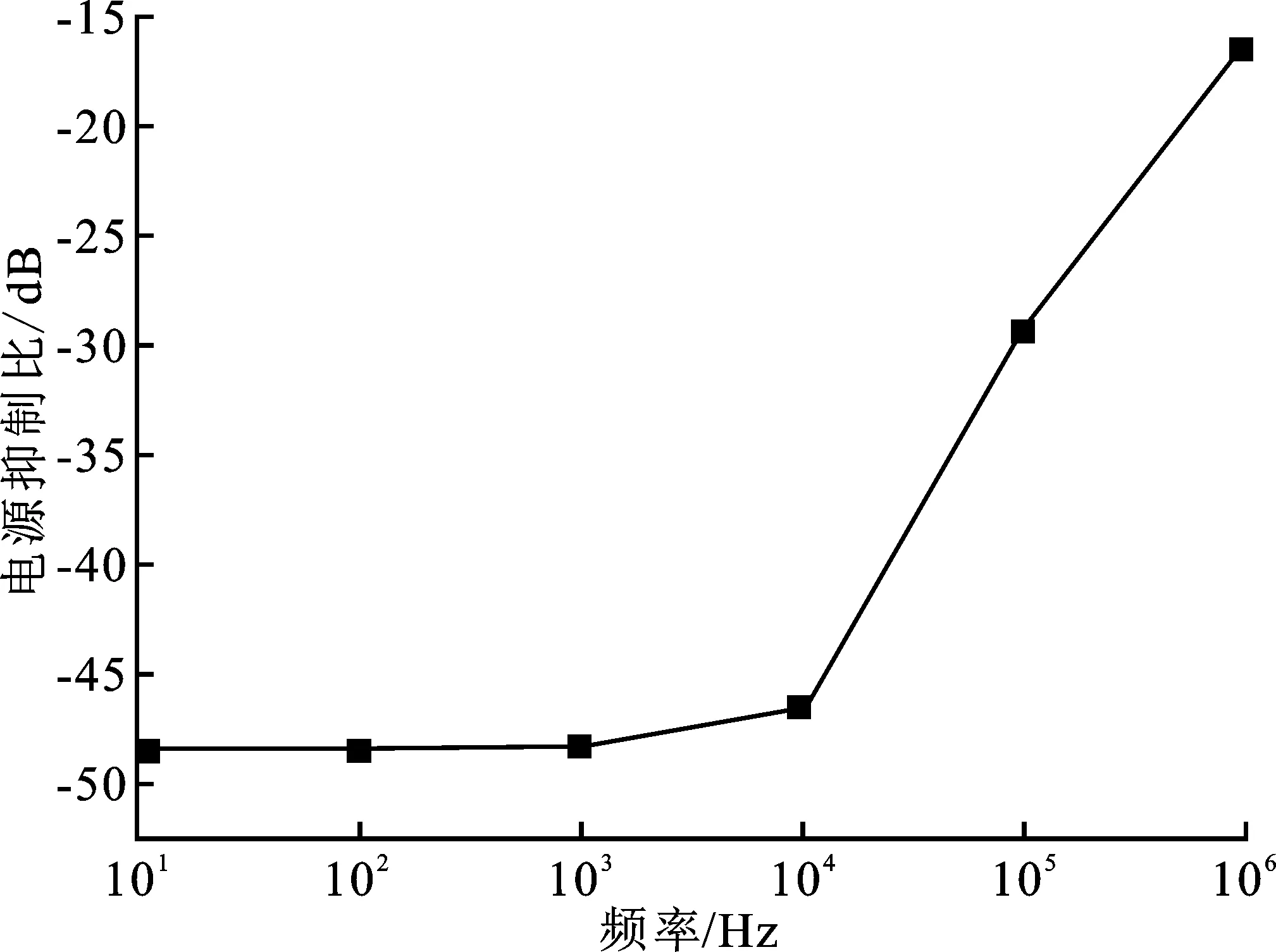

圖7給出了帶隙基準源的電源抑制比測試曲線。低頻時電源抑制比為-48.52 dB,隨著頻率增加到 1 MHz 時,電源抑制比減小至-15 dB。測試結果表明,電源電壓的噪聲對提出的帶隙基準源具有一定影響。

圖6 帶隙基準源溫度系數測試曲線

圖7 帶隙基準源電源抑制比測試曲線

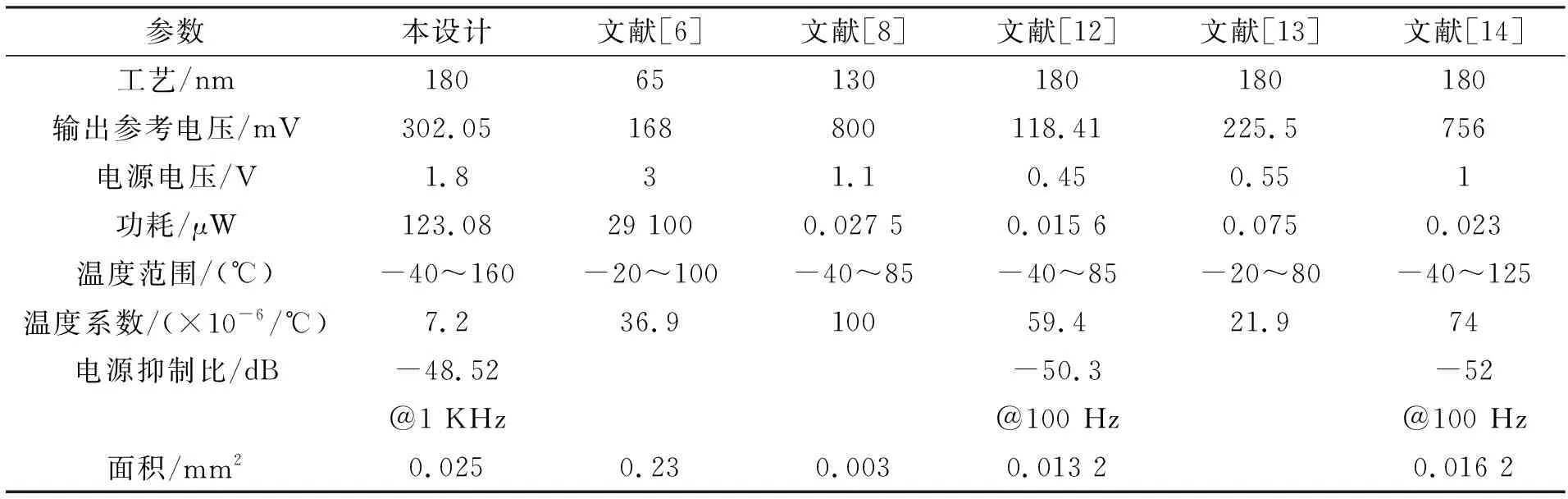

表1總結了本設計與現已發表文獻的帶隙基準源的性能對比。在保證電源抑制比、功耗、芯片面積等性能指標的前提下,筆者提出的帶隙基準源電路的溫度系數低至7.2×10-6/℃,明顯優于其他電路。值得一提的是,筆者所提出的帶隙基準源具有更寬的工作溫度范圍,其應用場景更加廣泛。

表1 本設計與參考文獻性能指標對比

4 總 結

筆者提出了一款高精度的帶隙基準源,電路利用高階溫度補償技術和分段溫度補償技術實現了低溫度系數,同時擴展了工作溫度范圍。電路通過CMOS 180 nm工藝進行驗證。測試結果表明,在-40 ℃~ 160 ℃ 寬溫度范圍內輸出基準電壓的溫度系數最低為7.2×10-6/℃,適用于各種物聯網領域,包括高溫環境下的物聯網應用場景。此外,電路采用簡單的電阻修調網絡以減小工藝角變化對帶隙基準源性能的影響。在1.8 V電源電壓下,電路總電流為68.38 μA,芯片核心面積為0.025 mm2,低頻時電源抑制比為-48.52 dB。