一種基于FPGA的方位增量碼產(chǎn)生方法

范越 周暉

關(guān)鍵詞:方位角碼;增量碼;FPGA;RS422

0引言

雷達(dá)工作時(shí),顯控系統(tǒng)需要從伺服系統(tǒng)接收天線(xiàn)的方位角碼。天線(xiàn)使用雙通道旋轉(zhuǎn)變壓器作為軸角傳感器,經(jīng)粗精通道解碼組合后生成16位的天線(xiàn)方位角,提取出高12位作為給顯控系統(tǒng)的方位角碼。如果用并行接口來(lái)傳輸,且采用差分方式抑制共模干擾,則需要24根線(xiàn),線(xiàn)纜數(shù)量較多,不利于安裝調(diào)試且可靠性差。如果采用其他接口協(xié)議,在某些硬件條件不允許的情況下無(wú)法實(shí)現(xiàn),而且艦船航向角變化有時(shí)會(huì)引起方位角跳變,不能直接使用。因此,需要在只有普通差分接口的條件下,將并行方位角碼轉(zhuǎn)換成串行的脈沖信號(hào)。

本文提出一種在FPGA中將并行12位(或更高)的方位角碼信號(hào)經(jīng)過(guò)補(bǔ)脈沖轉(zhuǎn)換成串行的4096(或更多)個(gè)脈沖的增量碼信號(hào),然后使用RS422接口發(fā)送,簡(jiǎn)化線(xiàn)路,傳輸方便可靠。

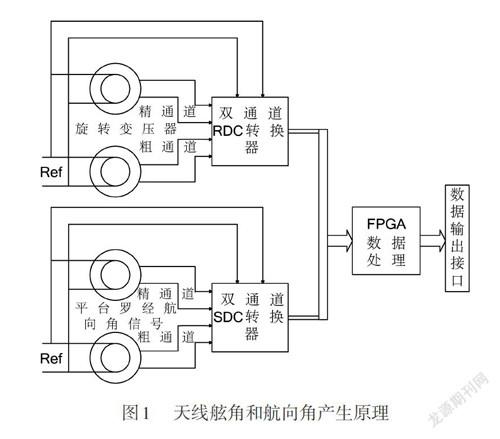

1天線(xiàn)舷角和航向角產(chǎn)生原理

伺服系統(tǒng)使用通用型高速、高精度軸角轉(zhuǎn)換技術(shù),針對(duì)高精度雙通道旋轉(zhuǎn)變壓器和平臺(tái)羅經(jīng)航向角信號(hào),運(yùn)用小型化雙通道軸角轉(zhuǎn)換模塊,利用大規(guī)模可編程邏輯器件的高速處理能力,運(yùn)用硬件描述語(yǔ)言,通過(guò)軟件現(xiàn)場(chǎng)調(diào)節(jié)的方法適應(yīng)傳感器的任意速比的組合糾錯(cuò)處理。其轉(zhuǎn)換速率快、實(shí)時(shí)性好、精度高,能夠適應(yīng)各種雷達(dá)或電子對(duì)抗設(shè)備需要;電路的集成度高,便于嵌入式崗十;可靠性高,適應(yīng)各種嚴(yán)苛的環(huán)境要求。天線(xiàn)舷角和航向角產(chǎn)生原理如圖1所示。

旋轉(zhuǎn)變壓器的粗精通道比為1:32,RDC轉(zhuǎn)換器輸出數(shù)據(jù)的分辨率為14位。由于粗精通道比為1:32,粗通道的第8、第7位數(shù)據(jù)R8R7正好對(duì)應(yīng)精通道的最高兩位數(shù)據(jù)F13F12,當(dāng)R8R7為“11”時(shí),F(xiàn)13F12為“00”時(shí),將粗通道的高5位數(shù)據(jù)加1;當(dāng)R8R7為“00”時(shí),F(xiàn)13F12為“11”時(shí),將粗通道的高5位數(shù)據(jù)減1;然后將粗通道的高5位數(shù)據(jù)和精通道的高11位組合得到16位天線(xiàn)舷角碼。

航向角信號(hào)的粗精通道比為1:36,SDC轉(zhuǎn)換器輸出數(shù)據(jù)的分辨率為14位。由于粗精通道比36不是2的n次方,所以只能通過(guò)將粗通道數(shù)據(jù)左移5位(乘以32)加上粗通道數(shù)據(jù)先左移2位(乘以4)得到與精通道量綱一致的數(shù)據(jù)。設(shè)這個(gè)數(shù)據(jù)為da-ta_temp[18-0]。判斷data temp的第13、第12位數(shù)據(jù)data_tempi312和精通道的最高兩位數(shù)據(jù)F13F12,當(dāng)data_tempi312為“11”時(shí),F(xiàn)13F12為“00”時(shí),將data_temp的高5位數(shù)據(jù)加1;當(dāng)data_templ312為“00”時(shí),F(xiàn)13F12為“11”時(shí),將data_temp的高5位數(shù)據(jù)減1;然后將dat_temp的高5位數(shù)據(jù)和精通道的高11位組合得到16位天線(xiàn)舷角碼。

通過(guò)FPGA控制雙通道RDC轉(zhuǎn)換器,將旋轉(zhuǎn)變壓器的粗精通道信號(hào)轉(zhuǎn)換后讀取,經(jīng)過(guò)粗精通道組合糾錯(cuò)處理后得到16位的天線(xiàn)舷角碼。同時(shí)FPGA控制雙通道SDC轉(zhuǎn)換器,將平臺(tái)羅經(jīng)的航向角粗精通道信號(hào)轉(zhuǎn)換后讀取,經(jīng)過(guò)粗精通道組合糾錯(cuò)處理后得到16位的航向角碼。

2方位角碼跳變?cè)?/p>

天線(xiàn)的方位角等于天線(xiàn)的舷角加上船的航向角,當(dāng)船在調(diào)舷時(shí),如果航向角的變化方向與天線(xiàn)旋轉(zhuǎn)方向一致時(shí),方位角就可能出現(xiàn)跳變的現(xiàn)象,因此無(wú)法通過(guò)方位角直接產(chǎn)生增量脈沖,需要在跳變的時(shí)候補(bǔ)脈沖確保天線(xiàn)轉(zhuǎn)一圈4096個(gè)脈沖不丟失。跳變現(xiàn)象如圖2所示。

天線(xiàn)的方位角合成是在時(shí)鐘CLK的上升沿進(jìn)行的,當(dāng)?shù)?個(gè)CLK的上升沿到來(lái)時(shí),天線(xiàn)舷角為0,航向角為2,方位角即2(0+2);當(dāng)?shù)?個(gè)CLK的上升沿到來(lái)時(shí),天線(xiàn)舷角為0,航向角變?yōu)?,方位角即3(0+3),未發(fā)生跳變;當(dāng)?shù)?個(gè)CLK的上升沿到來(lái)時(shí),天線(xiàn)舷角變?yōu)?,航向角為3,方位角即4(1+3),未發(fā)生跳變;當(dāng)?shù)?個(gè)CLK的上升沿到來(lái)時(shí),方位角保持4不變;當(dāng)?shù)?個(gè)CLK的上升沿到來(lái)時(shí),天線(xiàn)舷角和航向角同時(shí)發(fā)生變化,天線(xiàn)舷角從1變成2,航向角從3變成4,方位角直接從4跳到6。此時(shí)如果將方位角碼直接給顯控系統(tǒng)使用則會(huì)產(chǎn)生問(wèn)題。因此需要判斷是否跳變并補(bǔ)碼產(chǎn)生增量碼。

3增量碼生成原理

增量碼脈沖生成的原理如圖3所示。

原始的方位角碼有16位,根據(jù)顯控系統(tǒng)的需求,取原始方位角碼的高12位使用來(lái)產(chǎn)生增量碼。本系統(tǒng)中使用的是10 MHz的時(shí)鐘,12位的方位角碼FW經(jīng)過(guò)1個(gè)時(shí)鐘周期的延時(shí)得到FWT,將這2個(gè)方位角碼作差比較得出天線(xiàn)方位角度的變化量,如果差值為0,不產(chǎn)生脈沖;如果為1,產(chǎn)生1個(gè)脈沖;如果為2,則說(shuō)明方位角發(fā)生了跳變,產(chǎn)生2個(gè)脈沖;如果為3,則產(chǎn)生3個(gè)脈沖。考慮到船的調(diào)舷速度,不用考慮跳變3個(gè)脈沖以上的情況。

4 FPGA實(shí)現(xiàn)

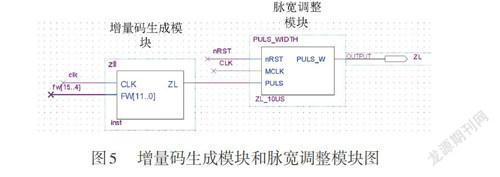

伺服系統(tǒng)以大規(guī)模可編程邏輯芯片F(xiàn)PGA作為系統(tǒng)的信號(hào)處理、I/O和總線(xiàn)管理核心。使用ALTERA公司的Cyclone系列芯片EPlC6Q24017,本芯片包含5980個(gè)邏輯單元,片內(nèi)存儲(chǔ)器92 160 bit,2個(gè)鎖相環(huán)。使用VHDL語(yǔ)言進(jìn)行編程。增量碼生成模塊內(nèi)部如圖4所示。

延時(shí)模塊是將方位角碼延時(shí)1個(gè)時(shí)鐘周期輸出,其中CLK為10 MHz時(shí)鐘,fw為12位的原始方位角碼,輸出fwt。

比較模塊是將當(dāng)前方位角碼fw和前1個(gè)時(shí)鐘周期的方位角碼fwt作差比較,如果發(fā)生變化,變化標(biāo)志位fwbi置1,將變化差值fw-fwt賦給n輸出。否則變化標(biāo)志位fwbi置0,n輸出保持不變。

在FPGA中經(jīng)過(guò)延時(shí)模塊、比較、脈沖生成、增量碼合成后產(chǎn)生增量碼,集成為如圖5所示的“增量碼生成”模塊,將得到的增量碼經(jīng)過(guò)脈寬調(diào)整模塊調(diào)整為所需要的脈沖寬度(10μs),最后發(fā)送出去。

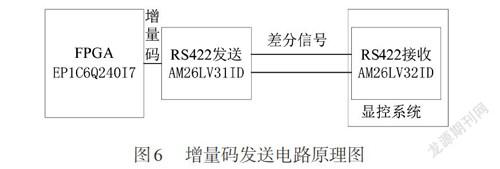

5硬件電路原理

使用RS422接口發(fā)送增量碼信號(hào)的電路原理圖如圖6所示。

FPGA產(chǎn)生增量碼后,經(jīng)過(guò)10口輸出,通過(guò)RS422發(fā)送芯片AM26LV31轉(zhuǎn)換為差分信號(hào)發(fā)送給顯控系統(tǒng),經(jīng)過(guò)差分接收芯片AM26LV32接收使用。

6結(jié)束語(yǔ)

本文介紹了使用高速、高精度軸角轉(zhuǎn)換技術(shù)針對(duì)高精度雙通道旋轉(zhuǎn)變壓器和平臺(tái)羅經(jīng)航向角信號(hào)的組合糾錯(cuò)處理方法,得到16位方位角碼后,分析了其產(chǎn)生跳變的原理,并最終提出了一種在FPGA中將并行12位的方位角碼信號(hào)經(jīng)過(guò)補(bǔ)脈沖轉(zhuǎn)換成串行的4096個(gè)脈沖的增量碼信號(hào)的方法,大大精簡(jiǎn)了傳輸線(xiàn)纜數(shù)量,提高可靠性。該方法已在實(shí)際系統(tǒng)中應(yīng)用,完全符合系統(tǒng)工作要求,運(yùn)行良好,證明了方法的有效性。