24~30 GHz GaN HEMT單片集成單刀雙擲開關

曾丁元 朱浩慎,2 馮文杰 車文荃,2 薛泉,2

0 引言

由于5G移動通信技術的快速發展,Sub-6 GHz頻段擁擠的頻譜資源已難以滿足5G無線通信的超高數據速率需求.毫米波頻段具有豐富的頻譜,是5G技術發展的必然選擇.3GPP已經明確n257(28 GHz)和n258(26 GHz)頻段為5G毫米波的優先部署頻段.因此,近年來在上述頻段開展了較多的研究工作[1-2],也得到非常多的關注.

在時分雙工通信系統中,單刀雙擲開關(Single-Pole Double-Throw,SPDT)控制發射和接收信號鏈路,通常置于天線與功率放大器和低噪聲放大器之間作為連接模塊,是收發系統中的關鍵模塊之一.對于接收鏈路而言,開關的插入損耗直接影響整個系統的噪聲性能,而對于發射鏈路則主要影響輸出的功率以及功率附加效率[3].毫米波頻段前端模組中的開關,需要低的插入損耗來減小開關對整體系統性能的惡化.在傳統射頻前端中,開關與功率放大器和低噪聲放大器通過封裝實現互連往往引入額外的損耗與失配,尤其在毫米波頻段,對性能惡化尤為顯著.因此,對于毫米波前端電路,各模塊采用同種工藝實現并單片集成有利于降低損耗,提升集成度.

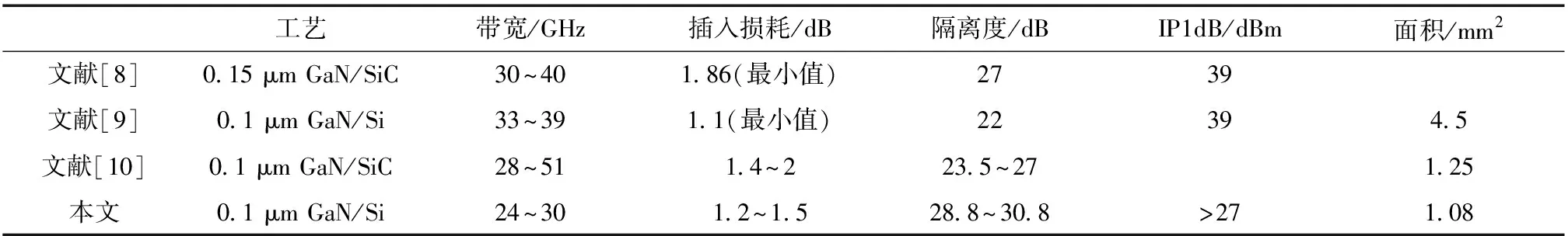

過去,工作在毫米波頻段的單刀雙擲開關多使用CMOS、GaAs等工藝實現[4-5].CMOS開關以其成熟的工藝技術,可以做到易集成、低成本但是其器件的擊穿電壓低,功率容量受限.GaAs開關擁有較低的插入損耗以及隔離性能,但相較于近年來發展起來的GaN開關技術,其襯底的熱導率以及擊穿電壓較低,導致功率密度不及GaN開關.由于寬禁帶半導體GaN在大功率射頻功放的功率密度以及效率等方面具有顯著優勢,成為近年來的研究熱點.隨著5G毫米波技術的發展,研究大功率高效率毫米波集成前端具有廣闊的應用前景.近期研究表明,GaN開關也可實現良好的插入損耗和隔離度性能.因此,利用GaN單片微波集成電路技術(MMIC)實現射頻開關并與GaN功率放大器和低噪聲放大器實現單片集成,可在大功率毫米波前端方面獲得更優的性能[6].2015年中國電子科技集團公司第十三研究所的郭豐強等[7]設計出了工作在Ku波段的GaN大功率單刀雙擲開關,其插入損耗小于0.9 dB,隔離度大于27 dB,可承受10 W的連續波輸入功率;2015年北京理工大學的郭德淳教授團隊在第16屆通信技術國際會議上發表了Ka波段的寬帶GaN開關,采用1/4波長轉換并聯結構,且并聯晶體管采用兩個對稱并聯形式以增大隔離度,設計的開關在30~40 GHz頻帶內插入損耗小于2 dB,隔離度優于25 dB,回波損耗優于18 dB,輸入功率1 dB壓縮點可達39 dBm[8];2019年羅馬第二大學的Polli等[9]采用100 nm GaN工藝設計出了一款應用于空載衛星的Ka波段單刀雙擲開關,不同于傳統并聯開關結構,該開關使用串聯晶體管感性諧振結構,33~39 GHz頻帶內實現了插入損耗為1.1 dB,隔離度為22 dB,以及39 dBm的輸入功率1 dB壓縮性能;2019年德國弗萊堡應用固體物理研究所的Thome等[10]采用100 nm GaN工藝設計了一款28~51 GHz的單刀雙擲開關,采用1/4波長轉換并聯結構,插入損耗為1.4~2 dB,隔離度為23.5~27 dB.

本文基于硅基 GaN工藝設計了一款工作在24~30 GHz的單刀雙擲開關,可同時覆蓋5G毫米波的n257和n258頻段.該開關通過采用1/4波長轉換并聯結構來兼顧插入損耗和隔離度性能,輸入輸出端口均串聯MIM電容隔離直流成分并參與匹配.測試結果顯示所設計的開關插入損耗在24~30 GHz內,插入損耗低于1.5 dB,隔離度優于28 dB,輸入功率1 dB壓縮點大于27 dBm(-5 V柵極偏置下),電路面積為1.08 mm2.

1 SPDT 開關電路設計

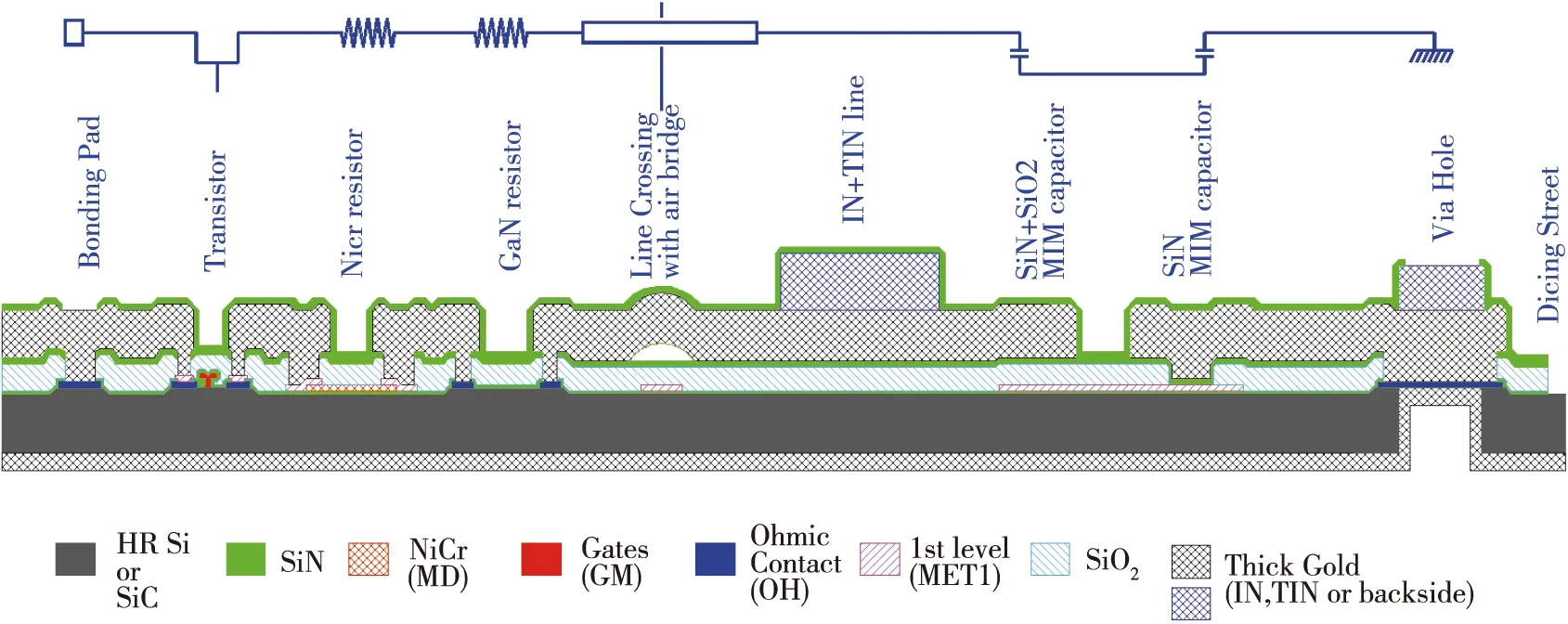

本文研究的GaN開關采用OMMIC的100 nm 的硅基GaN工藝(D01GH)適合微波和毫米波應用,其工藝截面如圖1所示,包含空氣橋,使用兩層互聯金屬IN和MET1,可以實現繞線電感和微帶傳輸線.有高低密度兩種類型的電容以及兩種類型的電阻,高阻值電阻使用GaN有源層實現,鉻鎳金屬電阻阻值較低但精度高,通孔穿過100 μm的高電阻率硅基板減少對地寄生電感.采用AlGaN/GaN異質結高電子遷移率晶體管(HEMT)作為開關器件,具有100 nm柵長的蘑菇型柵極,使用再生長的歐姆接觸減小源極接觸電阻,特征頻率(ft)和最大振蕩頻率(fmax)分別為110 GHz和160 GHz.30 GHz測試的功率密度為3.3 W/mm,擊穿電壓為40 V[11].HEMT作為開關器件時的導通電阻(Ron)和關斷電容(Coff)分別為1.4 Ω·mm和0.45 pF/mm.

圖1 OMMIC D01GH工藝截面Fig.1 The cross section of OMMIC D01GH process

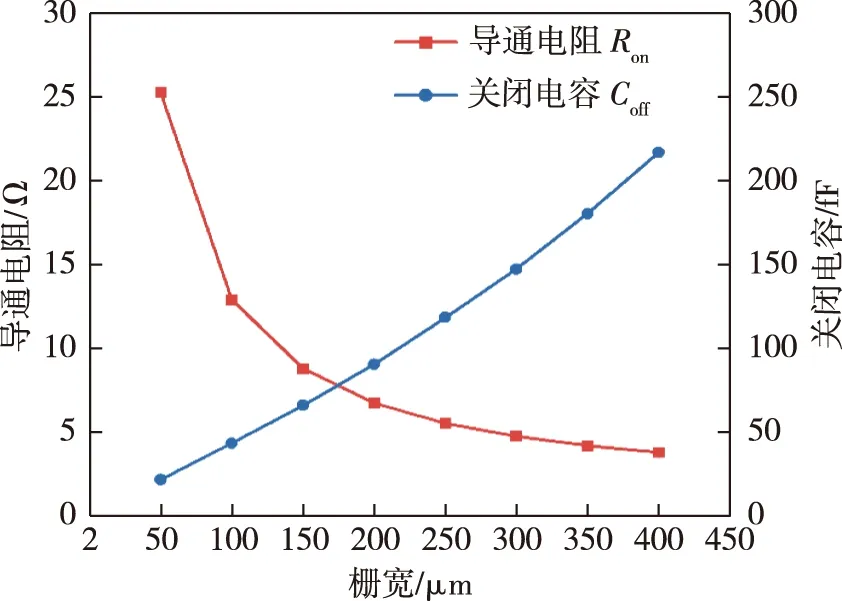

對于開關電路設計,通常由HEMT器件的柵極電壓控制信號導通或者關閉.毫米波頻段的寄生效應嚴重,而開關器件的導通電阻和關斷電容直接決定了開關的插入損耗和隔離度性能,需仔細考慮開關的尺寸以獲得滿足要求的性能.一般而言,當HEMT器件柵極電壓Vg大于其截止電壓時,HEMT器件導通,可簡單等效為導通電阻Ron.而HEMT柵極電壓低于截止電壓時,HEMT器件截止,可簡單等效為關閉電容Coff.Ron與Coff的值越小則會獲得越好的開關性能.如圖2所示:隨著HEMT器件柵寬增大,Ron減小,Coff增大;HEMT器件柵寬減小,則Ron增大,Coff減小.當柵寬為200 μm的時候,開關器件的Ron約為6.8 Ω,Coff約為91 fF,此時可獲得較好的插入損耗和隔離度性能.若使用單級HEMT器件并聯開關電路,則整體開關電路的隔離度為20 dB左右,不滿足設計需求.而為保證較低的插入損耗,HEMT器件柵寬不能增大以減小Ron來優化隔離度性能.故需使用兩級并聯的開關電路,第二級選擇較小柵寬的HEMT器件,如100 μm柵寬,以獲得較小的Coff值,避免開關電路插入損耗性能惡化,同時兩級并聯結構又能獲得較好的開關隔離度.

圖2 不同柵寬開關器件的導通電阻和關斷電容Fig.2 Ron and Coff of the HEMT with different gate widths

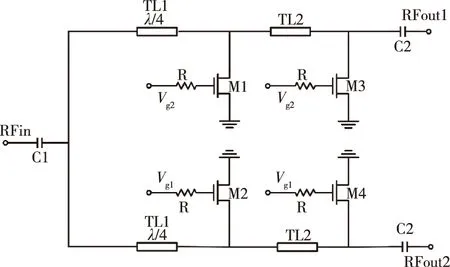

本文設計的SPDT開關為1/4波長轉換并聯結構,兩條支路為對稱結構,每條支路使用兩級HEMT器件并聯的拓撲以獲得較大的隔離度.圖3為設計的開關電路的拓撲結構.TL1和TL2為微帶傳輸線,理論上長度為1/4波長時可以獲得良好的隔離度,但一般只適用于頻帶較窄的設計.因此,在本文的設計中,需要適當調節其長度.此外,當M1和M3關閉時,該條支路導通,TL2與M1和M2關閉狀態下的等效電容Coff1和Coff2組成π型電路,并與TL1完成阻抗變換.C1和C2均為MIM電容參與電路的輸入和輸出匹配,并可隔離直流成分.

圖3 SPDT開關拓撲結構Fig.3 Topology of the proposed SPDT switch

利用電磁仿真工具ADS進行優化仿真,第一級HEMT器件M1和M2需選取較大尺寸以降低導通電阻增大隔離度,而第二級HEMT器件M3、M4尺寸較小,減小關斷電容降低插入損耗.最終優化后選取M1和M2的柵寬為200 μm,M3和M4的柵寬為100 μm.C1為180 fF,C2為700 fF.該工藝50 Ω特性阻抗線寬為83 μm左右,不利于電路版圖布局.故電路中微帶線寬度均為40 μm,其特性阻抗約為67 Ω,與電路中其他元件互連并參與匹配.柵極電阻R用以隔離泄漏至柵極的射頻信號,此處柵極電阻R的值為4 kΩ.電路整體控制電壓使用兩個PAD,控制電壓為0 V和-5 V.

2 仿真與測試結果

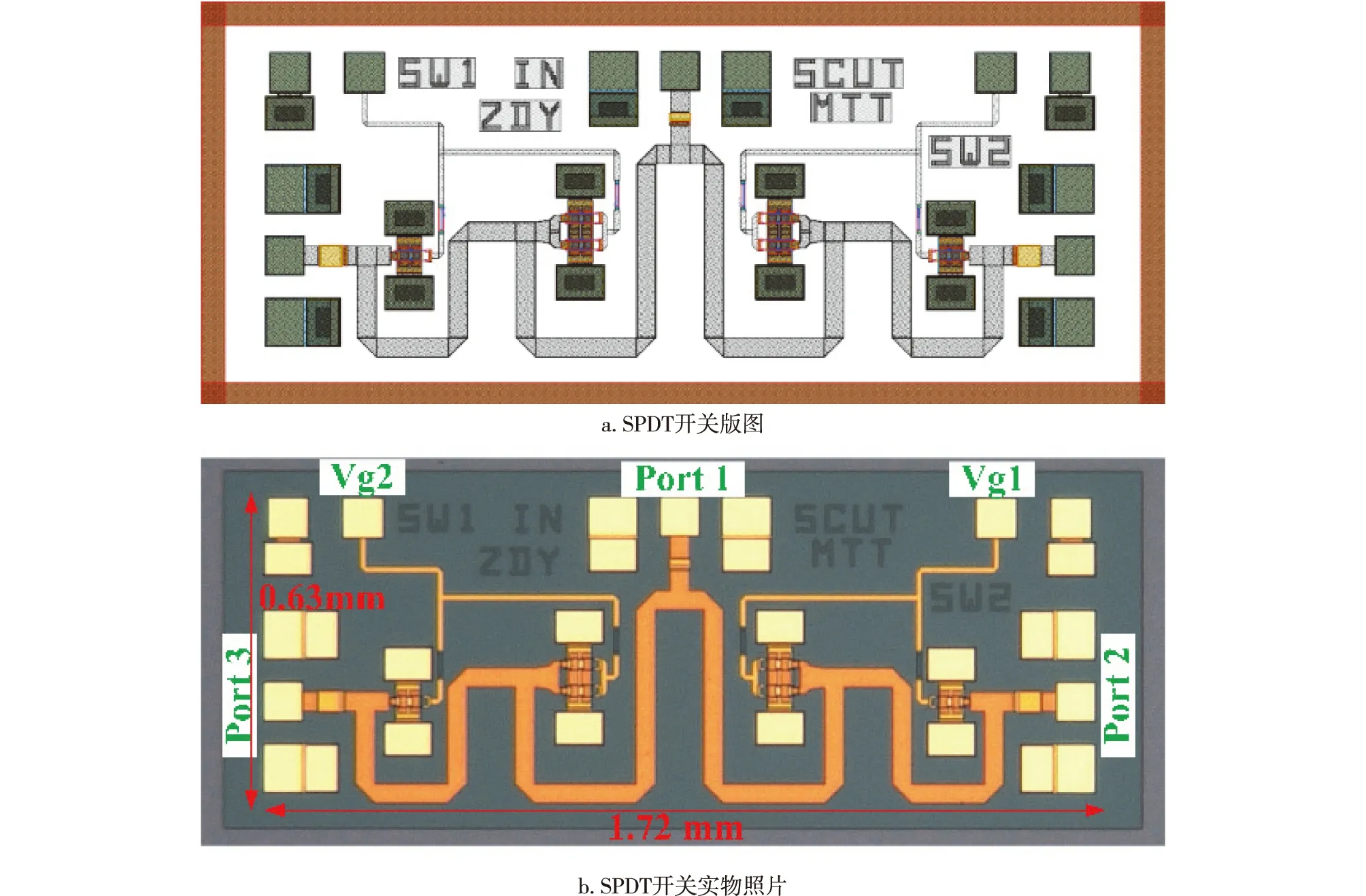

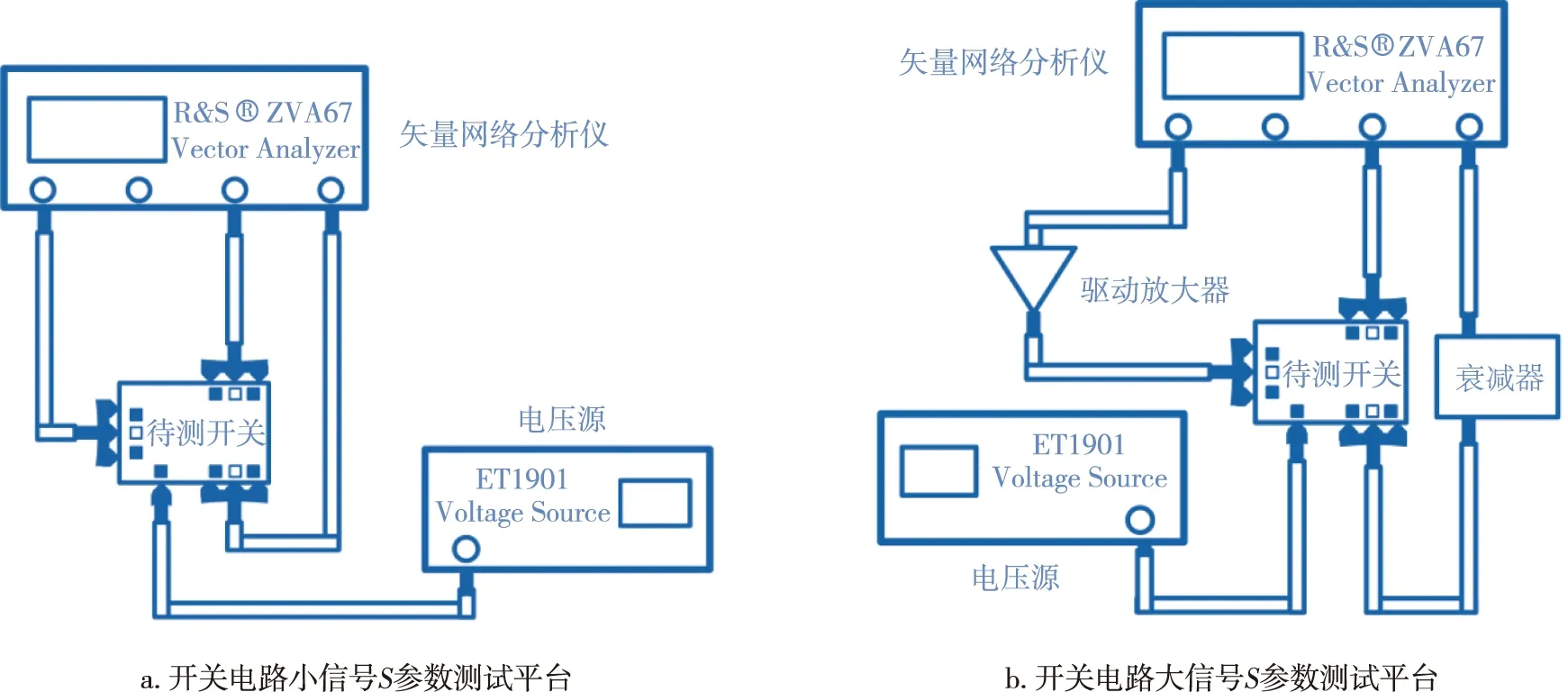

基于100 nm GaN工藝實現24~30 GHz的SPDT開關,電路版圖如圖4a所示,電路加工實物照片如圖4b所示,電路尺寸為630 μm×1 720 μm.開關的測試方案如圖5所示,使用R&S?ZVA67矢量網絡分析儀進行測試.采用在片的短路、開路、負載、饋通校準方案(SOLT)對電路3個端口進行校準.如圖5b所示,由于網絡分析儀輸出的信號功率有限,故大信號S參數測試時在待測開關的輸入端口加入了驅動放大器來增大網絡分析儀輸入開關的信號功率,并在開關導通支路的輸出端加入衰減器,衰減進入網絡分析儀的信號功率.

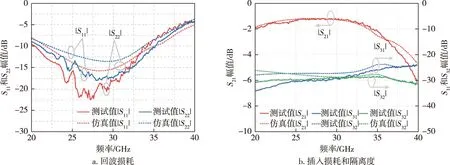

SPDT開關電路經在片測試,得到圖6所示的仿真與測試結果.測試時,如圖4b所示,一條支路的控制電壓Vg2為0 V,該條支路斷開;另一支路控制電壓Vg1為-5 V,該支路導通.圖6a為開關的輸入輸出回波損耗曲線,S11和S22為導通支路輸入端口1和輸出端口2的回波損耗,24~30 GHz頻帶內測試的輸入回波損耗大于15 dB,輸出回波損耗大于12 dB,均優于仿真結果.圖6b為開關的插入損耗(S21)和隔離度(S31、S23)曲線,24~30 GHz頻帶內,測試的插入損耗低于1.5 dB(最低為1.18 dB),基本符合仿真結果;測試的關斷支路的端口3至公共端口1之間的隔離度為28.8~30.8 dB,導通支路的端口2至關斷支路的端口3之間的隔離度為29~30 dB,均優于仿真結果2~3 dB,說明實際HEMT晶體管的寄生參數與仿真模型稍有差別.

圖4 SPDT開關電路版圖和實物顯微照片Fig.4 Layout (a) and micrograph (b) of the SPDT switch

圖5 開關電路測試平臺搭建Fig.5 Measurement setup of the SPDT switch a.small signal;b.large signal

圖6 SPDT開關仿真與測試結果Fig.6 Simulation and measurement results of the SPDT switch a.return loss;b.insertion loss and isolation

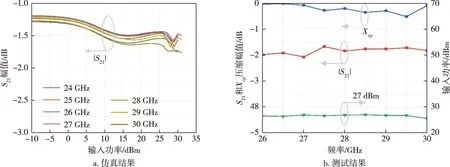

圖7是SPDT開關的大信號仿真結果.由圖7a可以看出開關在24~30 GHz頻帶內的輸入1 dB功率壓縮點大于30 dBm.經過對電路的簡單測試,得到大信號S參數的測試結果如圖7b所示,Xcp表示插入損耗壓縮曲線,S21為大信號輸入下的插入損耗性能曲線,Pin為測試時的輸入功率.當輸入功率為27 dBm時,插入損耗還未壓縮至1 dB,可知此開關的輸入功率1 dB壓縮點大于27 dBm.測試時的開關電路輸入端接入了驅動放大器,導通支路輸出端接了衰減器,與后仿真的電路環境有所區別,引入了一定的損耗,故測試的輸入1 dB壓縮點與后仿真結果有一定差距.表1對比了已發表的一些毫米波頻段的GaN單刀雙擲開關的工作,可以看到本文基于GaN的開關電路在28 GHz毫米波頻段擁有優異的插入損耗以及隔離度性能,有利于集成高性能GaN毫米波前端.

圖7 SPDT開關大信號S參數(S21)仿真與測試結果Fig.7 Simulation (a) and measurement (b) results of the large signal S-parameter (S21) for the SPDT switch

表1 與已有文獻的性能比較

3 結束語

本文基于1/4波長轉換并聯的兩級開關拓撲結構,采用硅基100 nm GaN工藝設計并實現了一種毫米波SPDT開關.電路測試結果表明該SPDT開關在24~30 GHz的范圍內實現了1.2~1.5 dB的插入損耗,隔離度為28.8~30.8 dB,輸入功率1 dB壓縮點大于27 dBm,在插入損耗、隔離度和功率容量上都表現出了優良的性能,適用于單片集成的GaN毫米波前端組件,在5G毫米波相控陣系統上具有較好的應用前景.