基于DDS的功率合成與雷達相噪改善機理的研究

章順 蔡曉波 徐學偉

(中國電子科技集團公司第十四研究所 江蘇省南京市 210000)

1 引言

預警機是空基預警探測體系的信息樞紐和指揮中心,它集預警探測、情報融合、情報分發和指揮控制等多功能于一體,負責對空中、海上以及地面目標進行大范圍搜索、跟蹤與識別,并指揮己方的導彈、飛機、火炮、艦船以及其他火控系統[1]。在近代歷次戰爭,特別是海灣戰爭、科索沃戰爭以及利比亞戰爭中,預警機均發揮了極其重要的作用,已成為現代化戰爭中不可缺少的重要武器裝備。此外,預警機還可以將探測傳感器、通信網絡、作戰平臺、指揮系統和作戰人員高效實時地融合于作戰體系中,起到了戰場效能倍增器的作用,極大地增強了體系作戰的能力[2]。

為適應現代化高科技戰爭的特點,對雷達要觀測的目標種類、測量參數等都提出了許多新要求。雷達應能觀測隱身目標、小型目標和低空目標,在強雜波、強干擾和硬打擊條件下工作,具有目標分類、識別能力等更使雷達發展面臨巨大挑戰[3]。

采用相控陣天線技術的雷達成為相控陣雷達,和傳統雷達天線相比,相控陣天線具有波束指向、波束形狀快速變化能力,易于形成多個波束,可以在空間實現信號功率的合成[4]。這些特點使相控陣雷達可以完成多種雷達功能,具有穩定跟蹤多批高速運動目標的能力。即使在單部發射機功率受到限制的條件下,我們也能獲得所求的特大功率,為增加雷達探測作用距離、提高雷達測量精度和觀測包括隱身目標在內的各種低可觀測目標提供了技術潛力[5]。

雷達是空中預警機的核心,雷達對探測作用距離和精度有很高的要求,發射機是雷達系統的重要組成部分,現代雷達為了獲得好的相參處理增益以及對雜波的抑制能力,大都要求發射機輸出的信號頻率具有好的相干性和穩定性[6]。而頻率穩定度是發射機設計的關鍵之一,因此研究頻率穩定度十分重要。相位噪聲是發射機的一項非常重要的性能指標,它對電子設備和電子系統的性能影響很大。從頻域看,它分布在載波信號的兩旁,按冪律譜分布。發射波形的相噪則是決定雷達探測作用距離和精度的重要因素[7]。

2 相位噪聲的定義

相位噪聲(Phase noise)是指系統(如各種視頻器件)在各種噪聲的作用下引起的系統輸出信號相位的隨機變化。它是衡量頻率標準源(高穩晶振、原子頻標等)頻穩質量的重要指標[8]。

相位噪聲的起因有以下幾種:放大器噪聲和非線性克爾效應,也即自相位調制(SPM)和交叉相位調制(XPM)和四波混頻,但一般在分析的時候,只考慮到自相位調制引起的相移效應。

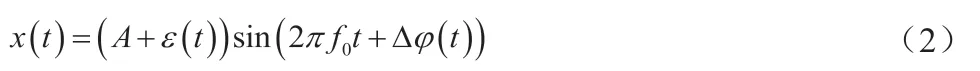

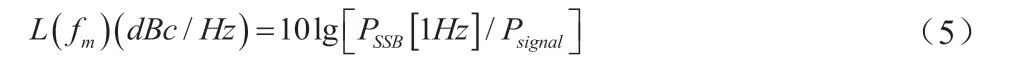

一般理想的載波信號可以表示為[9]:

其中:A 為信號的幅度,f0為信號的頻率,2πf0t 為信號的相位。在現實工程中,信號的相位和幅度是變化的,可以表示為[10]:

對于某個信號的穩定度,我們在頻域中一般用信號的相位噪聲表示,實際上它表示在頻域內,信號在信號頻譜中的寄生輸出,對于這個寄生輸出,我們把頻域內相位噪聲定義為偏離載頻多少赫的傅里葉頻率上[13](以fm表示)每單位頻帶的單邊帶功率與信號功率的比值來衡量,單位是dBc/Hz。由于離散的寄生輸出對于fm來說,分布是不均勻的,所以相位噪聲是fm的函數[14],表示為:

一般取對數表示為:

3 相位噪聲的影響

電子技術的發展,使器件的噪聲系數越來越低,放大器的動態范圍也越來越大,增益也大有提高,使得電路系統的靈敏度和選擇性及線性度等主要技術指標都得到較好的解決。隨著技術不斷提高,對電路系統要求必須低相位噪聲,在現代技術中,相位噪聲已成為限制電路系統的主要因素。低相噪對提高電路系統性能起到重要作用[15]。

當目標超低空飛行時,雷達面臨著很強的地面雜波,要想從強地雜波中提取信號目標,雷達必須要有很高的改善因子。因為這些雜波進入接收機,經混頻后,很難把有用信號與強地物反射波分離開,尤其對低速度運動目標,并接近地面時,發現目標就變得非常困難,這時只有提高雷達改善因子[16]。

為了提高低空檢測能力,提高對低空突防目標的發現能力,信號的低相噪非常重要,雷達能從強雜波環境中區分出運動目標,則要求雷達必須全相參產生出極低相噪的發射信號和接收機本振信號及各種相參基準信號[17]。

4 功率合成的理論分析

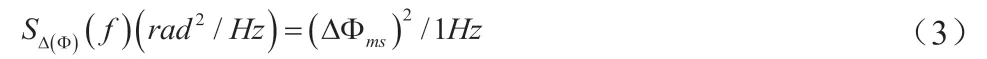

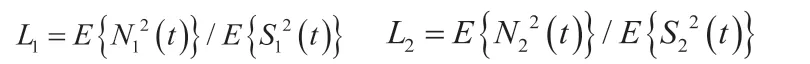

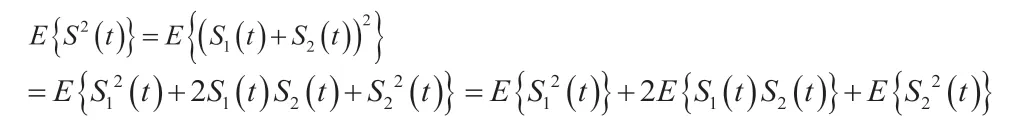

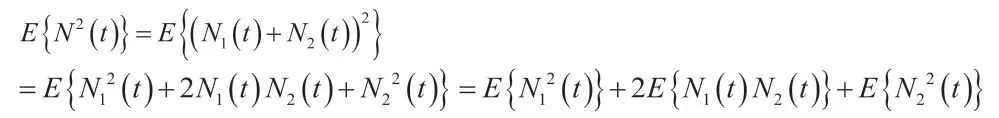

S1(t)和S2(t)兩路信號初始相位一致,因此

合成噪聲功率為:

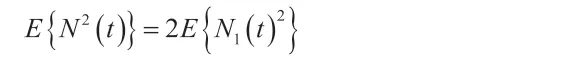

N1(t)和N2(t)兩路噪聲非相關,因此所以

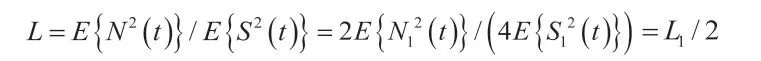

合成信號的相噪為:

完成功率合成的相位噪聲取對數為:

通過以上的理論分析可得結論,完成2 路信號功率合成得到的信號,相位噪聲性能優化3dB。接下來我們通過實驗驗證此結論。

5 芯片原理和系統框架

頻率合成技術起源于上個世紀三十年代,當時采用的頻率合成方法是直接頻率合成。它是利用混頻、倍頻、分頻的方法由參考源頻率經過加、減、乘、除運算,直接組合出所需要的頻率。他的優點是捷變速度快,相位噪聲低。但由于結構復雜,價格昂貴,很快被淘汰。在此之后出線了間接頻率合成。這種方法主要是將相位反饋理論和鎖相環技術運用于頻率合成領域,即所謂的PLL 頻率合成技術。PLL 頻率合成技術克服了直接式頻率合成的許多缺點,特別是它易于集成化,使得體積小、相位噪聲低、雜散抑制輸出頻率高,但它的頻率切換時間相對較長。隨著數字信號理論和超大規模集成電路的發展,在頻率合成領域誕生了技術性的革命,那就是直接數字合成技術DDS(Direct Digital Synthesis)。這是一種頻率合成的新方法,頻率轉換時間短、頻率分辨率高、輸出相位連續、控制靈活方便,但其頻率上限較低且雜散較大,極大地限制了DDS的推廣和應用。隨著電子技術的發展,各類電子系統對信號源的要求越來越高,如何抑制DDS 輸出信號中雜散也就成了研究熱點。

DDS 系統的核心是相位累加器,它由N 位加法器與N 位相位寄存器構成,類似一個簡單的計數器。每來一個時鐘脈沖,相位寄存器的輸出就增加一個步長的相位增量值,加法器將頻率控制數據與累加寄存器輸出的累加相位數據相加,把相加結果送至累加寄存器的數據輸入端。相位累加器鍵入線性相位累加,累加至滿量時產生一次計數溢出,這個溢出頻率即為DDS的輸出頻率。正弦查詢表是一個可編程只讀存儲器(PROM),存儲的是以相位為地址的一個周期正弦波的數字幅度信息。將相位寄存器的輸出與相位控制字相加得到的數據作為一個地址對正弦查詢表進行尋址,查詢表把輸入的地址相位信息映射成正弦波幅度信號,驅動DAC,輸出模擬信號,低通濾波器平滑并濾除不需要的取樣分量,以便輸出頻譜純凈的正弦波信號。

國內某公司有一款內部包含四路DDS,每路有獨立控制的相位、頻率、幅度控制字,最高工作頻率可達2.5GHz 的芯片。它支持線性掃描、非線性掃描、頻率鍵控、相位鍵控、幅度控制、RAM 掃描等功能。芯片內部集成 4 個高精度 DSS,確保良好的動態性能。多芯片同步下,內部集成硬同步功能及 TDC 軟同步功能。

單路DDS 相噪性能的提升上限是芯片本身的性能,由于重新優化DDS 芯片設計、工藝,以及DDS 芯片外圍時鐘電源電路的難度是非常大的,因此,單路信號的相噪性能提升十分有限,為了產生更好相噪的波形,如果我們用多路不相參的信號做功率合成,再通過現場可編程門陣列FPGA(Field Programmable Gate Array)調節每一路信號的初始相位,使之全部一致,再做功率合成,從理論上說,2 路合成相噪性能可以優化3dB[18]。

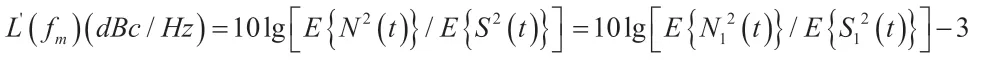

為了完成這個方法的驗證,我們設計了一個使用4 片DDS 芯片做功率合成的電路系統,電路框圖如圖1。通過FPGA 控制同步時鐘管理芯片的輸出同步時鐘,以及配置4 片DDS 芯片寄存器,使芯片輸出4 路點頻信號,為了保證每路信號不相參,我們用每個DDS 芯片的第一通道做兩兩功率合成[19]。

圖1:DDS 信號功率合成原理框圖

電路在設計時,為了保證功信號功率合成時相位一致,要保證每一條時鐘、每一路信號和FPGA 離散控制信號鏈路的板內走線全部等長。通過FPGA 控制時鐘管理芯片,使4 片DDS 芯片同步輸出相同頻率的連續波信號,并且讓4 路輸出信號的初始相位同步,讓這4 路DDS 信號做功率合成,以達到信號合成功率最大、相噪性能最好的目的[20]。

此外,為了保證每一路DDS 輸出信號不相關,每一片DDS 工作需要的模擬2.5V、1.2V 和數字2.5V、1.2V 分別用4 片LDO (Low Dropout Regulator,低壓差線性穩壓器)線性電源單獨供電。此外,為了最終測試相噪不受開關電源的開關頻率影響,我把每一片DDS芯片單獨置于一塊子板上,母板是開關電源、FPGA 以及對外控制信號,子板上獨立產生DDS的4 個線性電源品種,子板和母板間用射頻和高速連接器盲插對接,最后,在一塊單獨的、和數字電路部分隔離的模擬電路板上做信號的功率合成,以達到射頻信號不受數字電路電源開關頻率干擾的目的。

DDS的采樣時鐘供2.4GHz,系統時鐘為100MHz,4 片DDS的第一通道都產生50.1MHz 的點頻信號,下一節是測試結果。

6 實驗結果與分析

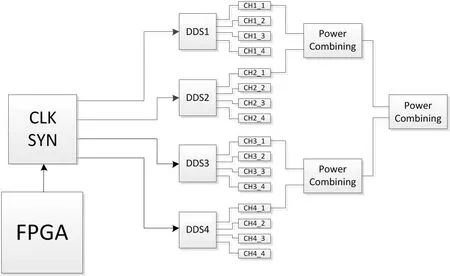

通過FPGA 調節時鐘相位,讓4 片DDS 芯片產生的4 路信號初始相位一致,最終得到的波形用示波器測量如圖2所示,所有信號的初始相位一致以便進行功率合成。

圖2:4 路同相位DDS 信號的時域波形

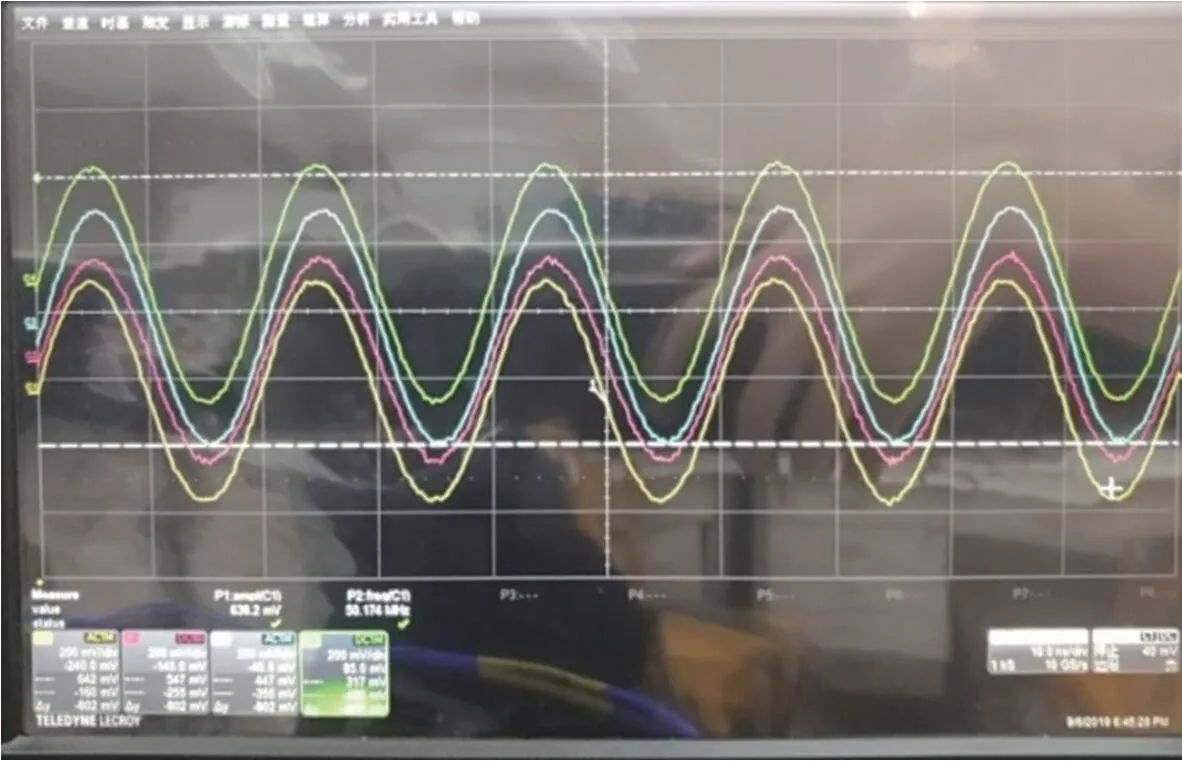

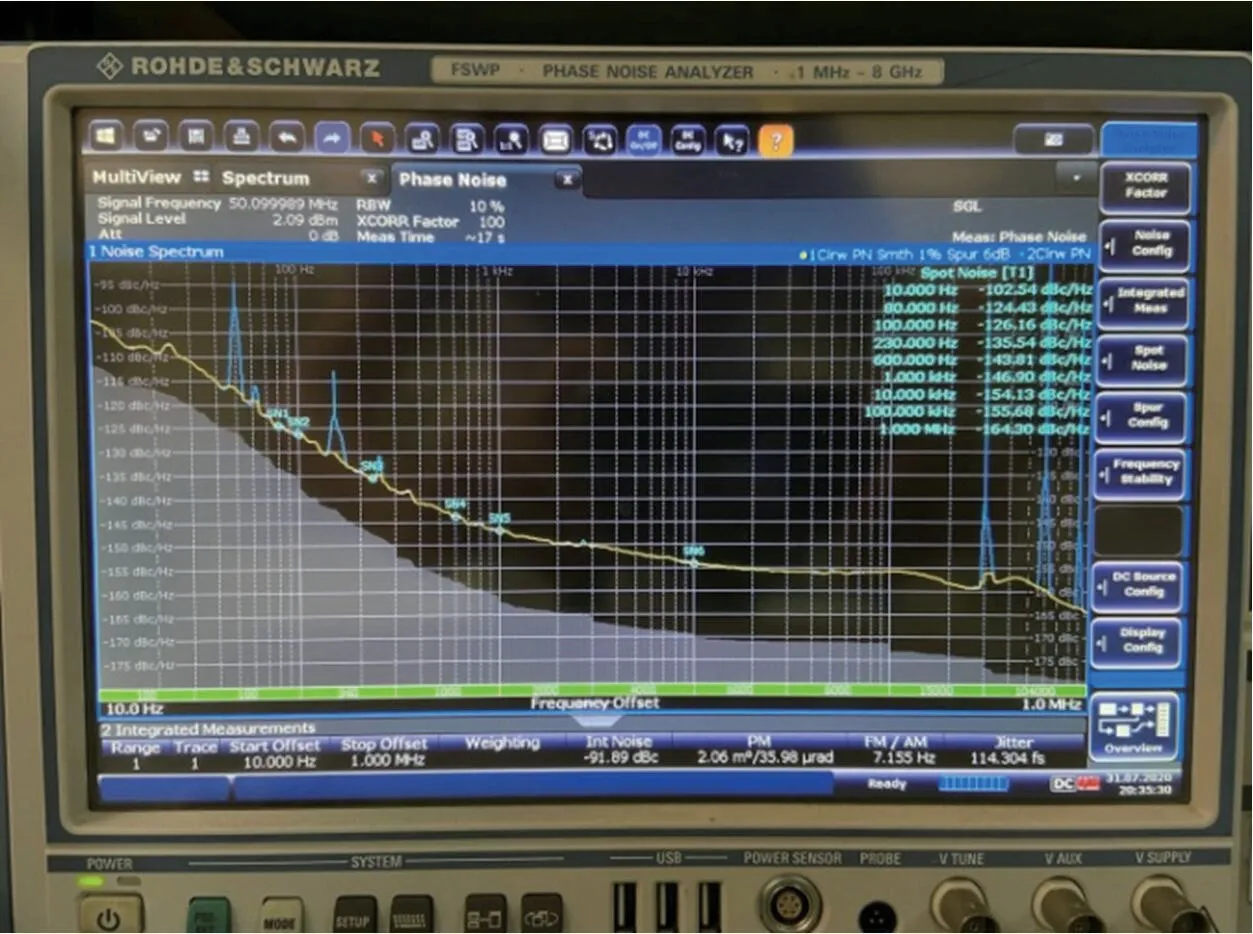

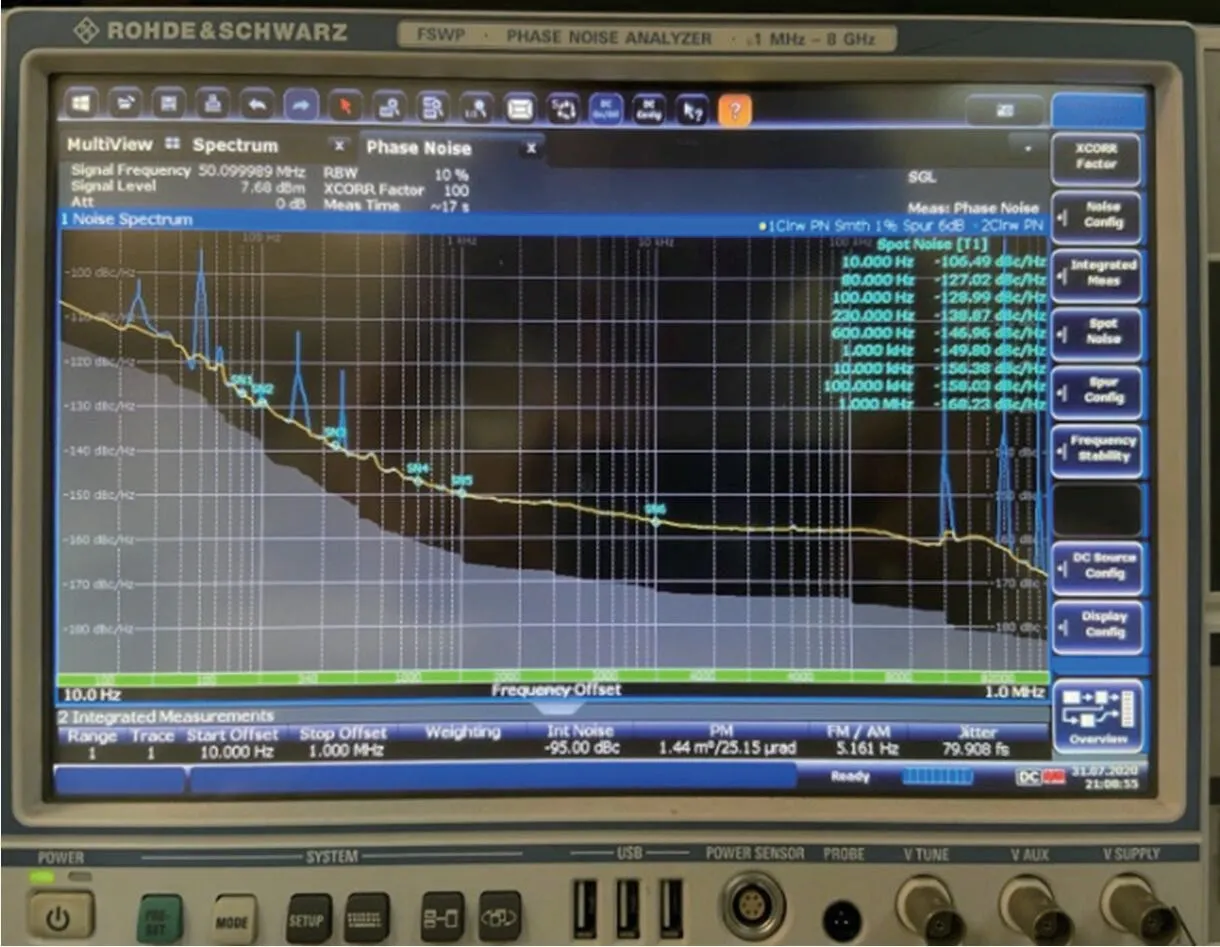

通過相位噪聲測試儀測量,我們可得,2.4GHz 信號源,單路DDS 芯片,2 路DDS 芯片合成以及4 路DDS 芯片合成得到信號的相噪分別如圖3,圖4,圖5 和圖6所示。

圖3:2.4GHz 信號源的相噪性能圖

圖4:單路DDS 信號的相噪性能圖

圖5:2 路DDS 信號合成的相噪性能圖

圖6:4 路DDS 信號合成的相噪性能圖

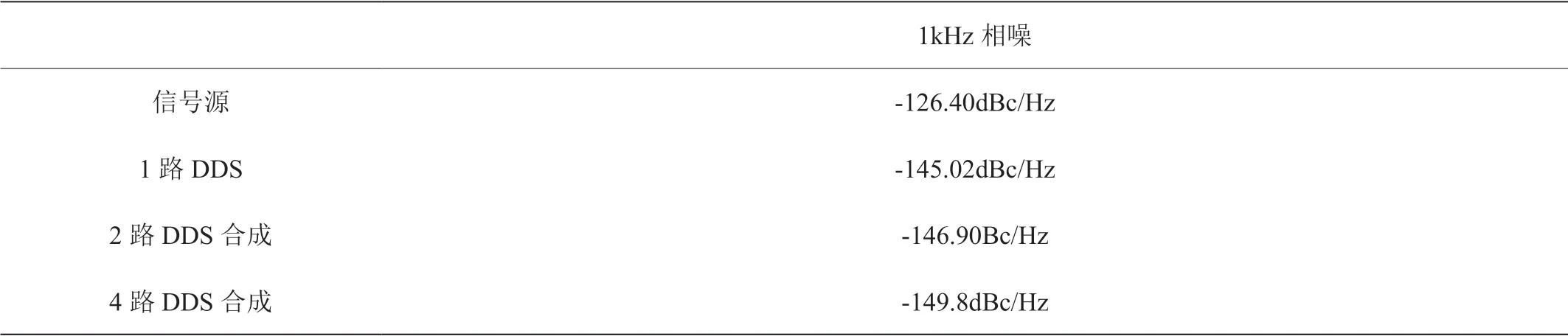

表1是這些DDS 芯片信號在距中心頻率1kHz 處的相噪數據,50.1MHz 點頻信號在1kHz 處,單路DDS 信號的相噪是-145.02dBc/Hz,2 路非相關信號合成的相噪是-146.90dBc/Hz,4 路非相關信號合成的相噪是-149.8dBc/Hz,兩兩合成,相噪指標雖然沒有提升到理論上的3dB,但是考慮到線路誤差和測量誤差,這種信號功率合成的方法對提升系統相噪性能是很有效的。

表1:不同信號相噪表

7 結束語

直接數字頻率合成是一種新型的頻率合成技術,它代表了頻率合成技術數字化發展的新方向。但是,DDS 所固有的雜散和噪聲,并且在頻率升高時雜散和噪聲也隨之增加,相噪性能也會有一定的損失,使它的應用范圍有一定的限制。所以如何減少DDS 輸出中的雜散和噪聲成分提升相噪性能,是當今DDS 研究中的核心問題之一

本文以DDS 芯片為基礎,討論了多路DDS 信號合成與雷達相噪改善性能的關系,通過實驗測量,驗證了多個信號合成,主信號功率合成,非相參噪聲未合成,可以提升系統相噪性能的結論,滿足了現代電路對高質量信號的要求,具有廣闊的發展前景,這種技術可以大范圍運用在預警探測相控陣雷達上。