基于STM32的嵌入式存儲系統的設計與實現

段素平

(中國船舶重工集團有限公司第七一〇研究所,湖北 宜昌 443003)

0 引言

當前,嵌入式技術發展越來越快,對大容量數據存儲的需求也越來越迫切。傳統的嵌入式系統或產品一般只帶有Flash、ROM等存儲器,只能存儲少量數據,若嵌入式系統需要存儲大容量數據,目前常用的存儲設備有 SD存儲卡、U盤、Flash芯片等。Flash芯片存儲容量小、價格高,且需要集成在PCB印制電路板上使用;U盤雖然存儲容量高,但設計相對比較復雜,占用空間比較大,連接可靠性不高[1];而SD存儲卡體積小、存儲容量高,支持SPI/SDMMC驅動,多種尺寸可供選擇滿足不同應用需求,優勢明顯[2-3]。基于此,設計了一種以SD存儲卡作為存儲設備的嵌入式存儲系統。

1 硬件設計

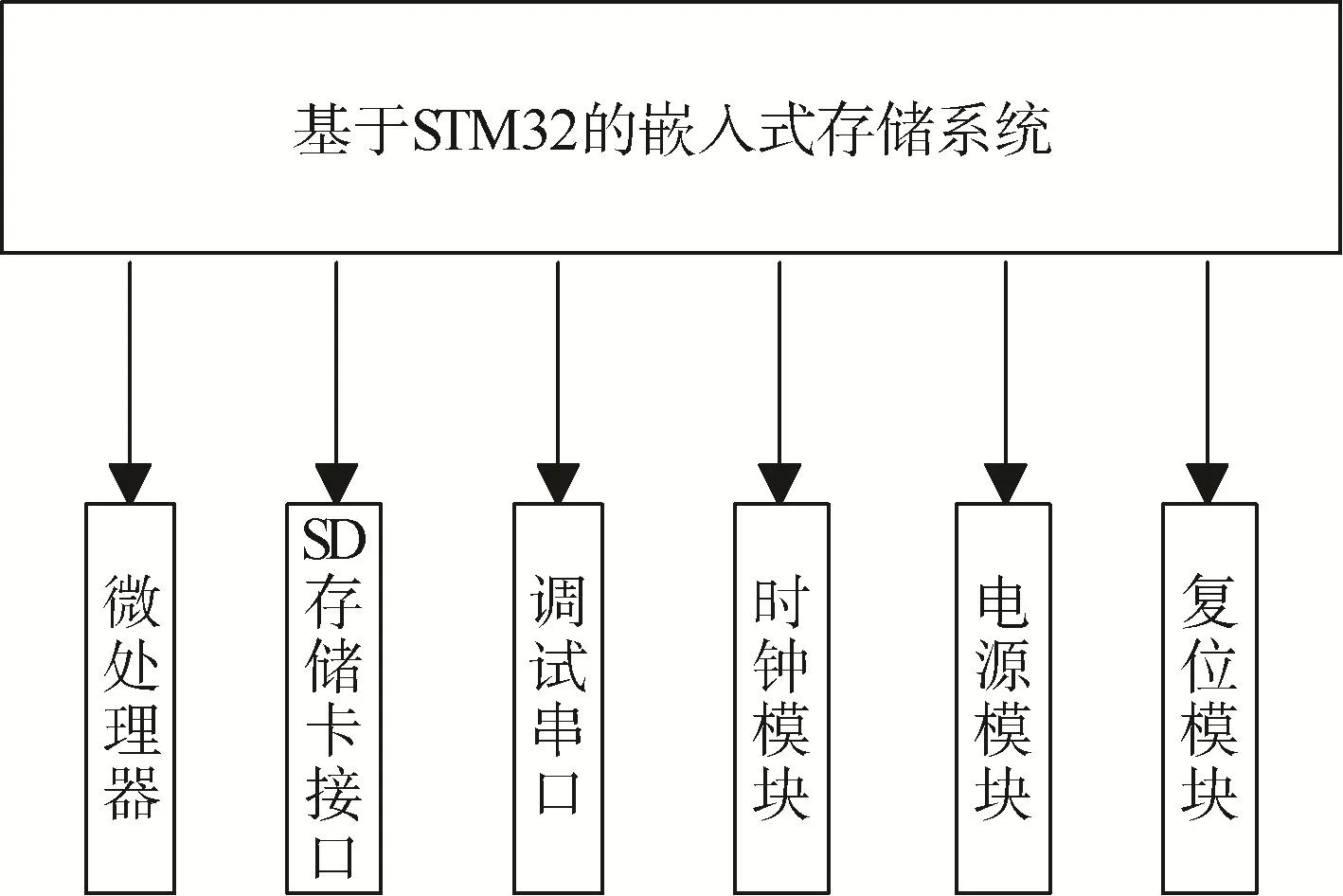

本系統主要由微處理器、SD存儲卡接口電路、復位模塊、電源模塊以及時鐘模塊等組成,如圖1所示。其中復位模塊、電源模塊以及時鐘模塊設計比較簡單,也不是本系統設計重點,所以本文不作介紹。

圖1 系統組成示意圖Fig.1 Diagram of system composition

1.1 硬件電路設計

1)微處理器。

微處理器主要負責控制整個系統的處理操作、狀態監測以及任務管理等功能,最重要的是實現大容量數據快速可靠的存儲和讀取。選擇STM32H743作為本系統的微處理器,該處理器是 ST 推出的基于 ARM Cortex M7 內核的處理器,擁有高達1 060 KB 的片內 SRAM,并且支持 SDRAM內存擴展。STM32H743工作頻率達到400 MHz,具有6級流水線,帶有指令和數據Cache,大大提高了性能。此外,STM32H743自帶豐富的外圍接口,其中就包括SDMMC接口控制器[4],利用該接口控制器可以很高效地實現SD存儲卡接口電路設計。

2)SD存儲卡接口電路。

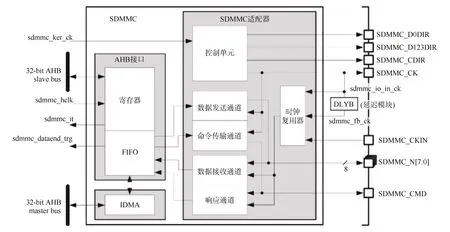

STM32H743自帶SDMMC控制器,最高通信速度可達48 MHz[5],如圖2所示。本系統利用該控制器實現SD存儲卡接口電路設計。

圖2 SDMMC控制器示意圖Fig.2 Diagram of SDMMC controller

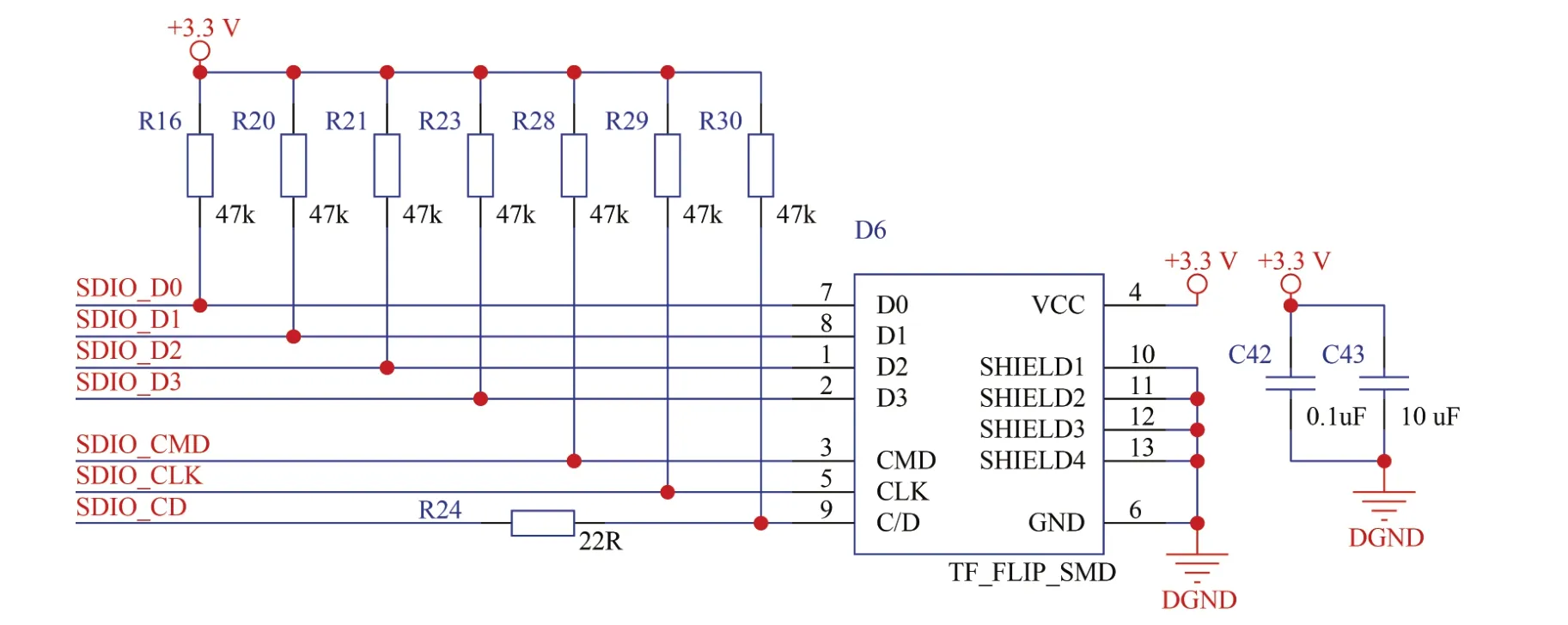

在 SDIO 模式下,只需要用到:SDMMC_CK、SDMMC_D[3︰0]、SDMMC_CMD 這幾根線即可正常驅動 SD 卡,電路設計原理圖如圖3所示。

圖3中,SDIO_D0-SDIO_D3為數據線,實現數據傳輸,所有的數據線都工作在推挽模式。SDIO_CLK為時鐘線,對應 SDMMC控制器的卡時鐘SDMMC_CK(每個時鐘周期在命令和數據線上傳輸1位命令或數據),在3.3 V信號電平下,該時鐘頻率最大可以達到50 MHz。需要注意的一點是,在 SD 卡剛剛初始化的時候, SDMMC_CK時鐘是不能超過 400 kHz 的,否則可能無法完成初始化,在初始化以后,就可以設置時鐘頻率到最大了[6]。SD_CD為SDMMC控制器通用命令信號線,對應SDMMC控制器的SDMMC_CMD,SDMMC的所有命令和響應都是通過 SDMMC_CMD 引腳傳輸的,任何命令的長度都是固定為48 位[7]。

圖3 SD卡接口電路原理圖Fig.3 Schematic of SD card interface circuit

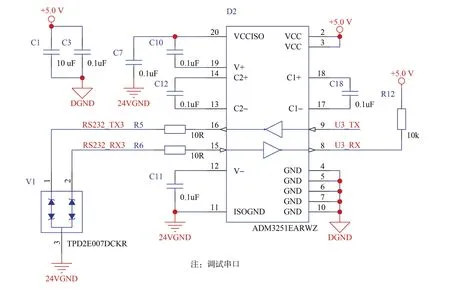

3)調試串口。

串口(串行通信接口)是指數據一位一位地順序傳送,其特點是通信線路簡單,只要一對傳輸線就可以實現雙向通信,從而大大降低了成本。RS232是最常用的一種串行通信接口,也稱標準串口[8],本系統使用RS232用作調試接口,實現系統狀態信息的打印輸出。

由于STM32H743輸出的都是TTL電平,即邏輯“平,對應2~3.3 V,邏輯“邏輯對應0~0.4 V,而 RS232標準采用負邏輯,即邏輯“1”對應-5~-15 V,邏輯“0”對應+5~+15 V[9]。為了實現兩者之間的串口通信,利用ADM3251芯片進行電平的轉換,電路設計如圖4所示。

圖4 調試串口電路原理圖Fig.4 Schematic of debugging serial circuit

1.2 PCB抗干擾設計

為了提高系統的可靠性和抗干擾能力,在設計硬件平臺時完成了以下工作:

1)將數字地和模擬地分開設計,電源線、地線的走向和數據線的走向平行設計,以提高抗干擾能力。

2)電源線設計得盡可能寬,減少環路電阻。

3)分布在電路板正反兩面的信號線進行垂直處理,在需要拐彎的地方設計成135°角。

4)PCB板上的過孔會帶來一定的電容效應,設計的時候盡量減少過孔數量。

2 軟件設計

本系統軟件設計用到的工具主要是 MDK,MDK源自德國的KEIL公司,它使用 uVision5 IDE集成開發環境,是目前針對 ARM 處理器,尤其是 Cortex M 內核處理器的最佳開發工具[10]。

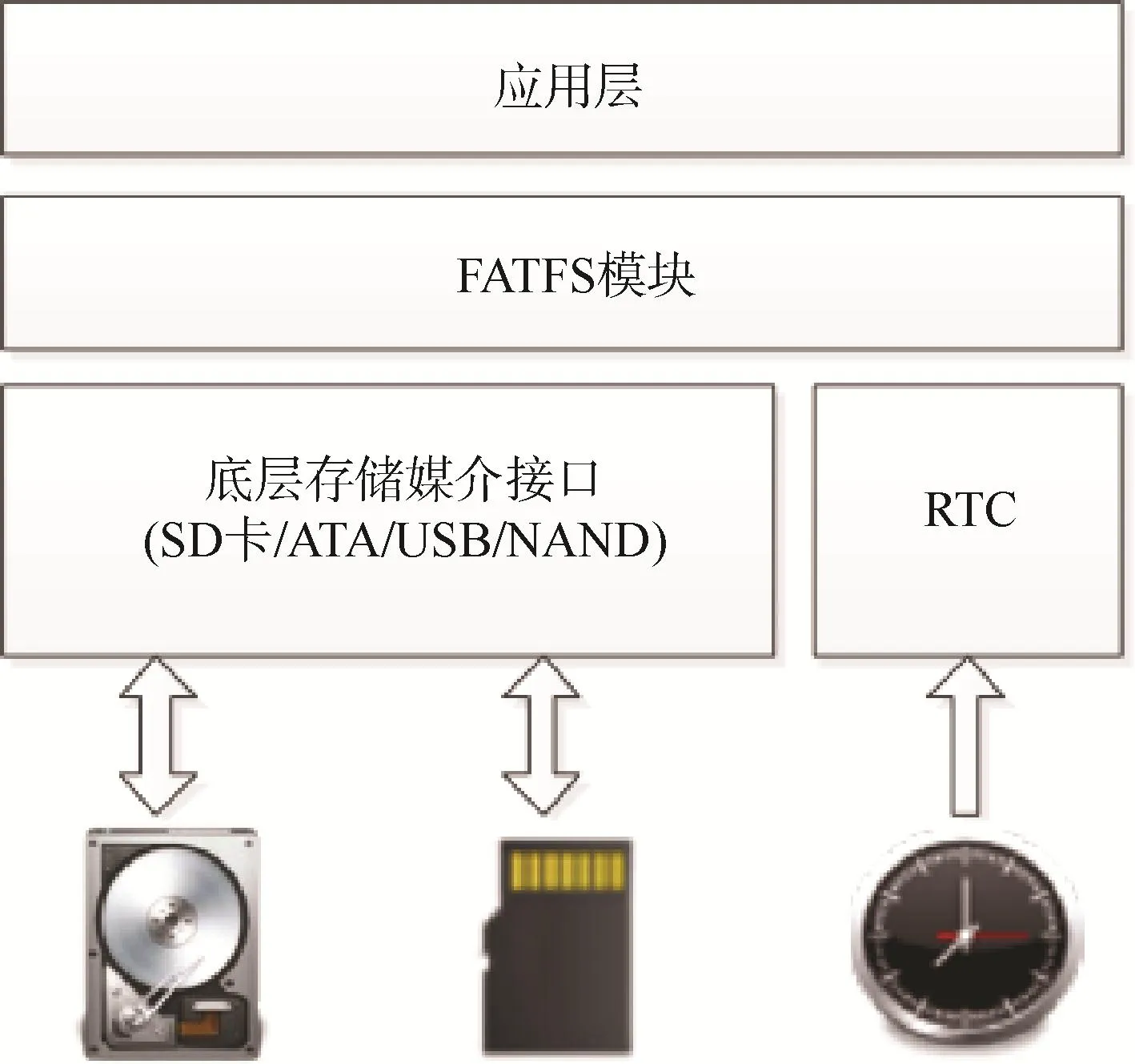

2.1 FatFS文件系統移植

對于存儲設備的管理,若采用傳統讀寫扇區的方式,不但會影響系統的性能,也無法發揮SD存儲卡的優勢,因此本系統移植FatFS文件系統對存儲設備進行數據管理。FatFS文件系統是一個完全免費開源的 FAT文件系統模塊,該系統為應用程序開發提供統一的、標準的API函數,具有良好的可維護性和移植性[11]。FatFS 文件系統的層次結構如圖5所示。

圖5 FatFS文件系統的層次結構圖Fig.5 Hierarchy diagram of FatFS file system

最頂層是應用層,使用者無需理會 FatFS 的內部結構和復雜的 FAT 協議,只需要調用FATFS模塊提供給用戶的應用接口函數,如 f_open,f_read,f_write 和 f_close 等,就可以像在 PC 上讀寫文件那樣簡單[12]。中間層 FATFS 模塊,實現了 FAT 文件讀寫協議,使用時只要將需要的頭文件包含進去即可。需要編寫移植代碼的是FatFS模塊提供的底層接口,它包括存儲媒介讀寫接口(diskI/O)和供給文件創建修改時間的實時時鐘。

FATFS 模塊在移植的時候,一般只需要修改源碼中ffconf.h 和 diskio.c 兩個文件。FATFS模塊的所有配置項都是存放在 ffconf.h 里面,通過配置里面的一些選項,來滿足系統的需求;diskio.c實現底層驅動,需要編寫如圖6所示的6個接口函數[13]。

圖6 FatFS底層驅動接口函數Fig.6 Interface function of FatFS underlying driver

disk_initialize( )函數實現磁盤驅動器的初始化;disk_status( )函數的功能是返回當前磁盤驅動器的狀態;disk_read( )函數讀取磁盤驅動器上的數據;disk_write( )函數是往磁盤驅動器上寫入數據;disk_ioctl( )函數用來控制設備指定特性和除了讀/寫外的雜項功能;get_fattime( )函數用來獲取當前時間。

2.2 應用程序設計

在成功移植FatFS文件系統基礎上,需要完成應用程序的編寫,應用程序完成的工作如下:

1)系統硬件初始化,包括配置系統時鐘、HAL庫初始化、使能Cache以及配置系統中斷等。

2)SD 存儲卡接口初始化,主要利用STM32H743自帶的SDMMC控制器對SD存儲卡接口進行初始化操作。

3)FatFS文件系統初始化,將SD存儲卡在磁盤的編號設置為0,并通過f_mount( )函數為SD存儲卡注冊一個工作區。

4)完成 SD卡存儲功能,先調用 f_open( )函數創建一個新文件或打開已存在的文件,然后調用f_write( )函數將緩沖區的內容寫入到剛打開的文件中,最后調用f_close( )函數關閉已打開的文件。以上步驟即可完成SD卡的數據存儲。

5) 完成SD卡讀取功能,先調用f_open( )函數打開數據存儲文件,然后調用f_read( )函數將文件內容寫入到緩沖區,并作出相應處理,最后調用f_close( )函數關閉已打開的文件。以上步驟即可完成SD卡的數據讀取。

2.3 軟件可靠性設計

SD存儲卡的較高讀寫速率可能會導致讀寫錯誤的發生,為了降低錯誤發生的概率,提高系統的可靠性,本系統軟件設計時采取以下措施:

1)讀寫數據采用校驗方式來檢驗數據的正確性,同時為了避免校驗和正確而數據錯誤的極其偶然情況發生,對數據層面進行再次檢驗,比如給加入數據幀頭,在讀寫數據時均對數據的幀頭加以判斷。只有當數據幀頭以及數據校驗和均正確,才會認為本次數據有效。

2)讀寫錯誤發生后,對數據進行循環讀寫,直到正確讀寫數據才跳出循環。

3 系統驗證

為了驗證系統的功能,設計了2組測試。第1組為基本功能測試。測試在 SD存儲卡中新建目錄或文件、在文件中讀寫數據等功能。在SD卡根目錄下新建根 SD_BasicFuctionsTest”目錄和“sd_test.txte文件,并在“sd_test.txte文件中寫入測試數據。之后讀取SD卡中所有信息,觀察是否含有“SD_BasicFuctionsTest”目錄和“sd_test.txtes文件。若存在該文件,讀取該文件數據,觀察是否和之前寫入的數據一致。

第2組為系統性能測試。測試系統讀寫SD卡速度(大容量數據存儲系統中,數據讀寫速度是一個很重要的設計指標)以及讀寫可靠性。在 SD卡根目錄下新建“Speed.txt”文件,往該文件全速寫入2 048 kB數據,計算其寫入速度;之后全速讀取“Speed.txt”文件中的數據,計算文件讀取速度。同時將讀取的數據與之前寫入的數據進行比較,統計匹配度。

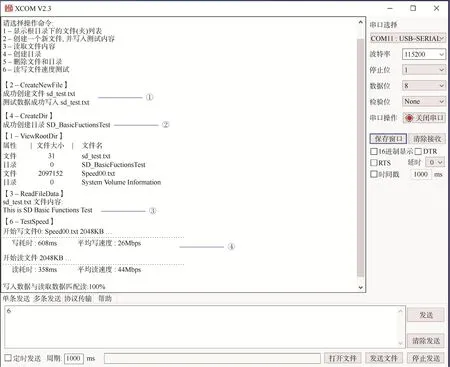

上述的測試步驟,本系統都通過調試串口打印相應信息,如圖7所示。

圖7 調試串口打印的測試信息Fig.7 Test information printed by the serial port

圖7中的①表明系統成功創建了文件“sd_test.txt”,并成功寫入測試數據;②說明系統成功創建了“SD_BasicFuctionsTest”目錄。之后讀取“sd_test.txt”文件數據,該數據與之前寫入的數據一致,如圖中③所示。圖7中的④是系統性能測試時打印信息情況,可知SD存儲卡讀寫速度分別達到了44 Mbps和26 Mbps,可滿足大部分應用需求。讀寫數據匹配度達到了100%,說明系統可靠性符合要求。

4 結束語

本文主要對嵌入式存儲系統進行了討論和研究,成功完成了系統的硬件設計和軟件設計。最后,通過2組試驗對系統的基本功能、讀寫速度以及可靠性進行了測試,測試結果充分驗證了本系統設計的正確性。