一種低電壓VCO-ADC的設計與校準方法

佟星元,楊 梅,郭 慧

(西安郵電大學 電子工程學院,陜西 西安 710121)

模數轉換器(Analog-to-Digital Converter, ADC)是連接模擬域和數字域的“橋梁”[1],是片上系統(System-on-Chip, SoC)中必不可少的組成部分。常見的ADC在模擬域完成數字量化[2]。隨著集成電路工藝特征尺寸的不斷縮小和晶體管特征頻率的不斷升高,數字電路的時鐘頻率得以提升。時鐘頻率的提高有利于增加時間域的分辨率。目前,越來越多的新興應用領域需要ADC在低電源電壓條件下工作。在低電源電壓條件下,一方面,受限于比較器的精度,高性能ADC的設計變得更加困難[3];另一方面,模擬輸入信號從模擬域直接量化成數字信號也變得越來越困難。因此,在低電壓條件下,將信號從模擬域轉換到時間域,在時間域內完成數字量化的方式廣受關注。

基于壓控振蕩器(Voltage Control Oscillator, VCO)的ADC(VCO-ADC)是一種典型的時間域ADC[4]。VCO-ADC電路具有數字化程度較高,與電源電壓演進的兼容性較好等優點,有利于ADC在低壓下工作[5]。然而,由于VCO電壓-頻率特征曲線的非線性特征,導致VCO輸出的正弦振蕩波形存在諧波,從而影響整體ADC的性能,并且隨著電源電壓的降低和對精度要求的提高,非線性問題會變得更加嚴重。

雖然采用差分結構,可以有效抑制偶次諧波和共模干擾[6],但也只能在一定程度上改善線性度,很難實現高精度。針對VCO-ADC線性度較差的問題,一般有數字校準技術[7-9]、增加反饋環路[10]和多通道相位技術[11]等多種改善方法。其中,由于數字校準技術的電路數字化程度高,工藝移植性和電壓演進的兼容性都較好。

采用最小均方根算法[12](Least Mean Squares, LMS)和Delta-Sigma ADC的數字背景線性化技術[13]能夠改善非線性,但這兩種方案均需要在較高電源電壓下實現,且均需要模擬電路的支持,電路的面積和功耗較大,不適用于低壓領域的應用。

考慮到低電壓的工作條件以及電路面積和功耗能等指標,擬設計一款基于180 nm互補金屬氧化物半導體(Complementary Metal Oxide Semiconductor, CMOS)工藝的12 bit 0.8 V VCO-ADC。VCO-ADC采用分裂ADC結構,包含兩個VCO-ADC子通道。通過向子通道中加入擾動信號的方式來使輸出中包含擾動信號信息,再使用基于查找表(Look-Up Table, LUT)的非線性數字校準算法對設計的ADC進行校準,以提高VCO-ADC的精度。

1 VCO-ADC的工作原理

VCO-ADC主要由壓控振蕩器、計數器、寄存器和減法器等模塊構成。其中,VCO將電壓域信號轉換為時間域信息,輸出的數字信號具有與輸入信號相關的頻率/周期信息,該數字信號作為計數器的計數時鐘,在一個采樣周期內完成計數,計數結果為與模擬輸入對應的數字量。寄存器完成對計數器在轉換周期內計數結果的存儲。減法器對兩個差分通道的計數結果求差,得到最終的數字輸出。

設計的VCO-ADC由兩個通道構成,其原理示意圖如圖1所示,其中,通道A和通道B由兩個完全相同的差分VCO-ADC構成,每個差分VCO-ADC由兩個完全相同的單端ADC構成。其工作原理為,Vn、Vp作為VCO-ADC的輸入信號,通過VCO產生與之對應的輸出信號,此信號將作為每個單端ADC中計數器的計數時鐘,輔助計數器完成一個采樣周期內的計數,計數器的輸出作為減法器的輸入,最終通過減法器得到差分VCO-ADC的數字輸出nA、nB。

圖1 VCO-ADC原理示意圖

2 VCO-ADC設計及校準

2.1 VCO電路設計

設計的VCO電路為一個環形電路,其電路結構結構示意如圖2所示。其工作原理為,當晶體管M7工作在飽和區時,可以將其近似當作一個壓控電流源,實現電壓到電流的轉換。由M7、M8和M9構成的電流鏡可以將輸入控制電壓Vin轉換為電流Ictrl,并且電流Ictrl的大小由輸入電壓Vin控制,從而使得環形VCO輸出頻率的快慢也由輸入電壓Vin控制,即環形VCO能夠完成從模擬輸入電壓Vin到時間域信號(頻率)的轉換。環形VCO在輸入電壓Vin的作用下,產生一段連續的正弦振蕩信號Vosc,通過反相器可將該振蕩信號轉換為相應頻率的脈沖信號VT[14]。

圖2 環形VCO電路結構示意圖

對于12位的全差分VCO-ADC,在一個轉換周期內能夠輸出的最大值為4 095,因此ADC中計數器在一個轉換周期內必須計數到4 095才能滿足要求。設計的VCO-ADC為12位5 kS/s的采樣率,經過計算,若要滿足要求,VCO最大輸出頻率應該至少大于20.475 MHz。從電路的分辨率、線性度等方面進行綜合考慮,最終確定VCO輸出頻率的范圍為15~50 MHz。

2.2 計數器電路設計

計數器通常分為異步計數器和同步計數器兩種。考慮到異步計數器在面積和功耗方面較同步計數器都具有明顯優勢[15],因此選用異步計數器來實現計數功能。在一個轉換周期內,理想情況下的12位VCO-ADC中的VCO輸出脈沖信號可以通過12位計數器完成計數,但是,通過仿真發現,VCO的輸出頻率范圍為16.58~40.89 MHz,超出了12位計數器的計數范圍,如果繼續使用12位的計數器,會帶來ADC輸出碼溢出的不良后果,為了防止這種情況的出現,采用13位加法計數器。13位計數器的電路結構示意圖如圖3所示,其中,VT為輸入信號經過VCO輸出的脈沖信號;作為計數器的計數時鐘Vclk為ADC的時鐘信號,其完成對計數器的復位。13位計數器舍棄最低位,剩余位作為單端ADC的數字輸出依次為D11、D10、…、D0。

圖3 加法計數器電路結構示意圖

2.3 寄存器電路設計

作為一種邏輯記憶電路,寄存器具有暫時存儲數據的功能[16]。在VCO-ADC的一個轉換周期內,計數器會不斷輸出計數結果。只有當一個轉換周期結束時,計數器的輸出才為ADC的最終數字輸出。寄存器的作用就是對數字輸出進行暫時的存儲,因此在計數器之后加入12位寄存器。在第n個轉換周期的Vclk來臨之前,寄存器存儲計數器的輸出,得到第n-1個轉換周期內ADC的輸出,完成一次模數轉換。當第n個轉換周期的Vclk來臨時,寄存器保存第n-1個轉換周期內的計數結果。在Vclk作用下,計數器復位,并且開始計數第n個轉換周期內VCO的輸出頻率,以此類推,重復上述步驟,直到下個轉換周期Vclk到來時,寄存器被復位,存儲第n個轉換周期內計數器的計數結果,實現對每個轉換周期內數字輸出碼保存一個周期的功能。

圖4 寄存器電路結構示意圖

2.4 減法器電路設計

每個通道的VCO-ADC均采用差分的形式進行設計,每個通道的兩端輸入Vn、Vp通過ADC得到數字輸出碼nA、nB之后,通過12位減法器對數字輸出碼進行處理,實現差分功能,得到VCO-ADC的最終輸出Dout。

12位減法器中Vclk為時鐘信號,Ai、Bi分別為計數器A、B的第i位通過寄存器A、B之后的保存值,作為減法器的輸入信號。Li-1為第i-2向第i-1位的借位值,即低位向本位借位的值,Li為第i位向第i+1位的借位值,即本位向高位借位的值,Si為第i位減法器的輸出值[17]。單端ADC的輸出都會隨輸入的變化而變化,所以減法器的輸出也是變化的。當輸入Vn小于Vp時,Ai、Bi相減得到負數,而減法器并沒有分辨正負數的功能,所以最高位S11的結果由第12位減法器的借位輸出信號與VDD經過異或門的結果決定,最終得到S11。12位二進制減法器的電路結構示意圖如圖5所示。

圖5 減法器電路結構示意圖

3 仿真結果與分析

3.1 各模塊仿真

3.1.1 環形VCO仿真

環形VCO的周期穩態(Periodic Stead State, PSS)電壓/頻率特性的仿真結果如圖6所示。可以看出,環形VCO的電壓輸入范圍為0.54~0.76 V。在整個輸入電壓范圍內,輸出頻率隨輸入電壓的增大而變快,仿真得到的輸出頻率范圍為16.58~40.89 MHz,大于至少需要達到的輸出頻率。

圖6 環形VCO的電壓/頻率特性曲線

3.1.2 計數器電路仿真

設計VCO-ADC的采樣率為5 kS/s,即采樣周期為200 μs,給定VT為一個1 μs的脈沖信號,設定Vclk為200 μs。異步加法計數器電路的仿真結果如圖7所示。可以看出,在每個采樣周期內,13位計數器的理想結果本應為199,經過舍棄最低位的值之后,得到計數器的最終結果為99。

圖7 異步加法計數器電路的仿真結果

3.1.3 寄存器電路仿真

寄存器在采樣點處對計數器的輸出進行存儲,并對計數結果完成一個周期的保存。將計數器電路與寄存器電路相連之后,寄存器電路的仿真結果如圖8所示。圖中的D11、D10、…、D0分別為計數器各個位的輸出,Dout為計數器對VCO的輸出信號計數的結果,即ADC的數字輸出。

圖8 寄存器電路的仿真結果

從圖中8可以看出,在0時刻,計數器的輸出為0,寄存器保存了此時計數器的輸出結果,并在0 μs~200 μs這個采樣周期內輸出0,在下一個采樣時鐘來臨時,計數器完成復位并開始重新計數,寄存器輸出并保存了輸出結果。

3.1.4 減法器電路設計

將寄存器與減法器相連之后減法器電路的仿真結果如圖9所示。其中,D11、D10、…、D0分別為減法器的12位輸出,DA、DB分別為差分結構中兩個寄存器的輸出,Dout為連接減法器的12位寄存器的最終輸出結果。

圖9 減法器電路的仿真結果

圖9中12位減法器運算結果的Dout數據以16進制數的形式表示,為方便計數,需要將Dout轉換為十進制表示形式Dout1。另外,由于12位減法器中存在異或門,還需要將Dout1經由異或門實現為Dout2,Dout2由DA、DB的差值加2 048得到,減法器十進制表示及異或門實現結果如表1所示。

表1 減法器十進制表示及異或門實現結果

3.2 VCO-ADC仿真分析

基于180 nm CMOS工藝,設計了12位0.8 V的VCO-ADC。其整體電路由兩個通道組成,版圖如圖10所示。在整體電路版圖設計中,兩個電容放在最左邊的部分,具有對稱性的差分輸入線Vinn、Vinp在兩個電容之間進行走線。為了保證匹配性和對稱性,將兩個單端VCO-ADC進行對稱擺放,為了避免模擬電路與數字電路之間噪聲的干擾,將每個模塊都用保護環包圍。版圖總面積為309.26×103.01 μm。

圖10 差分VCO-ADC電路版圖

使用Verilog HDL硬件描述語言進行校準算法設計,參考文獻[7-9],采用了基于查找表LUT的非線性數字校準算法,提取寄生參數完成后仿真,生成校準算法的輸入。在Quartus II軟件平臺上,采用Cyclone IV系列的現場可編程門陣列(Field Programmable Gate Array, FPGA)開發板對校準算法進行硬件驗證。

VCO-ADC校準前、后的頻譜圖分別如圖11和圖12所示。

圖11 校準前VCO-ADC的頻譜圖

從圖11中可以看出,雖然采用差分結構有效抑制了偶次諧波,但受VCO非線性的影響,三次諧波依然明顯,經過校準后,VCO的三次諧波有所減弱,如圖12所示。

圖12 校準后VCO-ADC的頻譜圖

校準前后VCO-ADC的電路信噪失真比(Signal to Noise and Distortion Ratio, SNDR)和無雜散動態范圍(Spurious Free Dynamic Range, SFDR)值隨電源電壓變化曲線如圖13所示。可以看出,隨著電源電壓的增大,校準前SNDR和SFDR曲線總體呈較明顯的上升趨勢,而校準后SNDR和SFDR曲線相對平緩,且與校準前相比,校準后SNDR和SFDR提升至70 dB和80 dB左右,提升幅度較明顯。

圖13 校準前后SNDR和SFDR隨電源電壓變化曲線

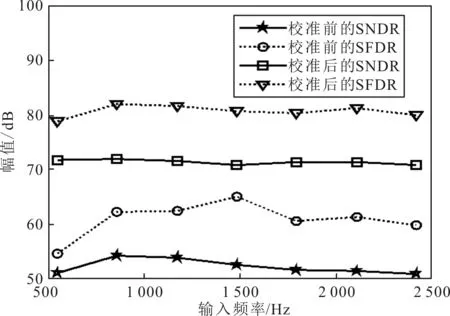

設定電源電壓為0.8 V,校準前后VCO-ADC的SNDR和SFDR隨輸入信號頻率變化曲線如圖14所示。可以看出,與校準前相比,校準后SNDR和SFDR相對平緩,且校準后SNDR和SFDR分別提升至70 dB和80 dB左右。特別是,在0.8 V電源電壓條件下,當輸入信號頻率為834.96 Hz時,校準前、后電路的SNDR從46.78 dB提升為70.27 dB,SFDR從47.45 dB提升為78.21 dB,提升幅度較明顯。

圖14 校準前后SNDR和SFDR隨輸入頻率變化曲線

另外,在線性特性方面,校準前、后的微分非線性(Differential nonlinearity, DNL)和積分非線性(Integral nonlinearity, INL)值分別從0.43 LSB和1.15 LSB降低為0.34 LSB和0.65 LSB。在精確度方面,有效位數(Effective Number of Bits, ENOB)從7.48 bit提升至11.38 bit。

所提設計與文獻[12]和文獻[13]方法的設計性能參數對比如表2所示。可以看出,設計的最大優勢是能夠在電源電壓為0.8 V條件下工作,而其他兩種設計工作的電源電壓較高。另外,所提設計的電路面積較小、功耗較低,這是因為其他兩種數字校準算法均需要模擬電路的支持,會增加電路面積、功耗和電路設計的復雜度。

表2 不同設計方法的性能參數對比

4 結語

利用180 nm CMOS工藝設計了一款12 bit的VCO-ADC。ADC采用分裂結構,包含兩個VCO-ADC子通道。利用偽隨機方式向子通道中加入擾動信號,使用查找表方法對VCO-ADC的輸出進行數字后臺校準。仿真結果表明,所提設計能夠在0.8 V電源電壓條件下工作,且ENOB和SFDR較小。另外,設計電路的面積和功耗較低。