雜質縱向高斯分布UTBB-SOI MOSFET的虛擬陰極閾值電壓解析模型

韋素芬,陳紅霞,李詩勤,黃長斌,劉 璟

(1.集美大學海洋信息工程學院,福建 廈門 361021;2.瑞芯微電子股份有限公司,福建 福州 350003)

0 引言

延續摩爾定律(More Moore)仍是當今集成電路技術發展的主要方向之一[1-2]。UTBB-SOI MOSFET不但具備傳統FD-SOI MOSFET電流驅動能力高、消除kink效應等諸多優點;而且相比傳統FD-SOI MOSFET來說,UTBB-SOI MOSFET還有更陡峭的亞閾值斜率[3]、更出色的短溝效應抑制能力、更顯著的背柵對閾值電壓和電流的調控能力[4]、更強的抗輻射能力、更好的耐高溫性能。因此在延續摩爾定律時代,在高速、低壓低功耗納米集成電路應用中,具備出色的發展與應用前景[5]。

閾值電壓是MOS器件解析模型中的重要模型參量,對器件的直流特性、頻率特性和開關特性等具有重要影響。一直以來,從傳統FD-SOI器件[6-7]到UTBB-SOI器件[8],閾值電壓模型一直是國內外的研究熱點。目前,大多數關于UTBB-SOI MOSFET的研究都假設雜質在超薄體區均勻分布,然而無論是對于長溝重摻雜的器件,還是短溝輕摻雜或極輕摻雜的器件,這樣的假設與實際工藝步驟之后產生的器件雜質分布特性都不相吻合,尤其是對于體區輕摻雜的UTBB-SOI器件而言,減少摻雜濃度的目的不僅是為了提高遷移率,也是為了盡量減小摻雜濃度不均勻對于器件電特性的影響。但,即使摻雜濃度降低到了1014~1015cm-3數量級,摻雜濃度的輕微不均勻特性仍會對納米器件特性產生不可忽略的影響[9]。溝道非均勻摻雜對器件特性的影響隨著尺寸的縮小而更顯著。因此,研究體區雜質非均勻摻雜對器件閾值電壓的影響有著重要的實際意義。

1 縱向離子注入及快速熱退火與高斯函數的對比

n溝UTBB-SOI MOSFET器件結構如圖1所示。x軸方向為沿源/溝道界面的垂直方向,y軸方向為沿柵-柵氧化層界面的水平方向;toxf、tsi、toxb、tsub、xd_sub是柵氧層、硅膜、埋氧層、襯底的厚度及襯底內耗盡層深度;L為溝道長度;NSD為源漏區摻雜濃度,NB(x)為硅膜摻雜濃度,NSub為襯底摻雜濃度;VD、VS、VG、VSub分別為漏、源、柵、襯底偏置電壓;器件的源端接地。在模擬時假設:n+型源漏區雜質呈均勻分布,p型襯底雜質呈均勻分布,輕摻雜p型硅膜內雜質呈橫向(y軸方向)均勻分布。

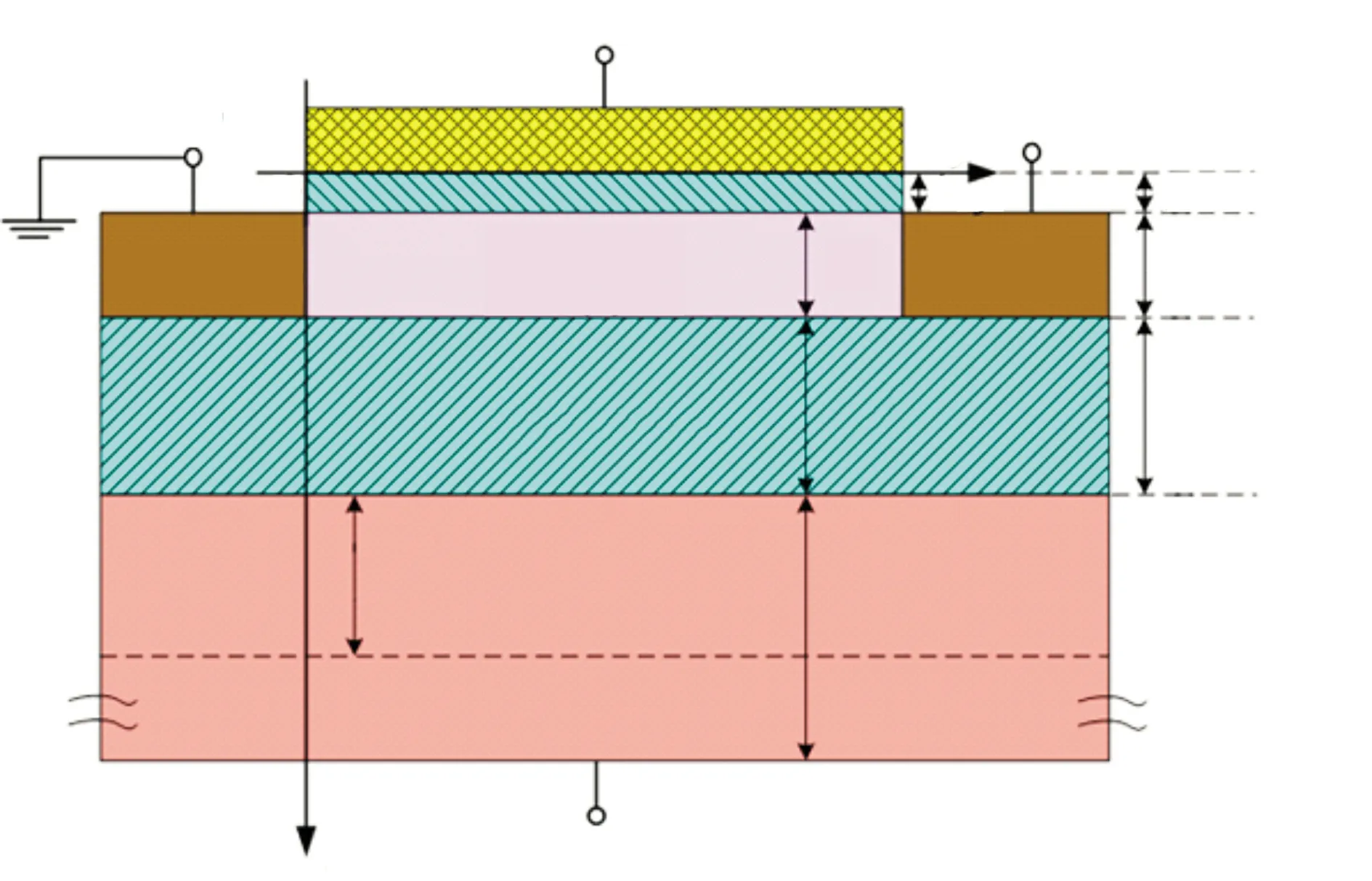

本研究的UTBB-SOI MOSFET的超薄硅膜基于智能剝離(smart-cut)技術形成。將器件厚度定為:tsi為8~25 nm;toxb為10~30 nm;toxf為1~3 nm。p型襯底摻雜濃度為1×1017cm-3,源區與漏區摻雜濃度為2×1020cm-3。對UTBB-SOI MOSFET來說,硅膜通常采用輕摻雜。為使得輕摻雜UTBB-SOI MOSFET的p型硅膜內的雜質分布與實際工藝相符,基于實際輕摻雜時硼注入的劑量和能量,先進行縱向無晶圓自轉的硼離子注入,后繼一次快速熱退火。使用工藝模擬軟件Sentaurus Process對以上工藝步驟進行模擬,對所形成器件硅膜內的雜質縱向分布規律進行曲線化擬合和分析。工藝模擬與曲線擬合結果分別如圖2所示。

在工藝仿真分析UTBB-SOI MOSFET的摻雜特性變化時,固定柵氧與埋氧厚度:toxf=2 nm,toxb=30 nm;改變硅膜厚度:tsi=8 nm,tsi=25 nm。針對這兩種不同硅膜厚度,分別調整硼注入的劑量和能量,進行四次縱向離子注入,以產生不同的摻雜分布特性,硅膜內的平均摻雜濃度保持在1014~1015cm-3數量級。每次離子注入均有后繼一次2 s的快速熱退火。在圖2中,離散點為工藝仿真軟件Sentaurus Process所計算出的縱向雜質分布點,實線為對應離散點圖形采用Origin工具所擬合的高斯函數NB(x),其表達式為:

NB(x)=Np·exp[-((x-R)/σ)2/2](toxf≤x≤toxf+tsi)。

(1)

其中:R為高斯函數平均投影射程(nm);Np為高斯函數峰值(cm-3);σ為高斯函數標準差(nm)。從圖2可看出:采用垂直于溝道方向無晶圓自轉的一次離子注入,之后再配合一次快速熱退火,在硅膜內所形成的雜質在水平方向呈均勻分布,在垂直方向分布規律與高斯函數一致。因此,在本文的仿真和分析中,采用式(1)的高斯函數NB(x)表征輕摻雜硅膜內的雜質分布。

2 基于虛擬陰極的閾值電壓的定義與推導

2.1 基于虛擬陰極的閾值電壓的定義

對短溝道輕摻雜、極輕摻雜和非摻雜UTBB-SOI MOSFET,閾值電壓定義不再基于長溝重摻雜器件閾值電壓關系式中加入修正項,而是引入虛擬陰極的概念來定義閾值電壓。虛擬陰極是指正、背柵電壓作用下硅膜內電勢最小值所在的位置。在雜質縱向非均勻分布的情況下,虛擬陰極位置并不一定位于硅膜的正、背表面,而是有可能位于硅膜的內部[10-11]。

對于納米輕摻雜UTBB-SOI MOSFET,由溝道表面勢最小值等于兩倍體費米勢得到閾值電壓的計算方法被認為不再準確[12-13]。為定義短溝輕摻雜器件閾值電壓,引入虛擬陰極的概念。Fasarakis[8]提出:以衡量內部虛擬陰極點反型載流子濃度來定義閾值電壓。當虛擬陰極(即:電勢最小值處)的反型載流子濃度等于襯底深處摻雜平坦處多數載流子數目時,這時的柵源電壓稱為閾值電壓。但是硅膜內部虛擬陰極準確位置的計算過程極其復雜,在閾值電壓模型建立過程中若采用求解硅膜內部虛擬陰極點的電勢值(即:反型載流子濃度大小)來判斷是否達到閾值電壓,其工程應用性會受很大局限。

2.2 基于虛擬陰極的閾值電壓的推導

硅膜內電勢最小值所在的位置稱為“虛擬陰極”。在本研究中用到了兩個虛擬陰極的概念。一個是基于文獻[14-15]的近似:假設正、背柵電壓分別對應的虛擬陰極就位于正、背表面,稱為“表面虛擬陰極”,即正、背表面電勢最小值所在位置;另一個是指Fasarakis等[8]與Karatsori等[16]提出的將位于硅膜內部的電勢最小值的位置稱為“內部虛擬陰極”。在本文閾值電壓模型推導中使用了“表面虛擬陰極”和“內部虛擬陰極”這兩個概念,并采用“表面虛擬陰極”的y坐標近似地表征“內部虛擬陰極”的y坐標。對于輕摻雜硅膜內雜質縱向高斯分布的UTBB-SOI MOSFET,其正、背柵控制的二維電勢分布函數模型φ(x,y)采用Wei等[17]所提出的基于分離變量求解得到的硅膜內的二維電勢分布函數的表達式。定義(taxf,ymin_SF)為正表面虛擬陰極坐標, (taxf+tsi,ymin_SB)為背表面虛擬陰極坐標。正、背表面虛擬陰極的y坐標可通過分別將正、背表面勢函數對y求導數得到。

(2)

(3)

根據基于虛擬陰極的電荷面密度法閾值電壓的定義,還需要襯底深處摻雜平坦處多數載流子電荷面密度QTH。本研究中器件的襯底為超薄硅膜,在硅膜縱向摻雜不平坦,遵循高斯分布NB(x)。因此,以基于高斯函數縱向均值的平均摻雜濃度來計算QTH:

(4)

(5)

(6)

正、背柵控制的雜質縱向高斯分布的UTBB-SOI MOSFET的閾值電壓VTH為:

VTH=min(VTHF,VTHB)。

(7)

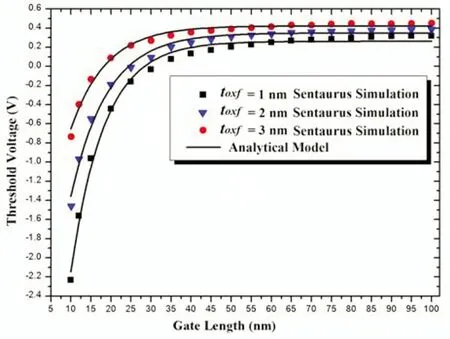

3 閾值電壓的仿真驗證

閾值電壓是由器件參數決定的,反映雜質縱向高斯分布的非均勻摻雜UTBB-SOI MOSFET各器件參數對閾值電壓的影響趨勢,并可驗證模型的正確性。本研究利用式(7)所求得的閾值解析模型,對不同的器件參數Np、R、σ、toxf、tsi、toxb以及不同VSub條件下,閾值電壓隨溝道長度的變化關系進行了計算與分析;還就不同溝道長度下,閾值電壓隨VSub的變化關系進行了計算與分析;接著,利用器件數值仿真軟件Sentaurus Device進行數值模擬,基于數值仿真得出的器件轉移特性曲線,采用最大跨導法提取器件的閾值電壓,對比模型所得閾值,進行分析和驗證。

在閾值電壓的器件仿真過程中所分析的器件是UTBB結構,仿真所采用的物理學模型為:載流子的輸運模型采用“Drift-Diffusion”模型;載流子的摻雜采用“Fermi-Dirac” 模型;載流子的產生-復合采用 “SRH and Auger Recombination Models”; 載流子的遷移率采用“Enormal Mobility Model”;仿真中計入的禁帶寬度變窄效應“band-gap narrowing effects”;通過設置MLDA 選項,考慮了體區的界面態效應。應強調的是:本研究中器件溝道長度的范圍為22~100 nm。由于溝道長度大于22 nm,故在閾值電壓模型中未引入量子效應修正項。

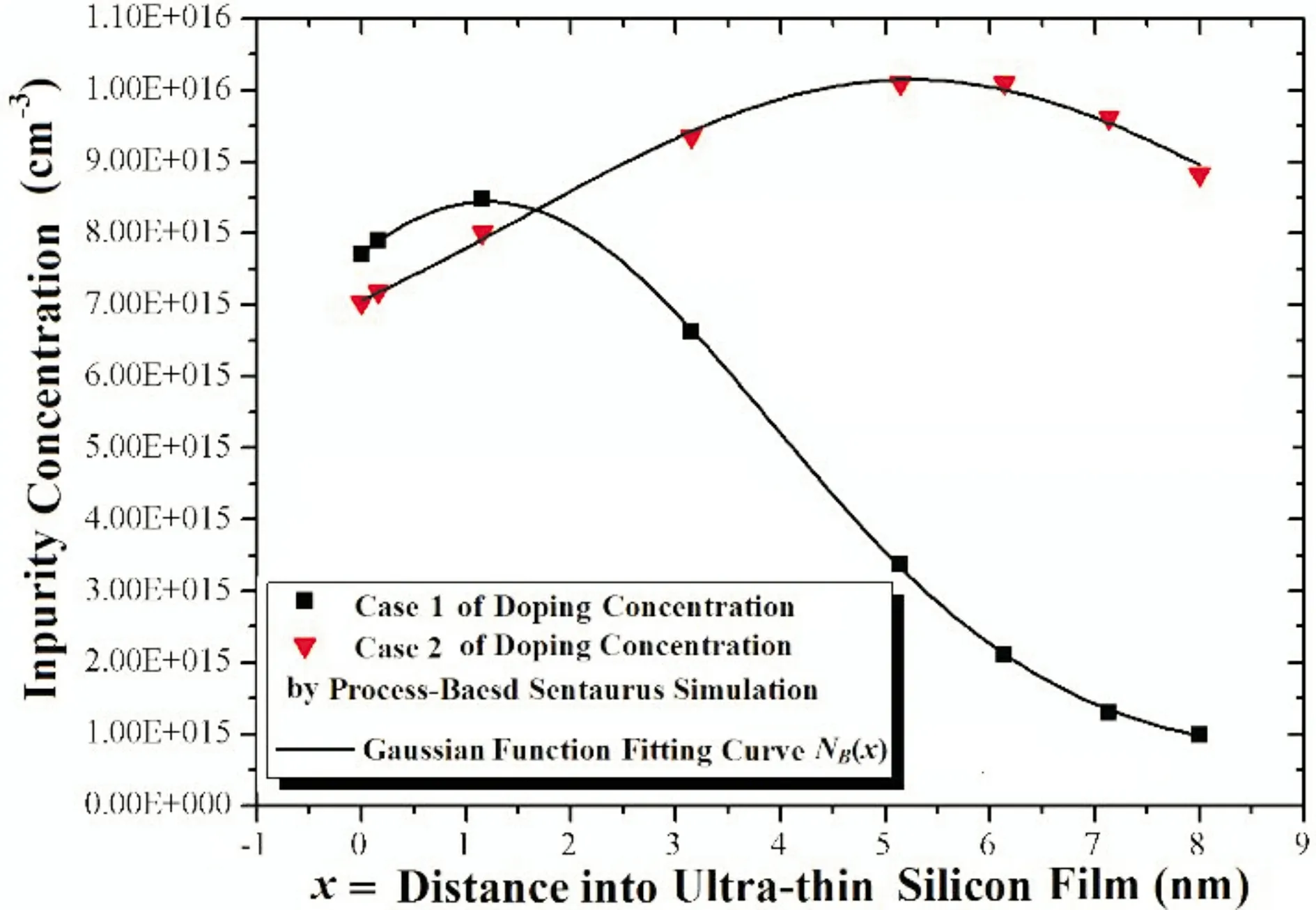

圖3~8的分析中,VDS=0.05 V,VSub=0 V。圖3~5給出在不同的柵氧層厚度、硅膜厚度、埋氧層厚度情況下,閾值電壓隨溝道長度變化曲線的改變趨勢。雜質縱向高斯分布函數的峰值Np=9.48×1014cm-3,平均投影射程R=15.75 nm,標準差σ=4.62 nm。

圖3給出toxf改變時閾值電壓隨溝道長度變化的關系曲線。在改變toxf時,固定tsi=15 nm、toxb=20 nm。從圖3可以看出:1)在同一個溝道長度節點上,閾值電壓隨著柵氧層厚度的減小而相應減小。2)不論toxf為何值,當溝道長度減少時閾值電壓都減少。相較而言,當柵氧層相對較薄的時候,閾值電壓隨溝道長度減小而減小的趨勢更加急劇;當柵氧層變得略厚時,若溝道長度變短,閾值電壓減小的趨勢會變得緩慢一些。這是因為更薄的柵氧化層對于溝道電荷的控制能力更強,對閾值電壓的調控更靈敏。正是由于這個原因,當溝道長度變短時,UTBB-SOI MOSFET工藝的柵氧層也會比較薄。

圖4為硅膜厚度的改變對于閾值電壓隨溝道長度變化特性的影響。在改變tsi時,固定toxf=2 nm、toxb=20 nm。在同一個溝道長度的節點上,閾值電壓隨著硅膜厚度的增大而減少。因此,硅膜厚度減小相當于減小體硅器件的結深,對于短溝效應的抑制效果就越佳,這正是將體區減薄的主要原因。

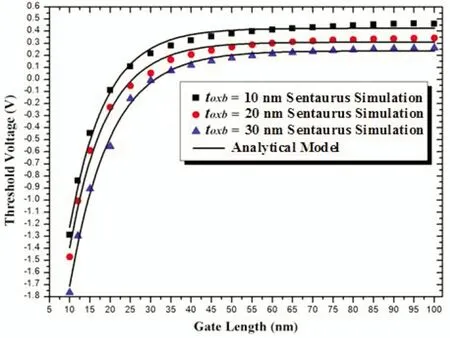

圖5為埋氧層厚度的改變對于閾值電壓隨溝道長度改變特性的影響。改變toxb時,固定toxf=2 nm、tsi=15 nm。由圖5可見:閾值電壓隨著埋氧層厚度的減少而增大;而且,埋氧層的厚度越薄,在納米溝道的范圍內,閾值電壓隨溝道長度的減少而減少的趨勢相對越平緩。由此可以看出,減薄埋氧層的厚度,可以在一定程度上減少源、漏與襯底之間的耦合[15-16],因此可以更好地抑制短溝效應。這也是將埋氧區減薄的原因。

圖6~8給出了當雜質縱向高斯摻雜特性改變時,閾值電壓隨溝道長度變化曲線的改變趨勢。固定toxf=2 nm,tsi=15 nm,toxb=20 nm。圖6為在不同高斯峰值的條件下,閾值電壓隨溝道長度而改變的特性曲線的變化趨勢。在改變Np時,固定R=15.75 nm,σ=4.62 nm。由圖6可看出:1) 高斯峰值越大,溝道中雜質整體摻雜濃度越大,因此,在各溝道長度節點上閾值電壓值也就相應地越大,在這一點上和雜質均勻分布時一致;2)隨峰值增加,整體摻雜濃度增加,閾值電壓漂移(threshold roll-off)會略微減緩。

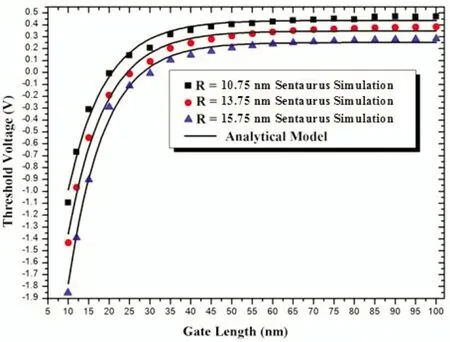

圖7為在不同的高斯平均投影射程的情況下,閾值電壓隨溝道長度而改變的特性曲線的變化趨勢。在改變高斯分布函數的平均投影射程時,固定Np=9.48×1014cm-3、σ=4.62 nm。當R越接近硅膜縱向的中心(tsi/2)時,硅膜內整體的摻雜濃度越高,閾值電壓越大。當R>(tsi/2)時,高斯分布函數的峰值會更接近硅膜的背表面,這使得硅膜正表面至硅膜中心線的整個硅膜上半部分的平均摻雜濃度比硅膜下半部分的平均摻雜濃度低,造成硅膜正表面閾值電壓小于背表面閾值電壓(VTHF

與上面相類似的情況還體現在高斯標準差σ的改變對于閾值電壓隨溝道長度變化的影響上,圖8展示了在不同高斯標準差的條件下,閾值電壓隨溝道長度而改變其特性曲線的變化趨勢。在改變σ時,固定Np=9.48×1014cm-3,R=15.75 nm。當σ增大時,硅膜內每一個位置的摻雜濃度都會減少(除了峰值濃度固定不變以外),即溝道中雜質的整體摻雜濃度減少,因此,在各個溝道長度節點上閾值電壓值也就相應地增大,在這一點上和雜質均勻分布的特性仍是一致的。

圖9~10分析襯源偏壓對于閾值電壓的影響。其中,VDS=0.05 V,Np=9.48×1014cm-3,R=15.75 nm,σ=4.62 nm,toxf=2 nm,tsi=18 nm,toxb=20 nm。圖9對比了不同的VGS與VSub偏電對于閾值電壓隨溝道長度改變的趨勢。當VGS=0.8 V,VSub=0 V時,硅膜正表面率先形成反型溝道,正表面閾值電壓是器件的閾值電壓;當VGS=0.8 V,VSub=1.5 V時,硅膜背表面率先形成反型溝道,背表面閾值電壓是器件的閾值電壓。

由圖9可見,器件在不同正、背柵壓的控制之下,閾值電壓值變化很大。因此,由于埋氧層厚度的減薄,UTBB-SOI MOSFET可利用調整背柵壓的方式實現對閾值電壓動態、有效的調制。

圖10展示了當器件溝道長度L分別為22 nm、40 nm、70 nm時,閾值電壓隨襯源偏壓VSub而改變的曲線。可看出:無論溝道長度等于22 nm、40 nm,還是70 nm,隨著VSub從-7 V增大到+1 V,閾值電壓都呈現出線性減小的關系,而且三種溝道器件的曲線的線性度都比較好;隨著溝道長度減少,曲線的線性度會略微變差一點。這說明在VSub的影響下,硅膜的背界面形成反型溝道時,影響背溝道的短溝效應不是很明顯。

由圖3~10可得出結論:在改變雜質縱向分布高斯函數特性、改變器件厚度、改變襯源偏壓的情況下,基于“虛擬陰極的電荷面密度法”對于閾值電壓的定義,推導得出的閾值電壓模型計算值與Sentaurus Device器件模擬值基本吻合。

4 結論

首先,基于形成輕摻雜超薄體的實際硼注入劑量和能量,利用工藝仿真工具,驗證了縱向離子注入后經快速熱退火所得到的雜質分布符合高斯函數特性。然后,針對雜質縱向高斯分布的UTBB-SOI MOSFET,采用“虛擬陰極的電荷面密度法”對于閾值電壓的定義,對超薄硅膜內雜質縱向高斯分布的UTBB-SOI MOSFET,推導出閾值電壓解析模型。利用該模型計算了不同器件參數(高斯摻雜平均投影射程、高斯標準差、高斯摻雜峰值濃度、柵氧厚度、硅膜厚度、埋氧厚度),以及在不同的襯源偏壓的條件下,器件閾值電壓隨溝道長度的變化關系。最后,分析在不同的溝道長度下,器件閾值電壓隨襯源偏壓的變化關系,模型計算值與Sentaurus Device數值仿真有良好的一致性。

本文所研究的硅膜內雜質縱向高斯分布是基于現行實際工藝步驟得到的真實分布規律。基于高斯分布推導出的閾值電壓模型公式,不但具備工程應用實際意義,而且求解模型的方法可以進一步應用到硅膜內具有更復雜摻雜特性的UTBB-SOI MOSFET器件上;更重要的是,在閾值電壓的計算中融入了雜質高斯分布的影響,考慮高斯分布對于器件“虛擬陰極”位置的影響,在求解虛擬陰極的位置時,采取了合理的近似。這樣既保證了模型的準確性,又兼顧了模型的工程實用性。