基于Sobel算子的實時視頻處理系統設計與FPGA實現

朱高鋒

(重慶交通大學 機電與車輛工程學院,重慶,400074)

0 引言

得益于近年計算機視覺與底層硬件電路的飛速發展,實時視頻處理與加速在通信系統、醫療成像乃至安全防護領域[1]都有重要作用。

圖像邊沿檢測算法可以提取到圖像中像素發生明顯變化的像素點,即視覺圖像中的邊緣,是實時視頻處理發展中必不可少的一環。由于視頻分辨率的不斷提高,(常規分辨率數據量),傳統邊沿提取算法在嵌入式軟件中的表現一直不佳,其實時性與功耗一直難以滿足要求[2-4],丟幀現象也時有發生。

FPGA作為可并行處理數據、硬件資源豐富的可重構系統,其特點可完美契合實時視頻處理需求[5],將視頻傳輸數據以數據流的形式傳遞與計算,并能根據圖像處理算法的變化重構硬件系統,是未來圖像處理的主流平臺之一。

本文采用OV5640攝像頭采集視頻數據,Xinlinx公司的Kintex 7系列FPGA芯片XC7K325T作為主控芯片,在Vivado2019.2上通過Verilog編寫實現了視頻圖像接收與格式轉換、圖像預處理、視頻數據緩存控制以及HDMI驅動顯示等功能。經測試,該系統可完成1280×720分辨率、30fps的圖像采集、預處理及顯示,實現了一種基于SOBEL算子的實時視頻采集與顯示系統設計。

1 系統整體邏輯方案設計

本系統采用Xinlinx公司的XC7K325T芯片作為開發平臺,作為Xinlinx廠家7系列FPGA芯片,Kintex系列與Spartan、Artix以及Virtex系列相比具有最佳的性價比。同時,作為28納米制程芯片,XC7K325T基于6輸入查找表,具有200萬邏輯單元容量,支持高達1866Mb/s的DDR3接口,25×18的乘法器、48位累加器以及預加法器的DSP片,提供了多種硬核IP等特性都十分適合視頻實時處理領域應用。外部搭載了DDR3 SDRAM大容量高速緩存芯片、HDMI接口、用于固化程序的FLASH等硬件用于實現系統功能。

系統采用自頂而下的模塊化設計方法,將FPGA內部邏輯劃分為系統初始化、圖像預處理模塊、數據交互三大模塊。其中,系統初始化模塊作用為完成對OV5640攝像頭的初始化,包含I2C通信模塊、寄存器初值存儲模塊、配置延遲模塊;圖像預處理模塊負責完成視頻圖像的預處理操作,包括RGB888轉Ycbcr模塊、中值濾波模塊、Sobel邊緣提取模塊、開操作模塊;數據交互模塊負責FPGA與外部數據交互,包括攝像頭接收模塊、視頻數據緩存模塊、HDMI驅動模塊。

系統整體邏輯方案如圖1所示。首先由攝像頭初始化模塊通過I2C接口對OV5640進行配置,主要參數配置為:分辨率1280×720、幀率30fps、輸出圖像格式RGB565、輸出接口DVP、輸出時鐘PCLK42MHz;通過圖像接收模塊對視頻進行接收的同時將圖像視頻格式轉換為RGB888輸入圖像預處理模塊;在預處理模塊中,首先將RGB888轉為對邊緣提取有益的Ycbcr格式,并經過中值濾波初步濾除圖像噪點,然后經過SOBEL算子與先腐蝕后膨脹操作完成視頻數據預處理操作;視頻數據緩存控制模塊將預處理后的視頻數據緩存入DDR3 SDRAM外部存儲器中,該模塊調用了MIG核進行片外DDR3讀寫控制,讀出的視頻緩存數據后經由HDMI驅動模塊輸出至顯示屏觀察系統設計效果。

圖1 系統邏輯框圖

2 FPGA片內邏輯設計

2.1 攝像頭配置模塊

本設計采用OV5640高清攝像頭,設置輸入時鐘XCLK頻率為24M,通過I2C接口賦值寄存器設置相關參數,I2C時鐘速率設置為400K。

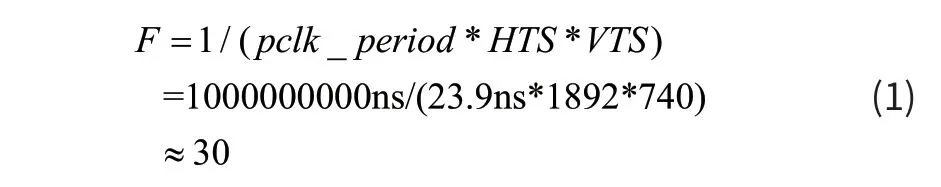

本文系統中,分辨率為1280×720,幀率設置為30fps,其中幀率由總水平輸出寬度HTS、總豎直輸出寬度VTS和輸出時鐘PCLK頻率共同決定。

攝像頭輸出接口設置為DVP接口,則攝像頭輸出分辨率為DVP輸出水平與豎直寬度,在配置文件中,攝像頭寄存器0X3808內數據bit[3:0]與0X3809內數據bit[7:0]拼接控制DVP接口輸出水平寬度,DVP水平輸出為1280,即0X3808配置為05、0X3809配置為00。類似地,DVP輸出豎直寬度為720,即0X380A配置為02,0X380B配置為D0。

0X3035、0X3036、0X3037、0X3108等多個寄存器經過倍頻與分頻操作得到輸出時鐘PCLK,本文PCLK配置為42MHz,并通過配置0X380C與0X380D設置HTS與VTS分別為1892、740。則攝像頭輸出幀率F為:

2.2 攝像頭數據接收模塊

攝像頭輸出接口配置為DVP接口,輸出格式為RGB565,即一格圖像的數據位寬為16位。DVP時序圖如圖2所示。

圖2 DVP時序圖

圖中,VSYNS為幀同步有效信號,兩個VSYNS高電平信號中間輸出一幀圖像的數據,而HREF為行同步有效信號,當HREF信號為高,接口輸出一行圖像的數據。

DVP接口的數據寬度為8位,所以當HREF信號為高時,需兩個PCLK輸出數據拼接為一位圖像數據,在拼接接收到的視頻數據的同時,將數據RGB三個通道對應的5、6、5位數據高位填0填充至8位,再將其拼接轉化為RGB888格式。

2.3 RGB888轉Ycbcr模塊

Ycbcr作為圖像色彩空間的一種格式,常用于圖像系統的編解碼中,其中Y分量代表了一格圖像的亮度成分。對于圖像來說,顏色的亮度分量在圖像邊緣處常常發生突變,更易于提取邊緣[6]。同時,通過將彩色視頻數據通過轉為Ycbcr格式,提取其中Y分量進行后續的處理,可減少圖像的數據處理量。RGB888轉換至Ycbcr公式如下:

為避免小數計算,節省FPGA內部邏輯資源,將RGB三個系數常量左移8位并量化為整數,在計算后右移8位恢復量級,并將公式中的運算分為乘積、求和、移位三級流水線以提升運算速率,同時對相應行、場同步信號做同步延遲。

2.4 中值濾波模塊

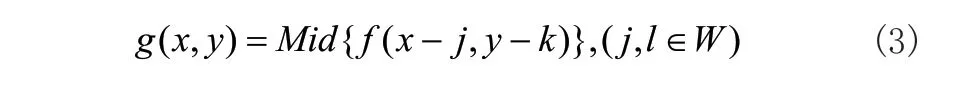

源于排序基礎理論的中值濾波法是非線性濾波方式中抑制噪聲的有效方法之一,在能有效濾除常見的椒鹽噪聲或脈沖噪聲的同時可以保證圖像信息的完整性。本文采用中值濾波是因為該方法即不會造成圖像邊緣模糊,在保留了對常規圖像濾波效果的同時易于硬件加速實現。中值濾波的原理是采用一個鄰域中的中值來替換該鄰域內其他值,其公式為:

其中,f(x,y)為圖像像素點的像素值,g(x,y)為中值濾波后的圖像像素值,W為待濾波的圖像模板。本文采用3×3的矩陣模板,即將臨近的像素點組成3×3的矩陣,并通過排序得出模板中的中值,最后將模板中的其他像素值替換為中值。

在FPGA內部邏輯實現過程中,充分利用FPGA的并行能力,通過三級流水線進行實現:

(1)將三行數據分別進行排序,得到每行數據的最大值、中間值、最小值;

(2)分別對三行數據的最大、最小與中間值進行同時比較;

(3)將三個最大值比較得到的最小值、三個中間值得到的中間值以及三個最小值比較得到的最大值進行比較,得到最后的中值。

2.5 SOBEL運算模塊

在本模塊中,將得到的灰度圖像采用3*3的Sobel算子進行水平方向與豎直方向的同步邊緣檢測。

Sobel算法第一步需采用水平算子與豎直算子與視頻每幀圖像進行卷積運算,其中的Sobel算法的水平算子Sobelx與豎直算子Sobely如式(4)、(5)所示:

對一幀圖像進行3*3的卷積運算需緩存前兩行的數據。本設計采用了Shiftram IP核對前兩行數據進行緩存,因為Xinlinx的ShiftramIP核最大深度為1088,采用深度為1024與256的兩個IP核共同緩存一行數據。

第二步需計算圖像的梯度向量G,G等于Sobel算子在兩個方向得到的卷積值Gx與Gy的平方根,即:

其中,開方采用CORDIC核進行運算,其延遲為6個時鐘周期。

第三步將得到的梯度值G與閾值比較,大于閾值則判定為邊緣,小于閾值則相反。將輸出的圖像數據值進行翻轉,即讓檢測到的圖像邊緣顯示為白色,非邊緣顯示為黑色。

本文系統中采用雙按鍵來控制Sobel閾值的加減,可使圖像輸出調整至最佳效果。

2.6 開操作運算模塊

由于SOBEL運算結果存在檢測邊緣過厚[7-8]的問題,對處理后的邊緣數據進行開操作,即先腐蝕后膨脹。開操作可以消除圖像中的細小噪點,并能平滑邊緣輪廓。腐蝕與膨脹運算與中值濾波類似,同樣采用3*3的腐蝕矩陣與膨脹矩陣模板對每幀圖像進行運算,若圖像數據生成的3*3矩陣模板為:

則對應的腐蝕輸出Geros與膨脹輸出Gexpa分別為:

將得到的輸出Geros與Gexpa替代該模板中的其他像素值,就得到了輸出圖像。

2.7 視頻緩存控制模塊

本模塊采用DDR3存儲控制器MIG的IP核輔助完成數據緩存設計。作為整個系統中的時鐘域數據交互模塊,MIG核兩側分別采用兩個FIFO分別用于MIG的讀寫數據緩存以及數據的跨時鐘域操作。MIG核輸入差分時鐘頻率為200MHz,兩側時鐘比例設置為4:1。

FPGA內部邏輯通過控制讀寫使能信號app_en、app_wdf_wren,以及觀測是否可以進行讀寫的準備信號app_rdy、app_wdf_wren進行讀寫操作,并化用乒乓操作思想,通過地址總線與BANK地址來進行視頻數據存儲位置切換,提升了實際帶寬,避免了視頻圖像拖影現象的產生。

2.8 HDMI驅動模塊

本系統采用了常規HDMI驅動芯片Sil9134作為顯示橋接芯片,通過產生1280×720的VGA時序讀取讀FIFO內的視頻采集數據,并通過Sil9134芯片轉換為HDMI接口輸送至顯示屏顯示。其中1280×720的VGA時序圖見2,通過計數器產生VSYNC信號和HREF信號,其計數時序表如表1所示。

表1 VGA時序表

表1中,當計數器在SYNC范圍內,將VSYNC、HREF信號置為高電平。而當計數器處于DISP范圍內時,將行、列有效信號置為高電平,數據有效信號DE在行、列信號同時為高時置為高電平。

3 版級調試與驗證

將代碼下載至開發板進行版級測試,初始閾值設置為23,測試圖如圖3所示。

圖3 測試原圖

采用中值濾波與Sobel算子結果如圖4所示,圖像邊緣提取過厚,且在邊緣提取后有細小噪點產生。

圖4 Sobel提取結果

加上腐蝕算法后結果如圖5所示,可以看到,腐蝕操作消除了Sobel提取后的船體體內與桅桿周圍的噪點,并削弱了檢測邊緣厚度,但將船帆的左上邊緣、船體下部陰影邊緣以及船體右側細小邊緣隔斷或濾除。

圖5 Sobel與腐蝕提取結果

加上膨脹算法后結果為圖6所示,膨脹操作將腐蝕操作細化的邊緣進行增強,并平滑了船體的邊緣輪廓。

圖6 Sobel與開操作提取結果

實驗結果顯示,本文設計系統可以較好的完成預期功能,圖像主要邊緣提取效果好,圖像噪聲較低。

4 結論

本文采用Xinlinx公司Kintex-7系列FPGA的XC7K325T芯片與0V5640高清攝像頭完成了基于Sobel算子的實時圖像采集與顯示系統設計,并通過版級調試測試了預處理算法各模塊的處理效果,驗證了系統工作正確性,為要求更高、算法更為復雜的實時視頻處理系統設計提供了參考。