具有失調抑制能力的低功耗帶隙基準電路

王紀鵬

(福州大學 物理與信息工程學院,福建 福州 350108)

0 引 言

目前,帶隙基準電壓源被廣泛應用于直流-直流(DC-DC)變換器、模數轉換器(ADC)、數模轉換器(DAC)等模擬電路中[1-2]。這些應用通常要求帶隙基準電壓源應當具有良好的精度和魯棒性,不隨工藝、電源電壓以及溫度的變化而變化。

誤差放大器的輸入失調電壓是造成帶隙基準電壓源精度下降的重要因素。傳統失調消除主要分為自歸零[3]和斬波[4]兩種方法,其中自歸零技術往往存在時鐘饋通和電荷注入等副作用,而斬波技術需要額外增加濾波器和振蕩器等電路。基于此,本文提出了一種新型帶隙基準電壓電路結構,首先對誤差放大器失調電壓的影響進行理論分析,其次驗證該結構具有較好的失調電壓抑制能力,最后基于理論分析結果設計具有結構簡單、低失調電壓以及低功耗等優點的帶隙基準電路。

1 新型帶隙基準電路分析與設計

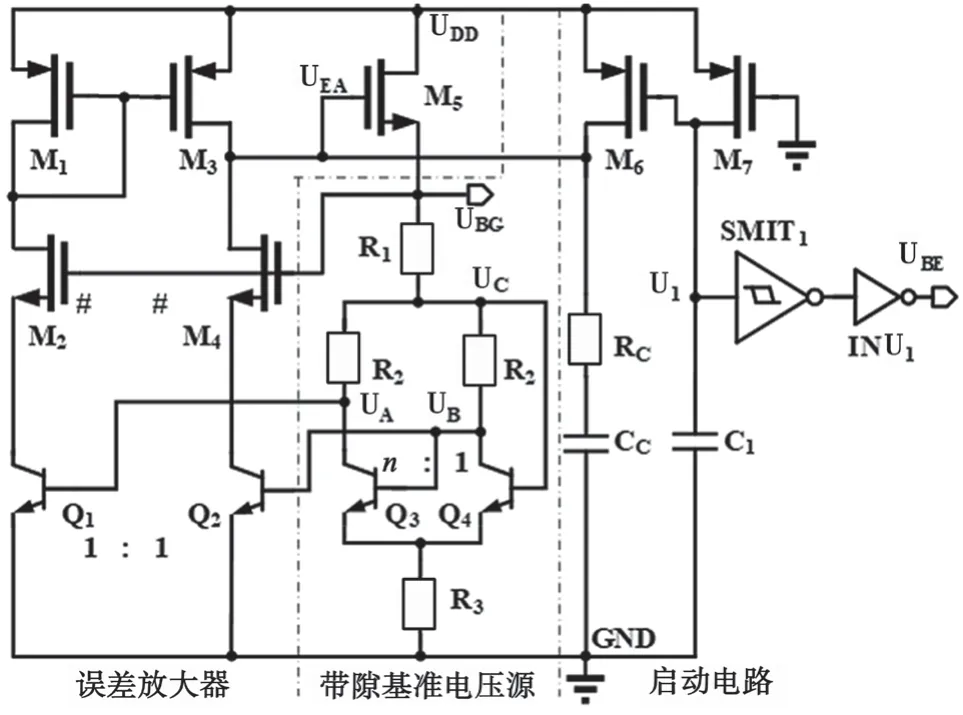

本文所提出的具有失調電壓抑制功能的帶隙基準電壓源電路如圖1所示,主要包括帶隙基準電壓源、誤差放大器以及啟動電路3部分。

圖1 整體電路結構

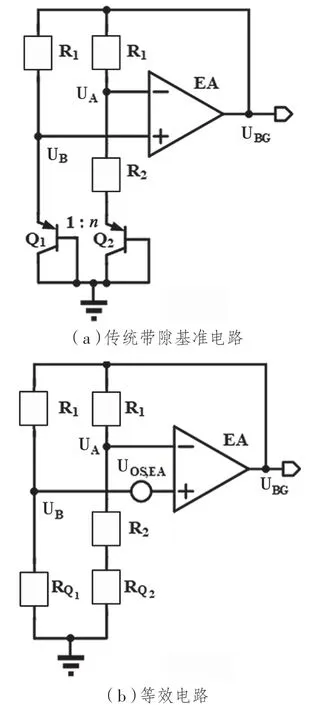

傳統的電壓模型帶隙基準電路如圖2(a)所示,主要由誤差放大器、三極管及電阻網絡構成。其等效電路如圖2(b)所示,圖中UOS,EA為誤差放大器的輸入失調電壓,RQ1和RQ2分別為三極管Q1和Q2的等效阻抗。

圖2 傳統模型

假設由于失調電壓UOS,EA造成輸出參考電壓UBG變化的變化量為?UBG,則通過電阻R1、R2、RQ1、RQ2在A點和B點造成的變化量分別為?UA和?UB。若誤差放大器的增益為Av,則由失調電壓UOS,EA引起的影響因子為:

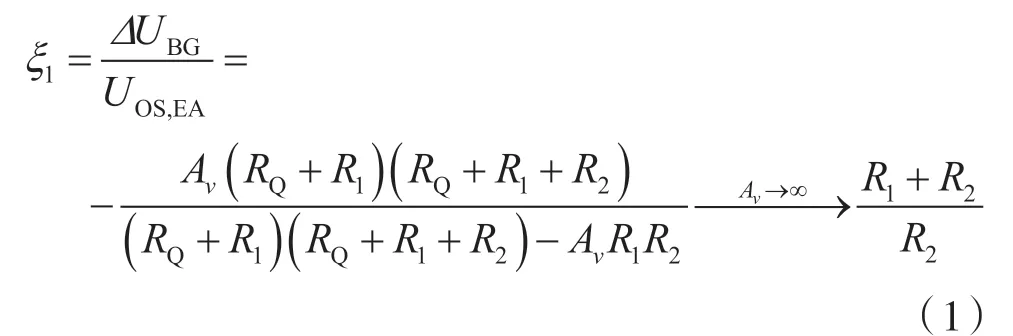

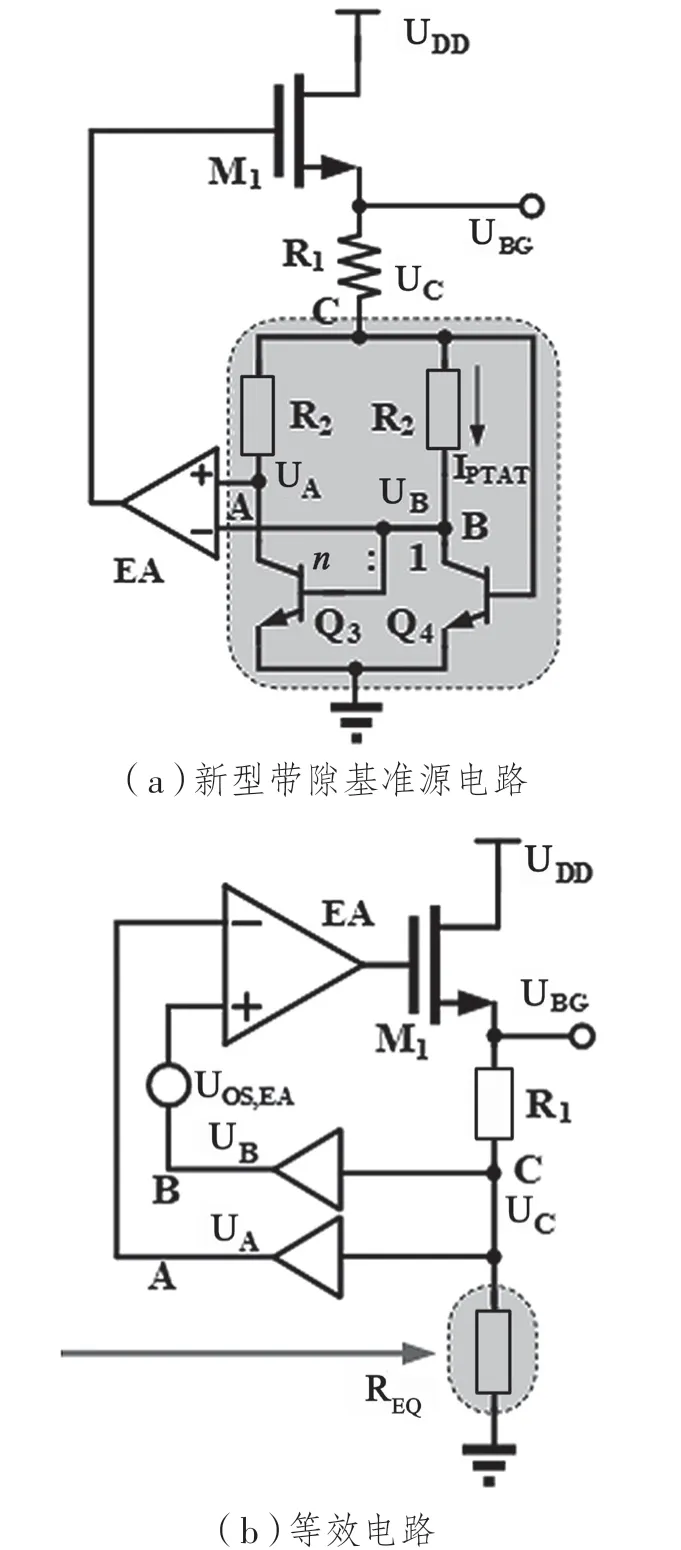

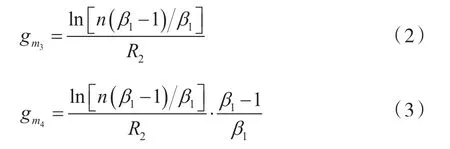

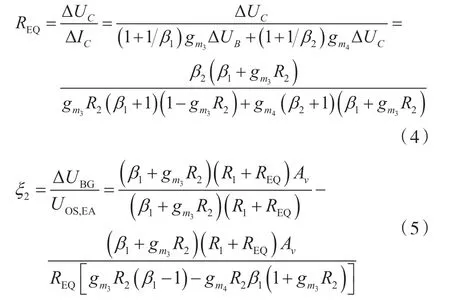

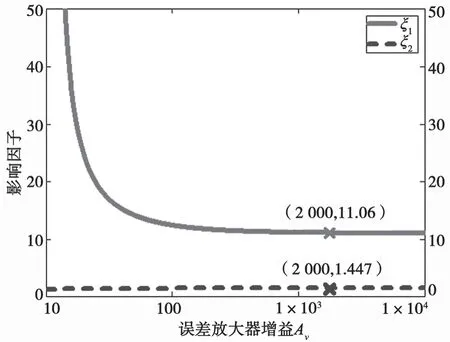

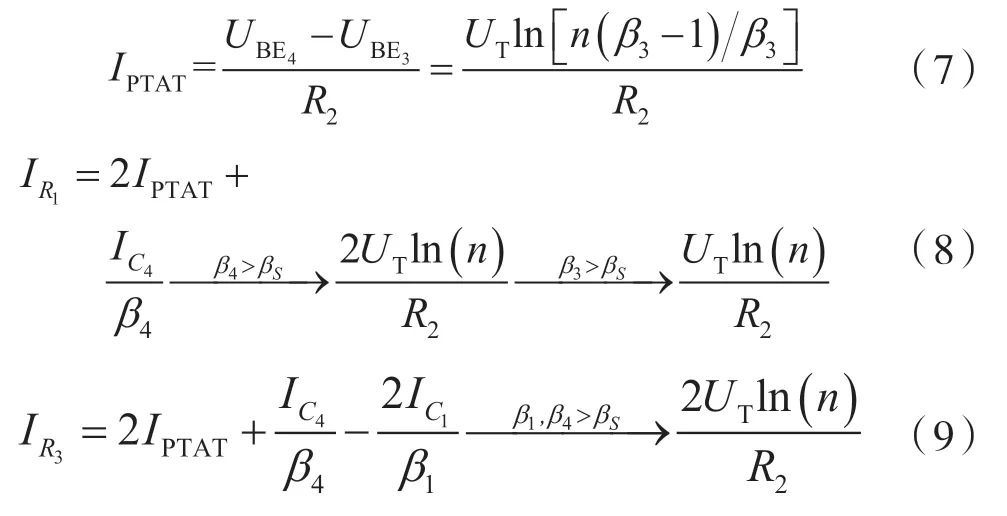

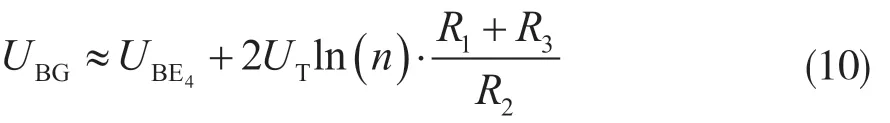

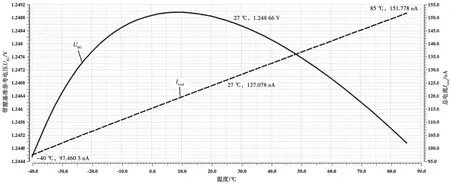

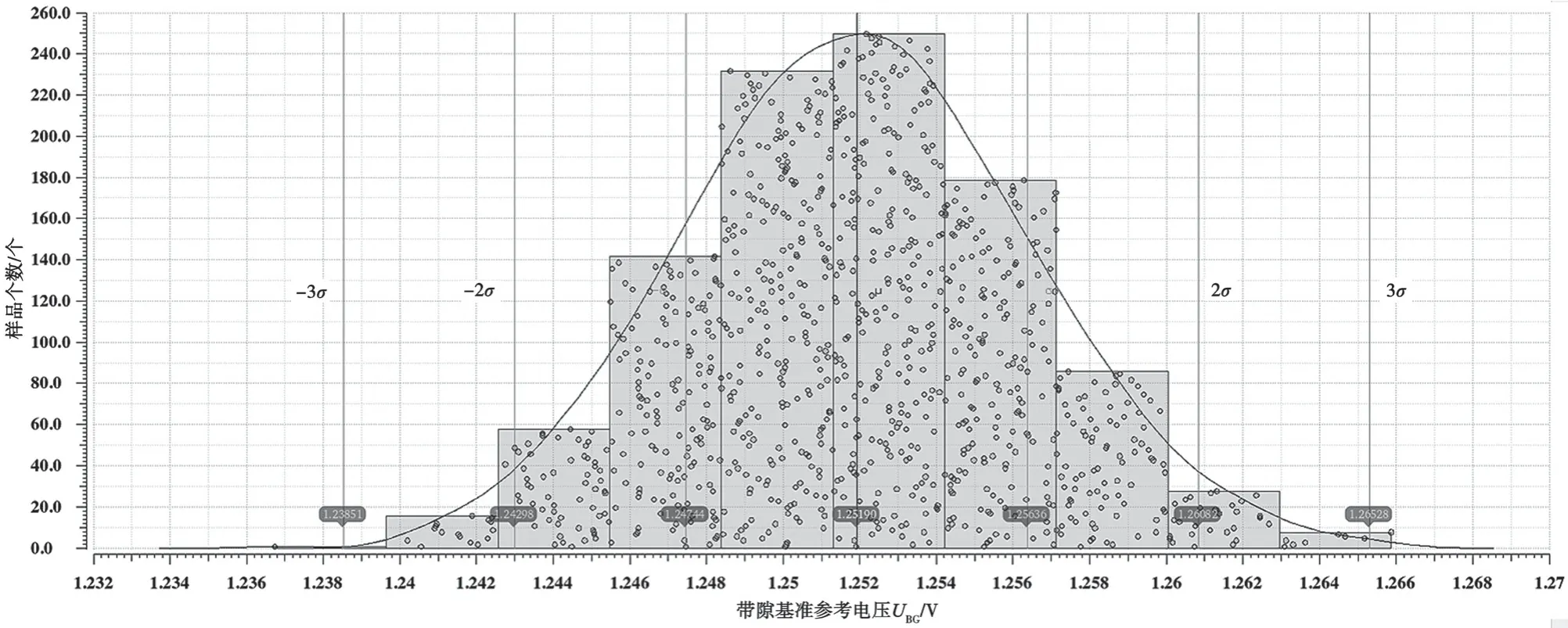

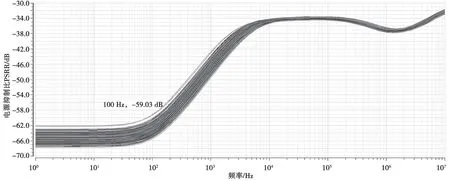

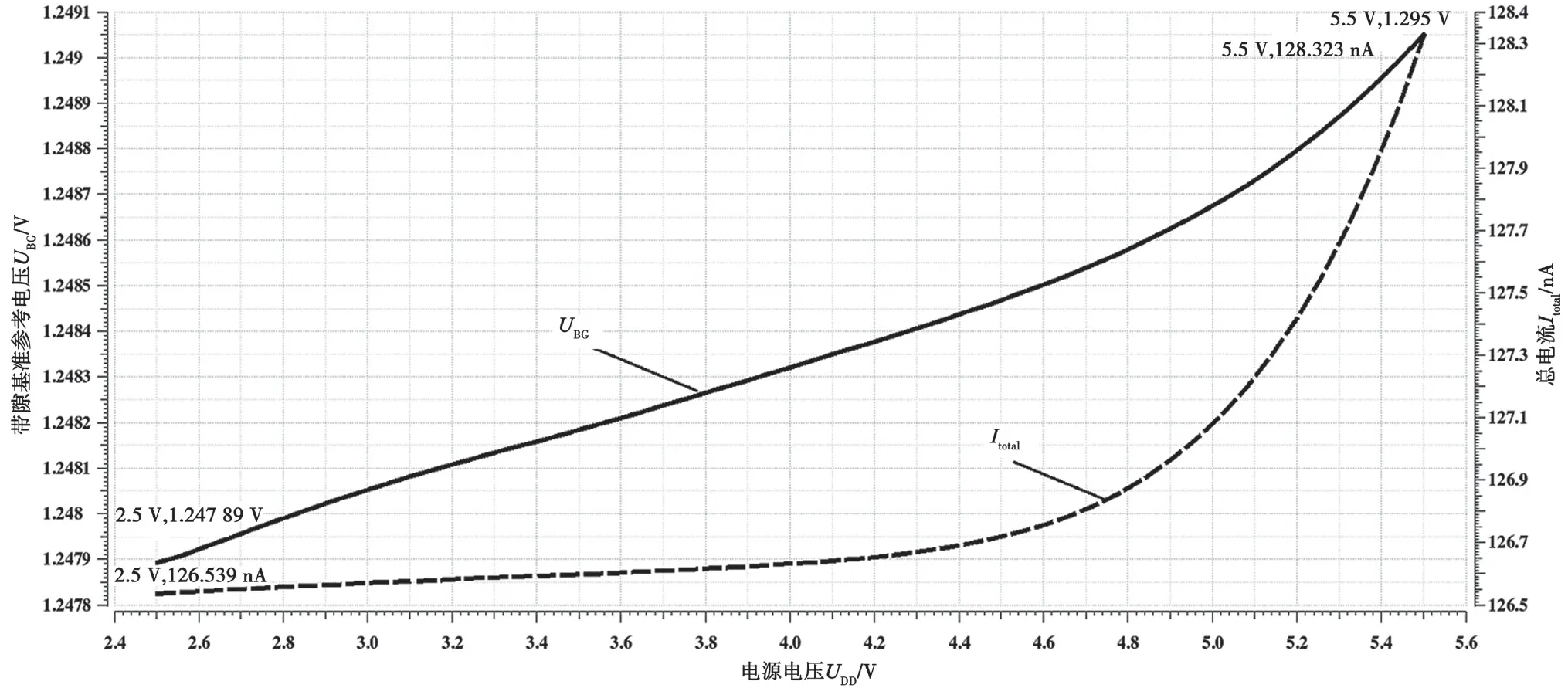

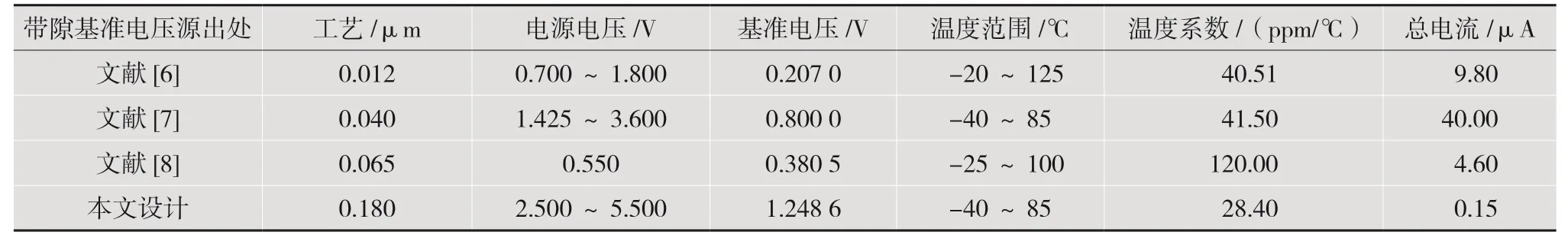

由式(1)可知,當誤差放大器增益Av足夠大且RQ< 新型的帶隙基準源電路及其等效電路如圖3(a) 和圖3(b)所示,為方便分析將電阻R2和三極管Q3、Q4等效為電阻REQ。 圖3 新型模型 假設三極管Q3和Q4的電流放大倍數分別為β1和β2,兩者的面積之比為n∶1,則對圖3(a)進行直流電流分析可得晶體管等效跨導gm3和gm4分別為: 假設失調電壓UOS,EA在A點、B點和C點所引起的變化量為?UA、?UB和?UC,在C點處的電流變化量為?IC,則等效電阻值REQ和新型帶隙基準電路的影響因子ξ2為: 本文設計的新型帶隙基準電路中三極管Q3和Q4的面積之比為8∶1,R1和R2約為5.5 MΩ和1 MΩ,影響因子ξ1和ξ2隨誤差放大器增益Av的變化情況如圖4所示。 圖4 影響因子隨增益變化 由圖4可知,在誤差放大器增益相同時,新型帶隙基準電路的影響因子遠小于傳統帶隙基準,可以降低對誤差放大器增益與失調電壓的要求,從而可以減小電路功耗和芯片面積。 三極管Q3和Q4的面積之比n和電流放大倍數β對影響因子ξ2的影響如圖5(a)所示,對REQ的影響如圖5(b)所示。 由圖5(a)可知,當n和β增加時,ξ2將減小。由圖5(b)可知,當β大于一定數值且n大于7時,REQ為負值,此時對系統的穩定性要求較高。綜合考慮系統影響因子、穩定性和器件匹配等因素,由電阻RC和電容CC構成Type II型補償電路,有效防止REQ造成系統不穩定。 圖5 面積比n對ξ2和REQ的影響 基于新型帶隙基準電路所構成的參考電壓電路如圖6所示,其基本原理是將正溫度系數的電壓和負溫度系數的電壓相疊加,從而得到與溫度無關的帶隙基準電壓[6]。 圖6 帶隙基準參考電壓電路 帶隙基準參考電壓源主體電路由三級管Q3、Q4和電阻R1、R3組成,誤差放大器電路由Q1、Q2、M1、M2、M3、M4以及M5組成。帶隙基準電壓可表示為: 當誤差放大器的增益足夠大時,由“虛短”原理可知電壓UA和UB近似相等。考慮三極管基極電流的影響,三極管Q1、Q2、Q3、Q4的電流放大倍數分別為β1、β2、β3、β4,集電極電流分別為IC1、IC2、IC3、IC4,基極電流IB為IC/β,由此產生的正溫度系數電流IPTAT、電阻R1上的電流IR1和電阻R3上的電流IR3分別為: 當三極管電流放大倍數大于特定值βS時,則三極管基極電流對帶隙基準電壓UBG的影響可忽略不計。將式(7)~(9)代入式(6)可得: 誤差放大器以三極管Q1和Q2作為差分輸入管對,具有失調電壓小、噪聲低等優點。同時通過三極管Q3、Q4和電阻R3為誤差放大器提供偏置,無需額外的偏置電路,可以減小芯片面積并降低整體電路功耗。M2和M4采用低閾值Native管,有利于Q1和Q2工作在線性區,從而確保整體電路具有足夠的環路增益。 帶隙基準電路總體芯片版圖如圖7所示,采用SMIC 0.18 μm CMOS工藝完成帶隙基準電路的設計和仿真驗證。 圖7 總體芯片版圖 圖8顯示了不同溫度下的帶隙基準參考電壓UBG和電路總電流Itotal仿真結果。 圖8 典型工藝角下參考電壓仿真結果 圖9為室溫下失調電壓1 000個樣本的蒙特卡洛仿真結果。 由圖9可知,失調電壓標準偏差值σ約為4.47 mV,參考電壓平均值μ約為1.25 V。 圖9 室溫下失調電壓仿真結果 圖10為1 000個樣本下電源抑制比(Power Supply Rejection Ratio,PSRR)的蒙特卡洛仿真結果。 根據圖10,PSRR在100 Hz處的仿真結果都優于-59 dB,表明本設計具有相對較好的電源噪聲抑制能力。 圖10 電源抑制比仿真結果 圖11為在室溫27 ℃和典型工藝角下輸出電壓和電路總電流隨電源電壓變化的仿真結果。 根據圖11,當電源電壓為2.5~5.5 V時,消耗的總電流最大約為128 μA。 圖11 不同電源電壓下的仿真結果 本文與其他文獻中的帶隙基準電壓源的性能比較結果如表1所示。 根據表1,本文設計的帶隙基準電路兼具電路結構簡單、低功耗、低失調電壓等優點。 表1 不同帶隙基準電壓源性能對比 本文介紹了一種具有失調電壓抑制的低失調和低功耗的帶隙基準電路,采用了新型帶隙基準結構,抑制了誤差放大器失調電壓的影響,無需增加額外的失調消除電路,具有低功耗、低失調電壓和結構簡單等優點。采用SMIC 0.18μm CMOS工藝完成電路設計和仿真驗證,可滿足無線網絡、便攜式可穿戴設備和生物醫療等應用需求。

2 帶隙基準電壓源電路

3 仿真結果

4 結 論