Chiplet關鍵技術與挑戰

李樂琪 劉新陽 龐健

摘要:半導體產業正在進入后摩爾時代,Chiplet應運而生。介紹了Chiplet技術現狀與接口標準,闡述了應用于Chiplet的先進封裝種類:多芯片模塊(MCM)封裝、2.5D封裝和3D封裝,并從技術特征、應用場景等方面介紹了這些封裝技術的進展。提出了未來發展Chiplet的重要性和迫切性,認為應注重生態建設,早日建立基于Chiplet的技術標準。

關鍵詞:Chiplet;2.5D封裝;3D封裝;先進封裝

Abstract: The semiconductor industry is entering the post-Moore era, and Chiplet emerges as the times require. The current status, inter? face standards of Chiplet technology, and the advanced packaging types applied to Chiplet are introduced, including multichip module(MCM), 2.5D package, and 3D package. The progress of these packaging technologies is discussed from their respective characteristics, ap? plication scenarios, etc. The importance and urgency of developing Chiplet in the future are put forward. It is believed that ecological con? struction should be paid attention to and technical standards based on Chiplet should be established as soon as possible.

Keywords: Chiplet; 2.5D package; 3D package; advanced package

近年來,半導體工藝水平的不斷提升使芯片性能得到顯著增強,但是摩爾定律正在逐漸逼近物理極限。同時,隨著中央處理器(CPU)、圖形處理器(GPU)、現場可編程門陣列(FPGA)等高性能運算(HPC)芯片性能的持續提升,人工智能(AI)、車聯網、5G等應用相繼興起[1-4],各類應用場景對高帶寬、高算力、低延時、低功耗的需求愈發強烈。為解決這一問題,“后摩爾時代”下的異構集成芯片技術——Chiplet應運而生。2015年Marvell創始人周秀文博士在2015年國際固態電路會議(ISSCC)上提出模塊化芯片概念。這是Chiplet最早的雛形。Chiplet將芯片性能與芯片工藝解耦,同時2.5D、3D等封裝技術如雨后春筍般出現。2.5D、3D封裝技術提供更高的互連密度,可以集成更多芯片模塊,有助于提升芯片效能,降低系統功耗。這也是HPC芯片開發人員采用2.5D、3D封裝技術的原因。

1 Chiplet技術現狀與挑戰

Chiplet技術是一種利用先進封裝方法將不同工藝/功能的芯片進行異質集成的技術。這種技術設計的核心思想是先分后合,即先將單芯片中的功能塊拆分出來,再通過先進封裝模塊將其集成為大的單芯片。“分”可解決怎么把大規模芯片拆分好的問題,其中架構設計是分的關鍵(需要考慮訪問頻率、緩存一致性等);“合”是指將功能比較重要的部分合成在一顆芯片上,其中先進封裝是合的關鍵(需要考慮功耗、散熱、成本等)。每款使用Chiplet技術的大芯片一定是分與合共同作用的產物。采用Chiplet技術通常有以下4個優勢:

(1)芯片可分解成特定模塊。這可使單個芯片變得更小并可選擇合適的工藝,以提高工藝良率,擺脫制造工藝的限制,降低成本。

(2)Chiplet小芯片可被視為固定模塊,并可在不同產品中進行復用,具有較高的靈活性。這不僅可以加快芯片的迭代速度,還能提高芯片的可擴展性。

(3)Chiplet可以集成多核,能夠滿足高效能運算處理器的需求。

(4)相較于更先進的半導體工藝制程,Chiplet的綜合成本更低,收益更高。

目前業內都在積極開展Chiplet的技術布局,包括Intel、AMD、Marvell等知名公司。相關產業生態鏈也在逐步完善中。2022年3月,Intel牽頭并聯合9家公司(高通、ARM、AMD、臺積電、日月光、三星、微軟、谷歌云、META)制定了通用芯粒互連技術(UCIe)標準。該標準實現了互連接口標準的統一,使不同芯片都可以通過統一的協議互連互通,大幅改善了Chiplet技術生態。

在2022年的ISSCC會議上,AMD詳細解讀了通過3D封裝實現3D V-Cache的技術。AMD應用臺積電的小外形集成電路(SoIC)技術,將V-Cache放置在CPU計算內核(CCD)上。這塊用于擴展L3 Cache的裸片(Die)不會覆蓋CPU核。通常CPU核的上方會被放置一層硅片,這樣封裝尺寸就不會發生變化,熱設計也能得到很好的滿足。通過3D V-Cache的擴展,每個CCD上的8個CPU核能共享的L3 Cache由原來的32 MB擴展到96 MB。

Intel在2019年發布了一款名為Lakefield的處理器。該處理器采用了Chiplet架構,將10 nm制程的計算Die與22 nm的輸入/輸出(I/O)Die通過Intel的Foveros技術封裝在一起。在2022年ISSCC會議上,Intel又發布了一款采用Chiplet技術的芯片Ponte Vecchio。該芯片擁有超過1 000億個晶體管,包含5類芯片,并由47個Chiplets組成:16個Xe-HPG架構的計算芯片、8個Rambo Cache芯片、2個Xe基礎芯片、11個嵌入式多芯片互連橋(EMIB)連接芯片、2個Xe Link I/O芯片和8個高帶寬存儲(HBM)芯片。這些Chiplet通過CoEMIB封裝在一起。

除了Intel與AMD等在大力發展Chiplet技術外,中國芯片企業也在紛紛布局Chiplet技術。例如,中興通訊在某個高性能CPU項目中,同樣采用了Chiplet技術。Chiplet技術主要包含高速接口技術、先進封裝技術、標準協議和生態建設。高速接口技術就如同智慧大腦中的血管技術,為數據的傳輸提供保障,它的主要指標包括能效、帶寬、時延。先進封裝是Chiplet的基石,它能使每個Chiplet小芯片連接在一起,從而構成整個系統級的芯片。標準協議可確保每家的芯片都能組合到一起,有利于互聯網協議(IP)的重復使用。生態建設決定了Chiplet技術的推廣和應用,它需要上下游各方的共同努力,以便實現良性可持續發展。然而,目前多芯片模塊(MCM)的性能、成本和成熟度仍面臨巨大挑戰。例如,MCM芯片熱流密度會逐漸增大,芯片內熱阻較大,熱點(Hotspot)現象呈現三維分布趨勢。導熱界面材料(TIM)材料和散熱蓋(Lid)材料的熱阻以及均溫性均是目前影響封裝散熱的關鍵因素。對此,業界常常采用金屬TIM或石墨烯TIM材料、真空腔均熱板散熱蓋(VC Lid)和金剛石鍵合等工藝,但這種方法面臨的封裝工藝挑戰較大,會存在鼓包、翹曲、輕微氣泡等問題。雖然芯片級液冷是未來解決大功耗芯片散熱的最佳途徑,但刻蝕工藝復雜,可靠性要求非常高,該技術目前還處于原理樣機的研究階段。

2 Chiplet接口標準

2.1 SerDes串行互連技術

SerDes串行互連技術采用差分信號傳輸方式實現了數據的高速傳輸,具有功耗低、抗干擾強、速度快的優點。根據發射端與接收端之間的距離,互連的SerDes技術可細分為長距(LR)SerDes、中距(MR)SerDes、短距(VSR)SerDes、極短(XSR)SerDes和超短距(USR)SerDes。其中,LR/MR/VSR SerDes的相關技術已經較為成熟,應用比較廣泛,封裝成本也較低,但缺點是功耗和信號的延遲比較大。XSR的光網絡論壇-通用電氣接口規范(OIF-CEI 4.0)是專門針對Die之間互連的,并向著100 Gbit/s的方向發展。相較于LR Serdes,XSR Serdes具有功耗低、面積小、通信協議靈活的特點。USR SerDes通過信號增強可進一步降低SerDes的功耗。封裝產品可以根據不同項目產品的需求選擇合適的SerDes類型,以實現成本與帶寬的平衡。

2.2并行互連技術分析

在串行互連的基礎上,各大公司技術聯盟提出了基于并行數據傳輸的物理層互連技術。其中,具有代表性的是UCIe。UCIe是Intel主推的一個開放的、多協議兼容的、可滿足不同客戶對定制封裝內多Die互連需求的技術標準。UCIe可同時支持2.5D、3D封裝技術,例如MCM、晶圓級封裝(CoWoS)、EMIB等。

UCIe 1.0使用成熟的高速串行計算機擴展總線標準(PCIe)和計算機互連標準(CXL)作為低功耗的裸片到裸片(D2D)互連物理層(PHY),可兼容多個協議,包括PCIe、CXL和Raw Mode。同時UCIe支持UCIe Retimer。這樣UCIe就能夠把互連的結構延伸到封裝外。UCIe Retimer一端采用UCIe協議,另外一端采用CXL協議,這樣可實現從封裝內互連到封裝外互連的巧妙轉換。綜合來看,這套標準可以使不同制造商的小芯片實現互通,即允許不同廠商的芯片進行混搭。不同于之前的業界并口標準,UCIe是一套完整的全棧協議,具有互操作性,并與現有的行業標準兼容,同時未來還將支持3D封裝。此外,由于協議制定單位均為業界龍頭公司(涵蓋制造、設計、應用等領域),UCIe在未來極有可能成為行業統一的標準。Intel推出該標準的目的在于建立以CPU為中心的計算生態環境。此外,NVIDIA于2022年8月宣布加入UCIe組織。Intel曾表示,未來至關重要的是一個開放的小芯片生態系統。對此,主要行業合作伙伴應共同努力,改變行業交付新產品的方式,以實現摩爾定律設定的共同目標。

中興通訊于2021年開始布局Chiplet互連互通標準,并于2022年6月向中國半導體器件標準化技術委員會半導體集成電路分會(TC78SC2)提交了標準提案。雖然Chiplet受到了業界同行的廣泛關注,但是該標準還未在國際標準組織中正式立項。鑒于UCIe的強大性,如果在流協議(各廠家可定義)的上層增加一層協議,系統就無須再使用PCIe/CXL協議。這有助于推動中國Chiplet的互連互通。

3 Chiplet中的先進封裝技術

Chiplet技術發展的基礎是先進封裝。要將多顆芯片高效地整合起來,必須采用先進封裝技術。在芯片尺寸不斷增大、架構變得復雜的情況下,封裝結構由原先的二維發展至三維。按封裝介質材料和封裝工藝劃分,Chiplet的實現方式主要包括以下幾種:MCM、2.5D封裝、3D封裝。比如,臺積電的2.5D先進封裝技術CoWoS、InFO_oS已經被廣泛應用。新的封裝形式和結構還在不斷演進。諸如SoIC的3D封裝技術將在2023年得到廣泛應用。

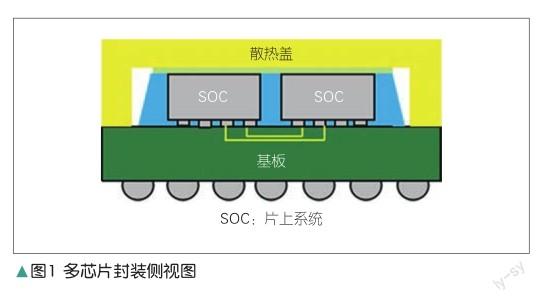

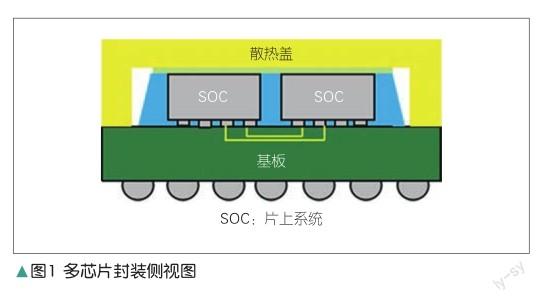

3.1 MCM封裝

MCM封裝是指通過引線鍵合、倒裝芯片技術在有機基板上進行高密度連接的封裝技術。圖1為MCM封裝的側視圖。引線鍵合與框架封裝一般用于I/O數目較少、對信號速率要求較低的情況,而倒裝芯片技術可以支持更高的信號速率、更短的信號傳輸路徑。凸塊技術用于完成芯片與有機基板的鍵合,可將多顆不同功能的芯片封裝在同一個有機基板上。基板上金屬線的互連使芯片與芯片之間的電氣進行互連。相對于硅工藝的互連襯底,封裝有機基板工藝成熟,在材料和生產成本上有巨大優勢。MCM封裝能夠滿足Chiplet芯片需求,封裝尺寸可以達到110 mm×110 mm。但受限于基板加工工藝能力,目前封裝基板上的走線寬度/間距一般為9μm/12μm。為保證銅走線的工藝控制,在設計時信號走線的線寬大多在12μm以上,布線密度比2.5D封裝低。

3.2 2.5D封裝

2.5D封裝是指在Chiplet芯片之間通過中介層(轉接板)進行高密度I/O互連的封裝,其特點是多Die集成和高密度性。根據目前的工藝水平,2.5D封裝又主要分為重布線層(RDL)Interposer和Si Interposer。

3.2.1 RDL Interposer

RDL Interposer封裝能夠通過RDL在晶圓級上使多個芯片完成電性連接。相較于MCM封裝,RDL Interposer封裝技術可以將芯片與芯片之間的距離變得更小,使信號走線寬度和間距大幅度降低,從而提高單位面積的信號密度。目前信號線寬/線距最小可以為2μm/2μm。由于芯片與芯片的間距可以做到60~100μm內,所以D2D信號互連距離可以控制在5 mm以內。相對于Si Inteposer,2.5D RDL Interposer省掉了硅通孔(TSV)工藝,具備更低的熱阻和更好的機械特性。RDL介質層采用的是高分子材料,其熱膨脹系數和基板類似,因此可以減少對Die的機械應力。圖2和圖3分別為2.5D(RDL Interposer)Chiplet芯片封裝正視圖和側視圖。另外,RDL Interposer中金屬銅的厚度可以做得更大,金屬銅的電阻率也可以做到更低,這有助于降低RDL走線的損耗。

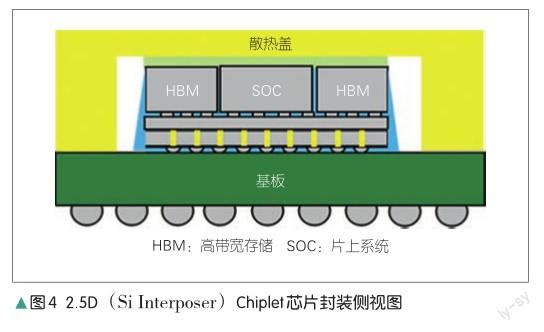

3.2.2 Si Interposer

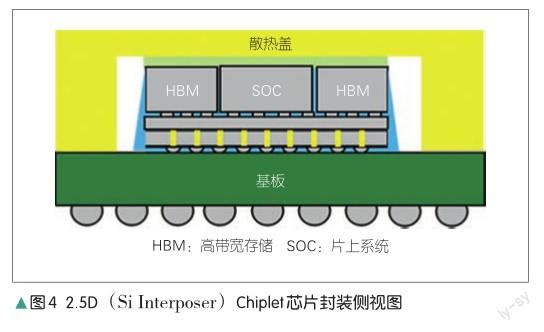

Si Interposer技術是基于硅工藝的傳統2.5D封裝技術。該技術在基板和裸片之間放置了額外的硅層,可以實現裸片間的互連通信。中介層則是在硅襯底上通過等離子刻蝕等技術制作的帶TSV通孔的硅基板。在硅基板的正面和背面制作RDL可為TSV和硅襯底上集成的芯片提供互連基礎。在硅基板上通過微凸點(ubump)和C4凸點(C4 bump)可最終實現芯片和轉接板、轉接板與封裝基板的電性能互連。圖4為2.5D(Si Interposer)Chiplet芯片封裝側視圖。目前Si In‐terposer的信號線寬/線距最小可以做到0.4μm/0.4μm。相對于RDL Interposer來說,Si Interposer的信號布線密度進一步提高,可以實現更高的I/O密度以及更低的傳輸延遲和功耗。然而與有機基板及RDL Interposer相比,Si Interposer的成本更高。目前中興通訊已有采用Si Interposer封裝技術的網絡交換芯片產品。該產品搭載HBM顆粒,可實現更優異的產品性能。

3.3 3D封裝

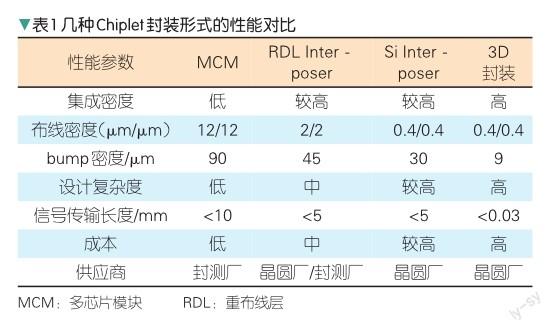

3D封裝是指在2.5D封裝技術的基礎上為了進一步壓縮bump密度,直接在晶圓上通過硅穿孔實現連接的一種封裝技術。目前3D封裝主要采用Wafer on Wafer、Chip on Wafer的混合鍵合技術。該方法能夠實現的最小鍵合距離為9μm。由于芯片本身取消了凸點,集成堆疊的厚度變得更薄,因此芯片厚度可以薄至20~30 um。這減少了芯片信號的寄生效應,提高了系統性能。表1列出了幾種Chiplet封裝形式的主要性能參數。可以看出,3D封裝是集成密度最高的。此外,三維集成電路(3DIC)也為Chiplet提供了極大的靈活性。設計人員可在新的產品形態中“混搭”不同的技術專利模塊與各種存儲芯片及I/O配置。這使得產品能夠分解成更小的“芯片組合”。其中,I/O、靜態隨機存取存儲器(SRAM)和電源傳輸電路可以集成在基礎晶片中,而高性能邏輯“芯片組合”則堆疊在頂部。此外,可以在CPU之上堆疊各類小型的I/O控制芯片,從而制造出兼備計算與I/O功能的產品;也可以將芯片組與各種Type-C、藍牙、WiFi等控制芯片堆疊在一起,制造出超高整合度的控制芯片。

3.4散熱解決方案

3.4.1 2D/2.5D方案

2D/2.5D封裝方案在散熱方面遇到的瓶頸問題是整體功耗較大。對此,業界通常采用Metal TIM或是石墨烯類的TIM材料,如圖5所示。這類材料具有較高的導熱系數(分別達到80 W·m-1·K-1和20 W·m-1·K-1),不僅能有效降低TIM自身的材料熱阻,還能降低Die內的溫差。

此外,有關Lid優化的研究也有很多,例如金剛石銅復合Lid、金剛石銀復合Lid和VC Lid。從應用前景來看,金剛石銅復合Lid和金剛石復合Lid帶來的收益比較有限,且表面工藝問題難以解決,與TIM材料的兼容性較差。由于Vapor相變層快速轉換熱量,導熱率明顯提升(約為銅Lid的4倍),因此VC Lid具有不錯的應用前景。然而,VC Lid也存在一些封裝工藝問題,例如鼓包、翹曲等。

3.4.2 3D方案

對于3D封裝結構,為了解決Die堆疊中功率密度疊加的問題,AMD采用鍵合一層結構硅(Dummy die)的方法。這不僅能起到均溫作用,還可解決因公差引起的應力問題。此外,Intel也采用相似的方案。Dummy die的材料包括Si和其他材料。近年來已有研究證明,在GaN或是SiC襯底芯片上鍵合一層金剛石,可以解決因高功率密度引起的過大溫差分布問題。如果Dummy die選擇導熱率更為優良的金剛石,那么效果會更加明顯。

除了TIM材料、系統散熱技術外,3D封裝芯片散熱方案還考慮了內部熱源問題。目前芯片級液冷技術是解決這一問題的最佳方法。美國國防先期研究計劃局(DARPA)早在2012年便啟動了芯片內/芯片間的增強冷卻(ICECool)[5]項目。在該項目中,佐治亞理工學院基于倒裝芯片架構,采用蝕刻工藝探究了芯片級液冷方案,改善了2.5D、3D芯片架構熱耦合的效果[6]。洛桑聯邦理工學院(EPFL)在2020年發表在《Nature》雜志上的文章顯示,流型通道(MCC)方案散熱能力為1 723 W/cm2@60℃[7]。

3.5電熱力耦合問題

先進封裝和系統集成技術不斷演變,不僅提高了電性能,還實現了多樣化集成,包括通過異質集成方法實現的具有多種形式的微系統。然而,相應的復雜度和可靠性問題卻變成一個更為嚴峻的挑戰。目前2.5D、3D芯片的主要應用場景包括人工智能、網絡通信、高性能計算等,其功耗通常較高。因此,如何保證電源完整性和大電流下的散熱能力至關重要。另外,復雜的封裝結構通常會包含力學特性差異較大的不同材料結構,在焦耳熱和封裝工藝下均會帶來較高的熱應力風險。因此,在基于Chiplet技術的應用過程中,由高功率電磁脈沖、芯片自熱耗散等引起的電、熱、應力等多物理效應十分突出。這需要人們探索相關仿真技術和研究方法,以便為優化設計提供指導。

基于先進集成封裝技術的多物理效應主要由電流連續性方程、熱傳導方程和彈性力學方程組等描述。焦耳熱和功率耗散等因素會引起溫度升高,產生熱變形和熱應力。變形會導致仿真模型網格發生變化,反過來會影響電場和溫度分布。另外,溫度的改變還會引起材料屬性發生變化,導致電場、溫度場、應力場發生變化。

目前芯片功耗越來越大,球柵陣列(BGA)/柵格陣列(LGA)的通流能力也在不斷提升。由此引發的系統自發熱問題不僅會影響芯片的結溫,還會對自身端子溫度產生較大影響,進而會對系統可靠性造成干擾。BGA/LGA通流仿真涉及電流、熱的協同仿真。由于BGA/LGA管腳數量較多,所需的網格量較大,并且端子較為復雜,異型結構仿真需要先做等效簡化(簡化成圓柱體),然后再做整體的電熱聯合仿真。

集成封裝的結構和材料特性十分復雜,幾何尺度跨度大,多場耦合聯動效應更為復雜,因此精確多場表征的難度較大。目前市面上有多款可用于分析多物理場耦合的商業軟件,其中比較常用的有ANSYS和COMSOL。它們都是基于有限元方法進行多物理場仿真分析的。傳統的仿真工具受限于計算機資源,無法處理全芯片模型,通常都會進行簡化或利用等效模型來處理。因此,人們需要研究針對三維集成封裝中多物理問題的高性能仿真算法。隨著Chiplet技術的不斷發展,多學科交互與協作將趨于日常化。因此,如何通過各學科人員的緊密合作對多物理場耦合現象進行更為精確的分析,將是業界共同努力的方向。

3.6 CPU Chiplet封裝實踐

在后摩爾定律時代,由制程工藝提升帶來的性能受益已經十分有限。受到縮放比例定律的約束,芯片功耗急劇上升,晶體管成本不降反升,單核的性能已經趨近極限,多核架構的性能提升速度亦在放緩。如何在先進制程之外探索一條CPU性能提升的線路,以覆蓋各種高性能計算的場景,已成為各大芯片廠商關注的問題。隨著云服務、人工智能、元宇宙時代的來臨,下游算力需求呈現多樣化及碎片化,而通用處理器不能滿足相應需求。因此,CPU也需要不斷發展與演進。這具體包括以下幾個方面。

(1)芯片定制化:針對不同的場景特點設計具有不同功能的芯片。

(2)架構優化:架構的優化能夠最大程度地提升處理器性能。

(3)異構與集成:似乎是延續摩爾定律的最佳實現路徑。例如,蘋果M1 Ultra芯片利用逐步成熟的3D封裝、片間互連等技術,使多芯片有效集成。

在CPU中可以采用2.5D先進封裝形式,利用高速并行D2D互連接口將兩個芯片通過InFO集成到一起,以構成超大規模的芯片系統。利用多層RDL的InFO結構,結合小尺寸的凸點間距,并采取2μm/2μm的線寬/線間距,可實現更高密度的帶寬。

4總結與展望

基于Chiplet的異構集成芯片技術代表了“后摩爾時代”復雜芯片設計的研制方向。Chiplet這種將芯片性能與工藝制程相對解耦的技術為中國集成電路技術的發展開辟了一個新的發展路徑。該技術借助現有成熟工藝來提升復雜芯片的性能。作為一種新興技術,當前Chiplet正處于發展階段。相關大量關鍵技術尚未形成標準。中國學術界和產業界應抓住機會,在技術研發和標準制定方面加大投入,盡快掌握核心技術。此外,芯片行業參與者需要避免單打獨斗,應注重生態建設,早日建立業界接受的基于Chiplet的異構集成技術標準,以便在未來國際競爭中占據一席之地。

致謝

本研究得到中興通訊股份有限公司謝業磊高級工程師、嚴斌高級工程師、孟福生高級工程師、譚曉東高級工程師、陳桂顯高級工程師的幫助,謹致謝意!

參考文獻

[1]劉新陽. 5G半導體產業發展和創新趨勢思考[J].中興通訊技術, 2021, 27(4): 51-51. DOI: 10.12142/ZTETJ.202104010

[2] SATO K, ZHANG X B. Semiconductor optical amplifier and gain chip used in wavelength tunable lasers [J]. ZTE Communications, 2021, 19(3): 81-87. DOI: 10.12142/ZTECOM.202103010

[3]蔡濟帆,徐增熠,遲楠.可見光通信星座整形與人工智能解調技術[J].中興通訊技術, 2022, 28(4): 19-24. DOI: 10.12142/ZTETJ.202204005

[4] ZHANG C C, ZHANG N, CAO W, et al. AI-based optimization of handover strategy in non-terrestrial networks [J]. ZTE Communications, 2021, 19(4): 98-104. DOI: 10.12142/ZTECOM.202104011

[5] BAR-COHEN A,MAURER J J,FELBINGER J G.DARPAs intra /interchip enhanced cooling (ICECool) program[C]//2013 CS MANTECH Conference. IEEE, 2013: 201-206

[6] BAR-COHEN A,MAURER J J,HAMILTON B A.DARPAs intrachip enhanced cooling program (ICECool): embedded cooling for RF and digital electronics[C]//2015 IEEE MTT-S International Mierouave Symposium. IEEE, 2015: 61-70

[7] ERP V R, SOLEIMANZADEH R, NELA L, et al. Co-designing electronics with microfluidics for more sustainable cooling [J]. Nature, 2020, 585: 211-216

作者簡介

李樂琪,深圳市中興微電子技術有限公司封測工程部封裝設計工程師;主要從事2.5D、3D先進封裝的封裝方案評估及封裝設計工作,參與并支持了多個預研項目及產品項目的設計與交付。

劉新陽,深圳市中興微電子技術有限公司副總經理,在中國通信學會集成電路專委會、中國半導體行業協會、集成電路產業技術創新戰略聯盟等多個行業協會中擔任委員或理事會理事;主管戰略規劃、技術規劃、品牌和政府公共關系,擁有24年的IC設計行業從業經驗,主持了多個重大產品的研發項目并完成批量商用交付。

龐健,深圳市中興微電子技術有限公司封測工程部封裝設計總負責人,主要負責封裝技術規劃和封裝技術預研,擁有20余年項目開發經驗,主持了多個商用產品的交付項目。