基于ZYNQ UltraScale+的高速圖像數據采集系統設計

唐宇楓,劉一清

(華東師范大學通信與電子工程學院,上海 200241)

近年來,隨著5G 技術的不斷發展,超高清顯示面臨的高數據傳輸速率問題逐漸得到解決。視頻技術正朝著超高清的方向發展[1],圖像傳感器作為超高清顯示中的數據源,其產生的圖像數據的正確采集對超高清顯示至關重要。圖像傳感器的并行DVP 接口由于使用單端信號線傳輸,數據容易受到噪聲的干擾,傳輸速率無法滿足超高清的數據傳輸速率要求。因此,在高分辨率圖像傳感器中,均使用差分LVDS 信號線傳輸圖像數據[2-5]。

文中設計了一套基于ZYNQ UltraScale+的高速圖像數據采集系統,為圖像傳感器提供了100 路LVDS信號線,圖像數據的采集速率可達160 Gb/s,滿足超高清的數據傳輸速率要求。設計的系統使用國產的圖像傳感器LN130A 進行測試,系統的核心處理器通過對圖像數據進行對齊、重排列使其變為可顯示的圖像數據,最終通過協處理器上的萬兆以太網模塊將圖像數據傳輸到上位機,實現圖像的顯示。

1 硬件設計

1.1 系統硬件概述

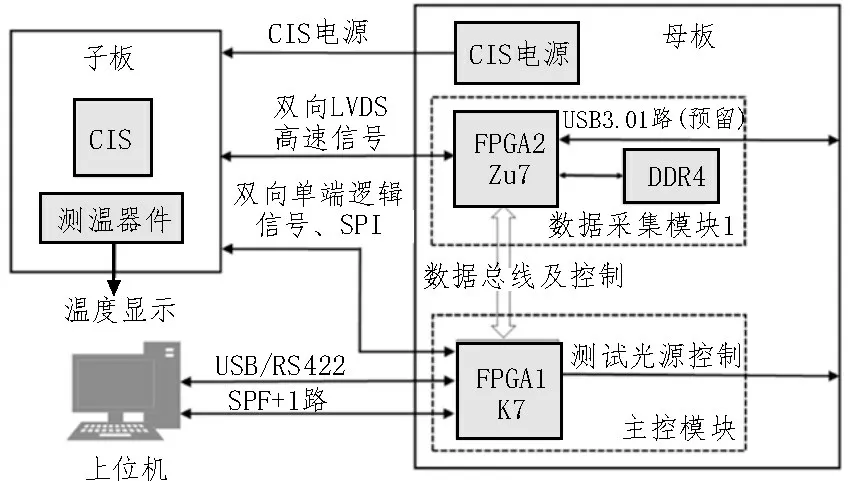

ZYNQ UltraScale+高速圖像數據采集系統由母板、子板和上位機3 個部分組成。其中母板作為系統的核心部分用于完成圖像數據的采集,為圖像傳感器提供驅動與控制信號,通過SFP+端口將采集到的圖像數據傳給上位機;子板上安裝有圖像傳感器,通過QSH 系列高速座子將傳感器輸出的圖像數據傳給母板;上位機配有標準網卡,通過SFP+端口接收母板傳來的圖像數據,并由自行編寫的上位機軟件處理和顯示圖像數據。該系統采用子板、母板的設計實現了圖像數據采集部分與圖像傳感器部分的分離。在采集不同圖像傳感器的數據時,只需要更換系統中的子板,增加了系統通用性的同時減小了更換圖像傳感器的開銷。系統框圖如圖1 所示。

圖1 系統框圖

1.2 系統母板硬件設計

系統中的母板采用Xilinx的ZYNQ UltraScale+MP SoC系列的XCZU7EV-FFVC1156-2-E芯片作為系統的核心處理器[6]。此芯片主要包含PL(Programmable Logic,可編程邏輯)與PS(Processing System,處理系統)兩個部分。其中PL 部分包含了504K 個可編程邏輯單元,1 156 個IO 管腳,能為圖像傳感器提供100 路LVDS 高速信號[7]。芯片上每一路LVDS 信號的數據傳輸速率最高為1.6 Gb/s,100 路LVDS 信號的數據傳輸速率可達160 Gb/s。PS 部分包含四核Cortex-A53 的APU(Application Processing Unit,應用處理單元)及雙核Cortex-R5 的RPU(Real-Time Processing Unit,實時處理單元),PL 與PS 間通過AXI協議總線進行數據交互。采用此芯片作為核心處理器,其上的100 對LVDS 高速信號保證了數據采集速率,同時PS+PL 的架構也使母板上的軟件開發變得多樣,使軟件開發更加靈活、高效[7]。

母板上的外圍設計圍繞核心處理器芯片的PL與PS 兩部分展開,PL 部分包含前文提到的100 路LVDS 高速信號線,其通過高速信號座子與子板相連,處理器IO 口調試時使用的LED 燈、撥碼開關、按鍵、4 路GTH 高速收發器及16路的LVDS高速信號與母板上的協處理器Kintex-7 相連。協處理器為圖像傳感器提供時序及控制信號,同時提供數據傳輸速率為10 Gb/s 的SFP+端口[8]與上位機進行數據傳輸,解決了核心處理器的SFP+端口IP 核需要付費使用的問題。PS部分包括4片8 Gb DDR4[9]@2 400 MHz高速緩存、一路SD2.0 接口、兩片128 Mb QSPI Flash、一路USB3.0 接口、一路用于打印調試信息的USB 轉UART 接口及LED 燈。母板設計以高速圖像數據的采集和傳輸為主題,支持多種圖像傳感器。文中通過采集國產CIS(CMOS Image Sensor,CMOS 圖像傳感器)芯片LN130A 的圖像數據,驗證了系統用于高速圖像數據采集的可行性。

1.3 CMOS圖像傳感器

LN130A 是一款分辨率為1 280×1 024,像素大小為9.5×9.5 μm2的具有高幀頻、高動態范圍的低噪聲CMOS 圖像傳感器。該圖像傳感器可實現卷簾快門或全局快門。LN130A 的一些基本特征如下所示。

1)分辨率:1 280(列)×1 024(行);

2)像素大小:9.5×9.5 μm2;

3)卷簾快門時,幀頻為160幀/s,讀出噪聲為1e-;

4)全局快門時,幀頻為80 幀/s,讀出噪聲為3e-;

5)可實現高動態范圍(≥90 dB);

6)積分時間可由外部調控;

7)共有4 路LVDS 圖像數據信號通路,每一路的傳輸速率均為784 Mbps;

8)具有14 bit片上ADC;

9)具有SPI 接口,用于對寄存器進行設定。

下面以采集LN130A 圖像數據為例,說明整個系統的軟件設計。

2 軟件設計

2.1 總體軟件概述

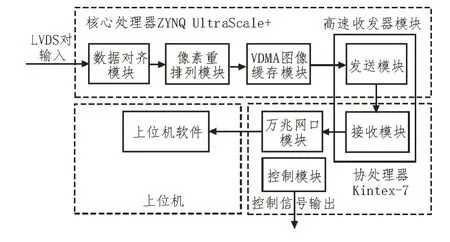

文中的高速圖像數據采集系統的總體軟件設計的功能框圖如圖2 所示。

圖2 軟件功能框圖

CIS 芯片在接收到母板上控制模塊產生的控制信號后輸出圖像數據,圖像數據通過LVDS 接口輸入到母板上的核心處理器,通過數據對齊模塊確保多路LVDS 數據信號的數據位同步及像素同步。其后的像素重排列模塊將4 路LVDS 信號上的以一定規律傳送的像素數據按照像素0 到1 280 的順序重新排列成一行圖像數據。此模塊還負責將重排列的圖像數據轉化為AXI4-Stream 格式,通過之后的VDMA模塊緩存到DDR4 中。VDMA 圖像緩存模塊緩存3幀圖像數據,使圖像能夠流暢顯示。核心處理器通過高速收發器模塊將緩存后的圖像數據傳給協處理器。協處理器上的萬兆以太網模塊將圖像數據組成UDP 協議的數據包傳到上位機,上位機中的軟件負責接收和處理圖像數據。

2.2 數據對齊模塊功能說明

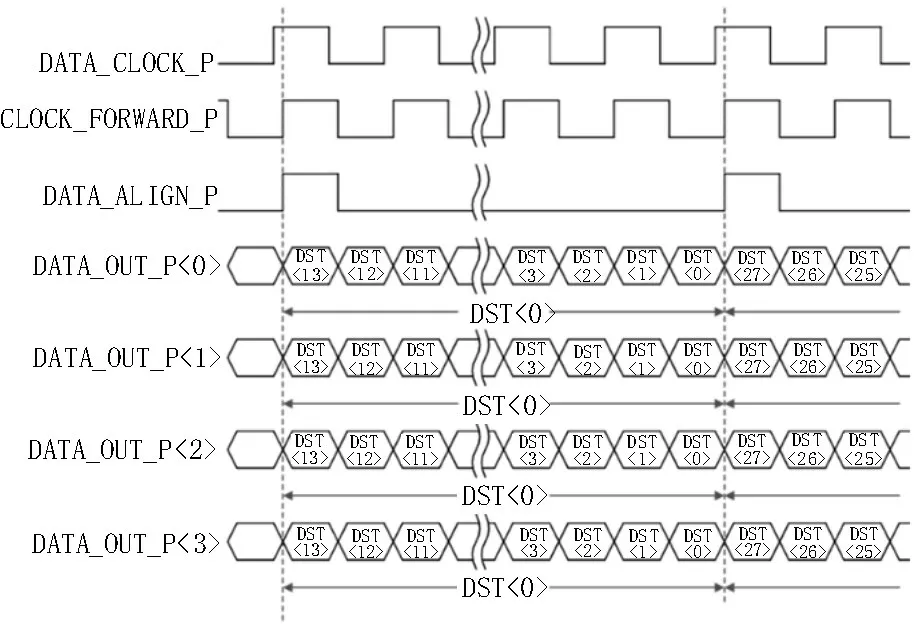

CIS 圖像傳感器輸出數據時序圖如圖3 所示,這些信號之間有著嚴格的相位關系。

圖3 圖像傳感器時序圖

其中,DATA_OUT_P<0~3>為4 路數據信號,CLO CLK_FORWARD_P 為數據時鐘,DATA_ALIGN_P 為像素同步信號。

2.2.1 數據位同步

數據對齊模塊在接收到信號后需要使用核心處理器中的ISERDES 接口硬核[10],在數據時鐘的邊沿對數據及像素同步信號采樣,并以1∶8 的比例將串行數據轉換為并行數據。使用ISERDES 硬核采樣前,還需使用核心處理器內的IODELAY 硬核調整上述信號的動態延時,確保信號間的相位關系與圖3一致,得到正確的采樣數據。

2.2.2 像素同步

在保證了數據的正確采樣后,4 路數據信號和像素同步信號在ISERDES 內的串行并行數據轉化環節也會存在不確定的延時,所以在數據同步模塊內還需要對8 bit的并行數據進行拼接,得到正確的14 bit像素值。像素同步功能使用Verilog語言進行編寫,首先將8 bit 的并行數據寫入異步FIFO 并以14 bit 的形式讀出并行數據,然后存入兩級14 bit的寄存器中,之后用這兩級寄存器中的數據排列出14 bit 數據的所有可能組合并與已知的目標序列對比,如圖4 所示。

圖4 像素同步過程

從圖3 可知,文中系統中像素同步信號在像素同步時的已知序列為14 位的二進制數1000000000 0000(b),數據信號的已知序列為14 位的DST<0>,并可以用其后接收的已知序列DST<1>檢驗像素同步的正確性。完成數據位同步及像素同步后的一行圖像數據的時序圖如圖5 所示,其中X_CLOCK 為輔助說明信號,便于讀者理解此模塊的輸出時序,其頻率為28 MHz。在一個X_CLOCK 周期內,數據對齊模塊將輸出8 個像素值(注:每個像素值均為14 bit)。

圖5 行像素時序圖

2.3 數據重排列模塊功能說明

參照圖5,數據對齊模塊的4 路14 bit 并行數據的輸出形式為DATA_OUT_P<0>上傳輸第N及N+1個像素的值,DATA_OUT_P<1>上傳輸第N+2 及N+3個像素的值,DATA_OUT_P<2>上傳輸第N+4 及N+5個像素的值,DATA_OUT_P<3>上傳輸第N+6 及N+7個像素的值,0≤N≤1 272。為了顯示圖像,一行圖像數據的像素值需要按照0~1 279 的順序重新排列。數據重排列模塊首先將4 路14 bit 并行數據拼接為一個56 bit 的數據存入異步FIFO 中,然后以112 bit的形式讀出數據,存入相同位寬的寄存器中,最后通過位拼接操作完成像素值的重排列,如圖6 所示。

圖6 數據重排列過程

2.4 VDMA圖像緩存模塊功能說明

系統中PL 端為了提供100 路的LVDS 數據接口,沒有足夠的管腳連接DDR4 存儲芯片。用于緩存圖像數據的DDR4 緩存器掛載在PS 端,因此需要使用Xilinx 公司提供的VDMA IP 核[11-12]將重排列后的圖像數據緩存到DDR4 中。VDMA 圖像緩存模塊的主體是VDMA IP 核,其為AXI4-Stream 總線形式的數據流提供了兩個DMA 通道,使PL 端的圖像數據能方便高效地緩存到PS 端的內存中,防止圖像出現卡頓及割裂現象。

數據重排列模塊輸出的圖像數據首先需要轉化為AXI4-Stream 總線形式,與VDMA IP 核的數據接口形式匹配。VDMA IP 核的寄存器主要用于設置緩存幀的起始地址及圖像行、列像素個數。文中系統使用核心處理器PS 端的AXI4-Lite 總線配置VDMA IP 核的寄存器。

2.5 高速收發器模塊功能說明

高速收發器模塊的主要功能是將緩存后的圖像數據從核心處理器傳送到協處理器,從而通過協處理器上的萬兆以太網模塊,將圖像數據傳遞到上位機進行顯示及處理。此模塊分為核心處理器內的發送模塊及協處理器內的接收模塊。

2.5.1 發送模塊

核心處理器在硬件上通過GTH收發器[13]與協處理器相連接,發送模塊使用Xilinx公司的GTH IP核發送數據。GTH收發器在Ultrascale+架構中支持500 Mb/s到16.375 Gb/s 的單通道速度,與PL 邏輯資源緊密集成。文中系統將GTH 發送器的速率設置為5 Gb/s,采用8/10 bit 的編碼方式對發送的并行數據進行編碼以降低發送信號中的直流成分,接著將并行數據轉化為串行數據,以差分對的形式將數據發送出去。

2.5.2 接收模塊

協處理器在硬件上通過GTX 收發器[14]與協處理器相連接,接收模塊使用Xilinx 公司的GTX IP 核接收數據。GTX 收發器在7 系列FPGA 中支持500 Mb/s到10.312 5 Gb/s 的單通道速度。文中系統將GTX 接收器的速率設置為匹配的5 Gb/s,對接收數據進行解碼,接著將串行數據轉化為并行數據,最后對并行數據進行像素對齊得到正確的圖像數據。

2.6 萬兆以太網模塊功能說明

萬兆以太網模塊以10 Gb/s的速率將圖像數據傳輸到上位機,文中系統使用Xilinx 公司的萬兆以太網子系統IP 核[15]實現萬兆以太網功能。此IP 核提供給用戶的數據接口為AXI4-Stream 總線形式,數據位寬為64 bit,用戶時鐘為156.25 MHz,時序如圖7所示。

圖7 萬兆以太網IP核用戶接口時序

為了減小協處理器與上位機通信時發送數據前的延時,文中系統將圖像數據組成UDP用戶數據報,并以AXI4-Steam的形式將數據流傳入萬兆以太網子系統IP核的用戶接口中,使其以10 Gb/s的速率與上位機通信。

2.7 上位機軟件功能說明

上位機軟件基于微軟的WPF(Windows Presentation Foundation)[16]進行界面設計,實現的功能有:1)將接收的14位像素值數據轉換為8位,并以bmp格式顯示圖像;2)統計顯示圖像中的像素值(8 bit圖像數據),并以直方圖的形式將結果實時顯示;3)調節圖像的亮度及對比度;4)放大顯示選中圖像區域內的原始14 bit像素值;5)以TIF 格式存儲圖像;6)錄制視頻。

3 測試及驗證

文中系統通過控制模塊的SPI 接口信號修改LN130A 芯片內寄存器的值,使其產生分辨率為1 280×1 024、80 幀/s 的灰階圖像數據,從而進行系統的圖像數據采集測試,最終的圖像數據傳遞到上位機拼接成灰度圖像進行顯示。

4 結束語

文中以Xilinx 公司的ZYNQ 作為核心處理器,設計高速圖像數據采集平臺,采樣速率可達160 Gb/s。從軟硬件兩方面現實了基于并行LVDS 接口的圖像傳感器的數據采集。文中系統采用子、母板的設計方式實現了圖像數據采集部分與圖像傳感器部分的分離,通過更換子板實現多種圖像傳感器的數據采集,具有通用性,也降低了更換圖像傳感器時的開銷,為并行LVDS 接口的圖像傳感器的圖像數據采集提供了一個可行的解決方案。