保護環對雙向可控硅靜電防護器件電容特性的影響

楊帥康 汪洋 蘇雪冰 張玉葉 楊紅嬌,

關鍵詞:雙向可控硅;保護環;寄生電容;傳輸線脈沖測試系統

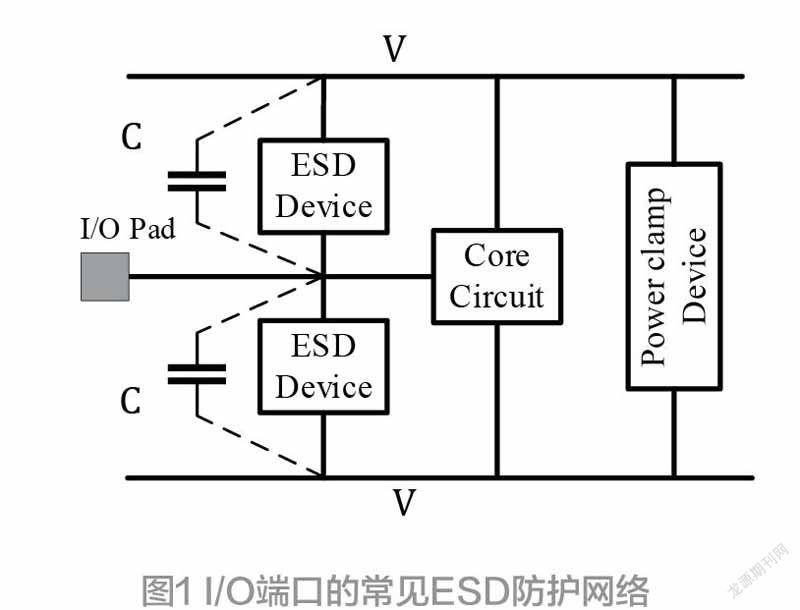

靜電釋放(electro-staticdischarge,ESD)是集成電路(IC)的主要可靠性問題之一[1],因此IC片上需放置靜電防護器件,其端口的常規靜電防護網絡如圖1所示。靜電防護器件的設計首先應滿足ESD窗口要求,此外,ESD防護器件的寄生電容(CESD)應盡可能小,避免器件寄生電容過大影響被保護電路的工作速度[2]。特別地,傳送高頻信號的IC端口對ESD器件電容更加敏感[3]。常規靜電防護器件有二極管、三極管、金屬氧化物場效應晶體管和可控硅整流器件(siliconcontrolledrectifier,SCR),其中SCR擁有最佳的單位面積靜電泄放能力,可為IC提供高水平的靜電防護[4]。為了保護信號電平高于和低于地的IC引腳,文獻[5][6]提出了雙向可控硅(dual-directionSCR,DDSCR)靜電防護器件,以滿足正向和反向ESD防護需求。在與內核電路集成時DDSCR器件外圍需增加保護環,以實現器件與電路隔離,對于防止少數載流子遷移對電路造成的干擾和損壞至關重要,并且也是防止閂鎖的常用方式[7]。本文的主要工作是分析討論保護環對DDSCR器件電容特性的影響,在高低壓工藝下分別制備了帶保護環和不帶保護環的DDSCR器件,測試并分析了器件寄生電容差異的根本原因。目前基本沒有文獻對DDSCR的電容模型開展研究,本文工作對于低容靜電保護器件設計具有一定的指導意義。

1低壓DDSCR器件結構

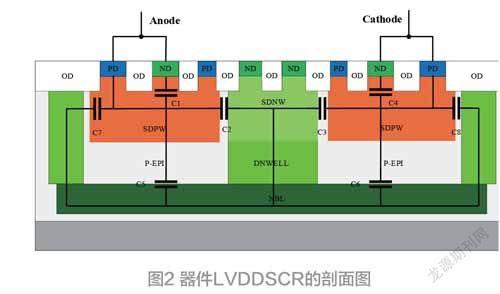

圖2為常規低壓DDSCR器件剖面圖,器件內部不同摻雜類型層次之間的結電容以及它們的拓撲連接關系一并展示于圖中。LVDDSCR器件使用的層次有N注入(ND)、P注入(PD)、P阱(SDPW)、N阱(SDNW)、深N阱(DNWELL)、P外延層(P-EPI)和N型埋層(NBL)。器件采用指狀版圖畫法,為216μm×89μm和232μm×105μm,使用0.18-μmBCD工藝制造。

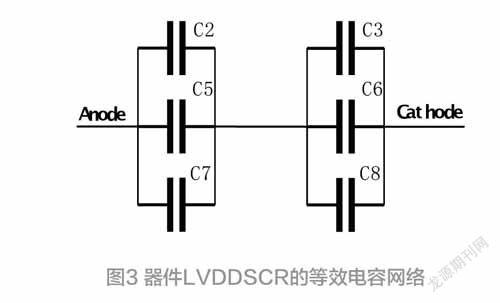

LVDDSCR器件的等效電容包括C1-C8,其中ND與SDPW之間形成的結電容為C1和C4;器件中間用來隔離的復合層次SDNW/DNWELL與P-EPI之間形成的結電容為C2和C3;P-EPI與NBL之間形成的結電容為C5和C6;左右兩側的隔離DNWELL與P-EPI之間的結電容為C7和C8。根據器件的剖面圖分析,得到LVDDSCR器件的等效電容網絡如圖3所示,結電容C1和C4短路,不參與電容網絡搭建。

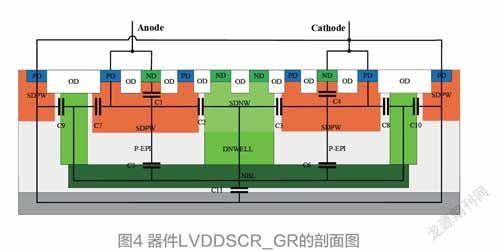

圖4為LVDDSCR_GR器件剖面圖,LVDDSCR_GR在LVDDSCR的外周增加了一圈P型保護環,該保護環由P+注入以及包裹它的P阱(SDPW)構成。

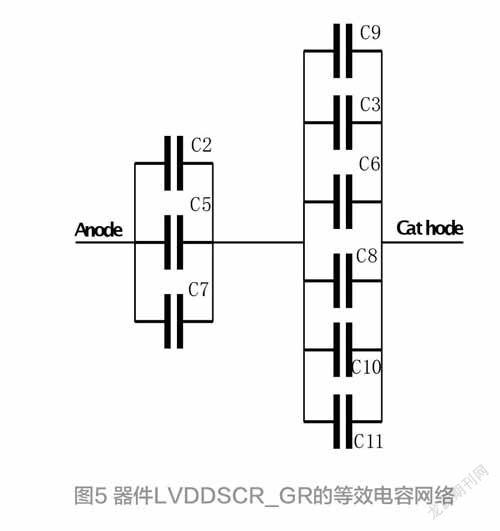

保護環的加入,使得器件增加了DNWELL與P-EPI之間的結電容C9、C10,以及P-EPI與NBL間的結電容C11,因此,器件LVDDSCR_GR的等效電容網絡變為圖5所示。與Anode連接的結電容沒有變化,但是結電容C9、C10、C11的加入使得連接到Cathode的電容值增大,因而使得整個器件寄生電容增大。

2低壓DDSCR器件測試與分析

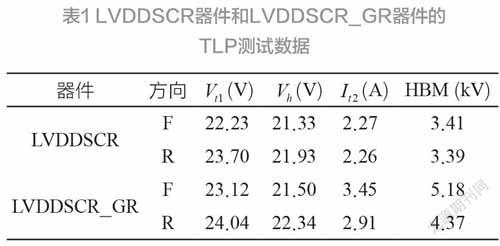

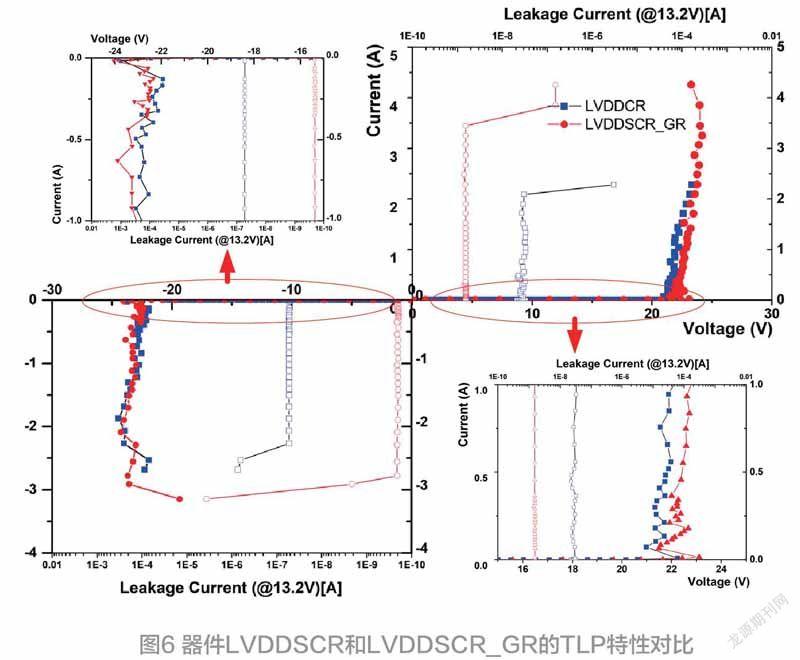

傳輸線脈沖(TLP)測試系統可獲得準靜態的I-V特性曲線,是表征器件靜電性能的重要手段之一。該測試系統提供的脈沖信號為10ns上升時間和100ns脈沖寬度,可得到等效的HBM靜電防護等級。LVDDSCR和LVDDSCR_GR器件的TLP測試結果如圖6所示,器件的關鍵靜電性能參數列于表1。

器件的TLP測試結果表明,不帶P型保護環的器件LVDDSCR與帶保護環的器件LVDDSCR_GR相比,觸發電壓和維持電壓基本相同。它們的正向觸發電壓Vt1分別為22.23V和23.12V,反向觸發電壓分別為23.7V和24.04V,維持電壓Vh都在22V左右。這說明二者的ESD電流主要泄放路徑一致,仍位于器件內部。保護環的增加使得器件內部的熱量分布有所改進,因此LVDDSCR_GR器件的失效電流相比LVDDSCR有所提升。該器件的失效電流(It2)略有不對稱,這是由于版圖布局采用指狀,不是完全對稱的布局,因此器件的正反會存在略微的不對稱現象。

Keysight公司的B1505A功率器件分析儀可測試器件C-V特性。采用該設備測試獲得的LVDDSCR、LVDDSCR_GR器件在1MHz和5MHz頻率下的C-V特性曲線如圖7所示。隨著電壓的增加,器件的寄生電容呈下降趨勢,同一個器件在5MHz頻率下的電容值高于1MHz頻率下的電容值。器件LVDDSCR在增加了保護環后,在1MHz的頻率下測試發現,LVDDSCR與LVDDSCR_GR器件的寄生電容有較大差別。在零偏壓條件下,1MHz的頻率下電容值由原來的1135fF增加到1463fF,5MHz的頻率下電容值由原來的1237fF增加到1658fF。

為了評定ESD器件的寄生電容和泄放靜電能力,引入品質因子(featureofmerit,FOM)來表征ESD器件的綜合性能:

式中VHBM為ESD器件能夠承受的HBM電壓,CESD為器件寄生電容,A為器件面積。

通過計算得到在1MHz下LVDDSCR與LVDDSCR_GR的正向FOM值分別為15.6和15.5,反向FOM值分別為14.5和12.2,說明LVDDSCR器件綜合能力最佳。

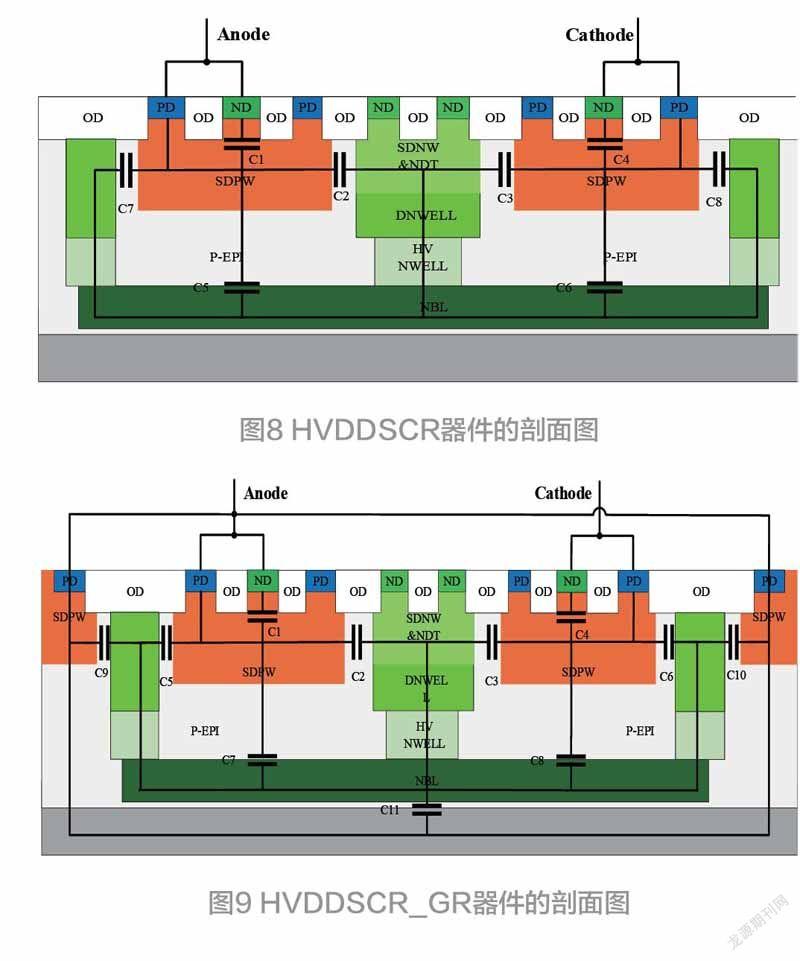

3高壓DDSCR器件結構

高壓工藝下雙向可控硅帶保護環和不帶保護環的靜電保護器件剖面圖分別如圖8和9所示。HVDDSCR與LVDDSCR器件結構相似,但是由于工藝發生變化,額外增加了高壓N阱(HVNWELL)層次,同時為了調節器件的觸發電壓,觸發面增加了NDT層次,SDPW與SDNW之間的距離也增加。兩個高壓器件的寄生電容網絡與LVDDSCR和LVDDSCR_GR器件相同,已在剖面圖上標識,因此不再單獨作圖。器件HVDDSCR和HVDDSCR_GR均為多指結構,采用指狀版圖畫法,為221μm×95μm和237μm×111μm,使用0.18-μmBCD工藝制造。

4高壓DDSCR器件測試與分析

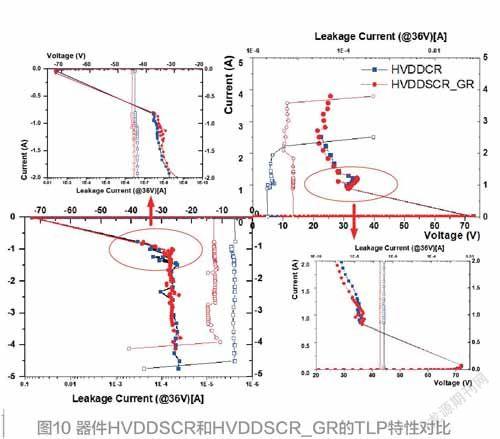

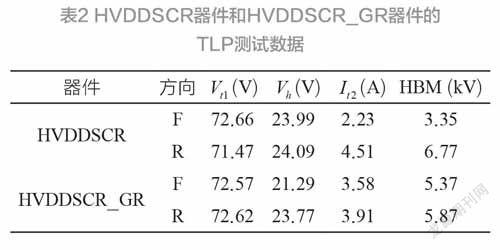

利用TLP系統測試得到HVDDSCR和HVDDSCR_GR器件的ESD特性。在高壓工藝下,由于ESD設計窗口的不同,器件的部分尺寸與層次進行了調整,因此器件的ESD特性相應發生了變化。

器件HVDDSCR和HVDDSCR_GR的觸發電壓都在72V左右,HVDDSCR的維持電壓比HVDDSCR_GR的稍高一些,但都在23V左右。器件HVDDSCR的正反向失效電流分別為2.23A和4.51A,器件HVDDSCR_GR的正反向失效電流都在3.5A以上,綜合來看器件HVDDSCR_GR的魯棒性更強。同樣,高壓器件版圖布局也采用指狀畫法,亦存在正反向失效電流不對稱現象。

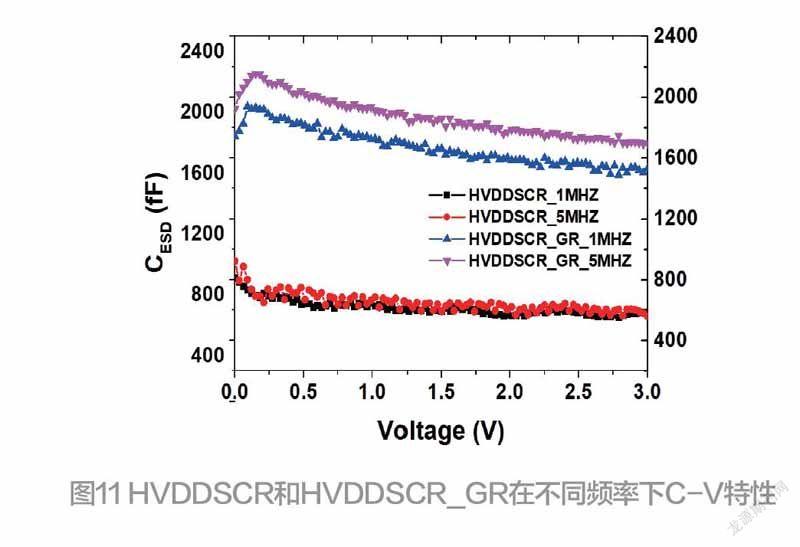

電容測試結果如圖11所示,高壓工藝下不帶保護環的DDSCR器件等效電容在1000fF以下。在1MHz頻率下零偏壓時HVDDSCR的寄生電容為810fF,HVDDSCR_GR電容為1740fF。在5MHz頻率下HVDDSCR_GR的電容值由HVDDSCR的922fF增加到1922fF。通過計算得到在1MHz下HVDDSCR與HVDDSCR_GR的正向FOM值分別為19.7和10.6,反向FOM值分別為39.8和11.7,驗證了HVDDSCR_GR器件的綜合能力最佳,與低壓工藝分析一致。

5結語

論文分別在高低壓工藝下制備了帶保護環和不帶保護環的DDSCR器件,TLP測試結果表明,P型保護環對器件的觸發點、維持點以及魯棒性影響不大,并未帶來較大變化,原因是DDSCR器件泄放電流的主要路徑存在于器件內部,P型保護環不會影響器件的泄放靜電能力。而C-V測試結果發現,P型保護環會引入新的結電容,使得DDSCR器件的寄生電容網絡發生變化,從而增大DDSCR器件的寄生電容。