以太網與CAN總線通信的FPGA設計與實現*

潘忠英

(山西工程職業學院,計算機工程系,山西 太原 030009)

0 引言

工業智能化推進過程中,在采集不同設備的數據進行傳輸時,為了提高傳輸速率、降低功耗,需選定合適的總線進行信息交互。不同的總線進行信息交互時,由于數據傳輸格式存在較大的差異,無法直接通訊,因此需要對傳輸數據進行格式轉化。綜控機與其他設備互聯時,一般采用計算機上特定有限的接口作為通訊方式,CAN 口通訊簡單、糾錯力度大、抗干擾能力強。當設備連接復雜度程度較高時,綜控機需要擴展性更高的接口來實現通訊。以太網傳輸速率快,能夠解決通訊節點增加導致的速率及功耗問題。目前對于CAN總線與以太網之間的通訊設計,一般采用ARM 芯片作為CPU 進行軟件設計。但考慮到FPGA 芯片具有開發周期短,編程靈活且成本低的特點,系統選用FPGA芯片作為時序控制核心,實現各個總線的底層協議以及不同協議之間的數據轉換交互。

1 系統總體設計

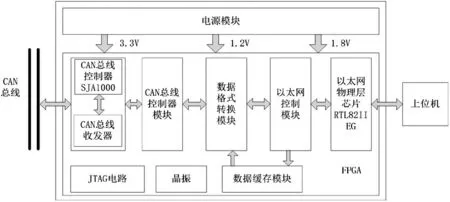

以太網與CAN 總線信息交互的總體設計框圖如圖1所示。

圖1 系統總體設計框圖

系統采用復旦微電子生產的國產FPGA 芯片作為邏輯控制核心,型號為FMK50。軟件設計由以太網收發模塊、CAN 收發模塊、數據轉換模塊等構成。系統上電后,由綜控機通過網口發送數據包給FPGA,FPGA 通過以太網控制模塊不斷查詢線上是否有新的數據,為匹配數據傳輸速率,采用緩存模塊對接收到的以太網數據報文進行暫存。FPGA 采用數據轉換模塊對UDP 報文進行數據提取,并按照CAN 總線通訊協議對數據重新進行打包封裝,發送給CAN控制器模塊實現數據的發送。為驗證設計的正確性,對數據的雙向傳輸均進行測試。通過比較發送端與接收端的數據及數據長度,表明數據雙向傳輸均正確。

2 系統硬件設計

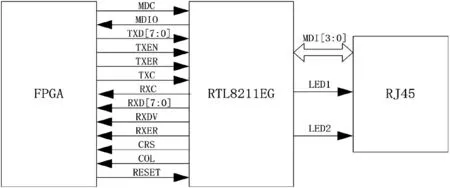

2.1 以太網模塊設計

系統采用以太網物理層芯片RTL8211EG 進行網口數據的收發,該芯片傳輸數據的速率最快可達到1000Mb/s。FPGA 與該芯片在硬件上通過專用接口GMII 進行連接,具體硬件電路圖如圖2 所示。從圖2中可以看出,當FPGA 發送數據給RTL8211EG 芯片時,FPGA作為主設備,依照時序手冊提供數據TXD和時鐘GTXC給從設備RTL8211EG。軟件設計上FPGA主頻為50MHz,通過時鐘管理模塊DCM 倍頻出125MHz 作為GTXC,數據傳輸時按照時鐘節拍對數據字節進行采樣。

圖2 以太網模塊電路圖

2.2 CAN模塊電路設計

系統采用CAN 控制器SJA1000,配合獨立CAN收發器實現CAN總線通訊。FPGA輸入8MHz的時鐘到CAN控制器芯片的XTAL引腳,與內部振蕩電路相連。由于CAN 總線由差分電平CANH 和CANL 組成,CAN 控制器輸出的數據不能直接與之通信,因此需要CAN 收發器來對數據進行電平轉換,實現數據正常穩定的傳輸。由于FPGA 與CAN 控制器芯片的工作電壓不同,兩者在進行通訊時需要進行電壓的匹配。CAN 模塊電路設計圖如圖3所示,圖中CAN 控制器芯片的RX1 引腳與CAN 收發器的Vref 引腳互連,降低數據在CAN控制器與CAN收發器之間的傳輸延時。

圖3 CAN模塊電路圖

3 系統軟件設計

軟件方案設計上以國產FPGA 芯片FMK50 作為控制芯片,并在開發環境Vivado 和Procise 中對軟件進一步開發。

3.1 CAN模塊軟件設計

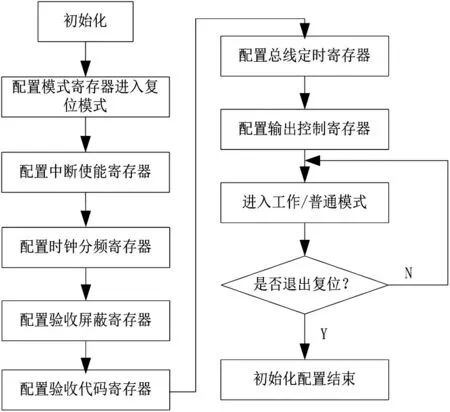

3.1.1 CAN初始化模塊設計

FPGA 與CAN 控制器進行信息交互前,需要對其芯片內部的相關寄存器進行配置,由于FPGA 對CAN控制器的配置只能在復位模式下進行,因此系統上電后,軟件設計上自動運行CAN 初始化模塊,完成對CAN 控制器的寄存器配置后退出復位模式,進入正常工作模式后即可執行讀寫操作。該模塊初始化流程如圖4所示。

圖4 CAN模塊初始化流程

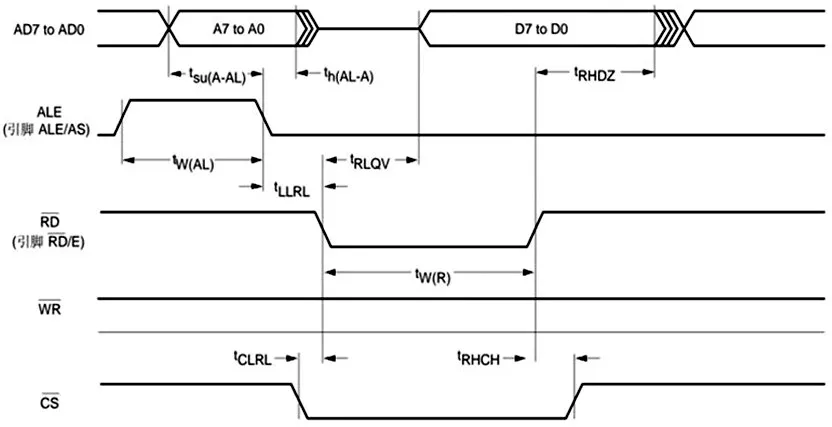

3.1.2 CAN接收模塊設計

CAN 模塊上電完成初始化后,可根據外部中斷標志的沿觸發的方式來讀取CAN 控制器存中緩器內的數據。FPAG 主要通過8 路數據/地址線AD0-AD7、地址使能線ALE、片選信號/CS、讀使能信號/RD、寫使能信號/WR 來讀取CAN 控制器中接收緩沖器內的13 個字節數據,FPGA讀周期時序圖如圖5所示。

圖5 讀周期時序圖

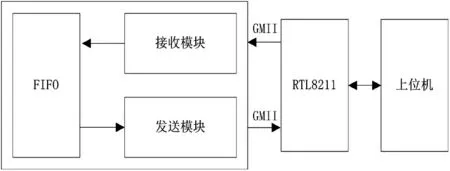

3.2 以太網模塊軟件設計

上位機通過網口發送數據至物理層芯片RTL8211,FPGA 內的以太網控制模塊通過GMII 總線和該芯片進行信息交互,信息傳輸格式遵循UDP 協議,具體通信圖如圖6 所示。以太網模塊主要由四部分結構組成,包括負責讀取物理層芯片內接收FIFO中數據的接收單元、發送數據至物理層芯片發送FIFO 的發送單元、為匹配數據傳輸速率而進行數據緩存的緩存單元以及對報文中的數據進行校驗的CRC校驗單元。

圖6 以太網模塊和上位機通信圖

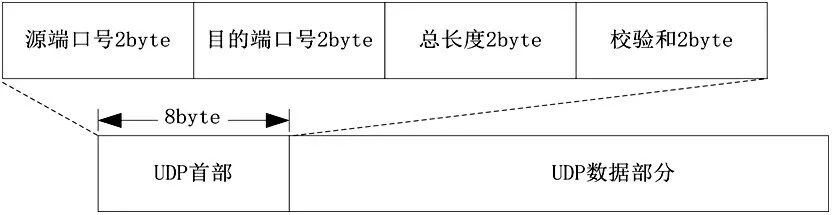

3.3 UDP數據傳輸協議

UDP 協議作為網口通訊最常用的協議之一,建立通訊方式簡單、傳輸過程可靠。UDP 發送的數據報中包含通訊雙方的端口號,因此數據傳輸在總線上可依據指定MAC 地址實現正確接收與發送。同時該協議包含CRC 校驗,若傳輸過程中數據受其他因素影響發生錯誤,通過CRC 模塊驗證,錯誤信息可被檢測出并丟棄該包數據。UDP 數據包共分為兩部分,為數據包頭部和數據。其中,數據包頭部分由通訊雙方MAC地址、數據報長度以及校驗和構成。UDP 報文的主要部分如圖7所示。

圖7 UDP報文構成

4 系統測試與驗證

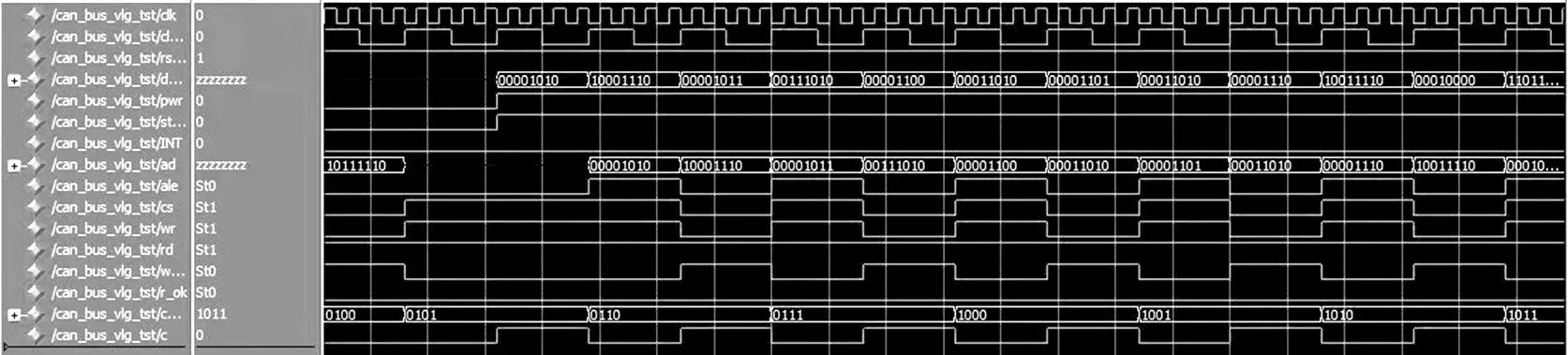

4.1 CAN模塊仿真

CAN 控制器SJA1000 與FPGA 通過8 通道并行數據/地址線AD0-AD7 進行交互,當地址使能信號ALS有效時,總線上輸出的數據表示地址;當寫使能線/WR的電平為低時,總線上的信息為數據。為驗證CAN模塊軟件設計的正確性,編寫測試模塊,對收發模塊中的邏輯設計進行相應的仿真測試。當CAN 接收模塊檢測到外部中斷信號的下降沿時,按照讀時序讀取SJA1000 中的接收緩沖器的13 個字節,接收完后需要釋放接收緩沖器以臨時清除中斷位,否則將不會響應后續中斷信號。接收模塊的軟件仿真如圖8所示。

圖8 CAN模塊數據接收仿真測試圖

4.2 以太網通信測試

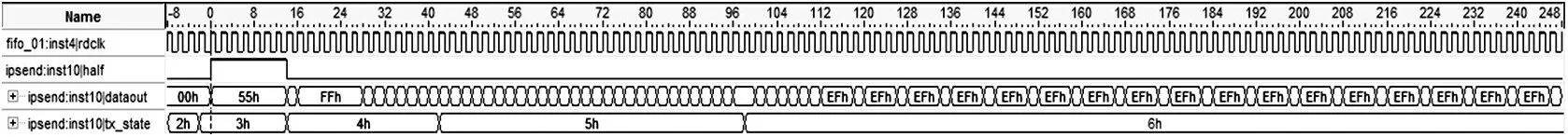

為驗證以太網模塊的正確通信,采用chipscope 對以太網模塊數據傳輸進行在線監測,如圖9所示,以太網發送模塊對輸出數據進行封裝,發送數據時首先發送7 個字節的前導碼0x55 以及1個字節的幀開始符0xD5、然后6 字節目的MAC 地址28-D2-44-DC-6E-FE、6 個字節源MAC 地址00-0A-35-01-FE-C0以及2字節IP包類型,然后發送數據報及校驗和。

圖9 chipscope監測圖

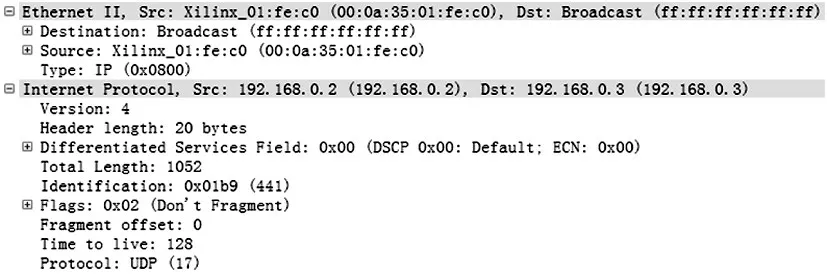

上位機利用網口數據抓取工具Wireshark 對線上數據進行實時監測,通過該方法可驗證上位機與設備通訊連接正確,且通過觀察數據驗證收發地址及收發個數均正確。從圖10 中可以看出,Wireshark 識別到源MAC地址為00-0a-35-01-fe-c0。

圖10 網口監測圖

4.3 CAN模塊數據與以太網數據通信測試

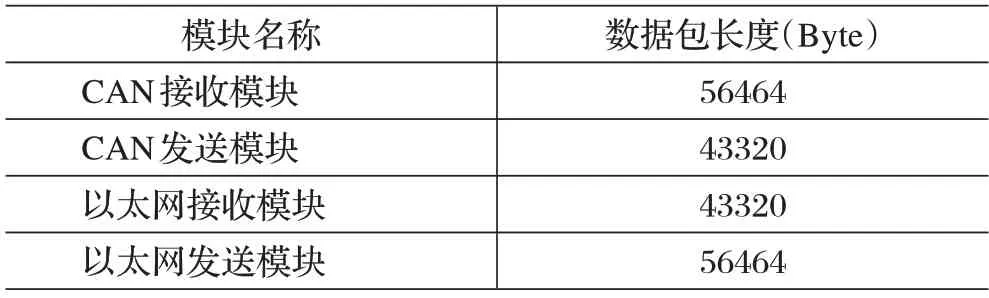

為驗證CAN 模塊與以太網模塊之間的正確通信,通過雙向發送不同字節長度的數據,上位機完成數據的存儲,通過對比數據長度來作為本次測試的依據。軟件設計中CAN 總線傳輸速率為800Kbps,當以太網傳輸波特率設置為10Mbps 時,CAN 總線上的數據總能被以太網收到并發送。為匹配兩模塊的傳輸速率,不出現丟包的現象,以太網發送數據頻率同樣采用800Kbps 進行數據通信。如表1 所示,分別為CAN 模塊收發的數據長度以及以太網模塊收發的數據長度對比,由表可知兩模塊之間可以實現正確通信。

表1 CAN模塊收發的數據長度以及以太網模塊收發的數據長度對比

5 結束語

系統利用FPGA 強大的可編程能力,通過對CAN總線以及UDP 數據格式的拆解、提取、封裝實現CAN總線與以太網之間的通信。由于兩類總線應用領域的不同,且數據傳輸速率存在較大差距,為實現兩者之間的正確通信,需對數據傳輸速率進行匹配。通過實際測試,降低以太網數據傳輸頻率可達到正常通信,且不發生丟包現象。采用FPGA 芯片使得產品開發周期縮短,并能高效的實現總線間通信。系統滿足設計需求,對不同總線間通信具有一定參考意義。