片上SRAM 物理不可克隆函數(shù)特性優(yōu)化設(shè)計

高國平,趙維林

(中國電子科技集團公司第五十八研究所,江蘇無錫 214072)

1 引言

安全性對于幾乎所有電子產(chǎn)品來說都是非常重要的,物理不可克隆函數(shù)(PUF)的提出為保護芯片數(shù)據(jù)安全提供了一種切實有效的方法。以靜態(tài)隨機存儲器(SRAM)PUF 為代表的基于存儲器的PUF 設(shè)計具有很大的優(yōu)勢,在核心集成電路中,存儲器是必須具備的單元,其實現(xiàn)簡單,現(xiàn)已成為PUF 主流設(shè)計方向。

在實際應(yīng)用過程中,嵌入SRAM 集成電路產(chǎn)生的隨機數(shù)特性大不相同。通常的方法是尋找具有產(chǎn)生較好隨機數(shù)特性的集成電路[1-3],然而隨著工藝節(jié)點的進步,這種方法顯露出了較大的局限性[4]。為了便于獲得具有SRAM PUF 的集成電路,本文提出了一種設(shè)計優(yōu)化方法。

2 原理分析

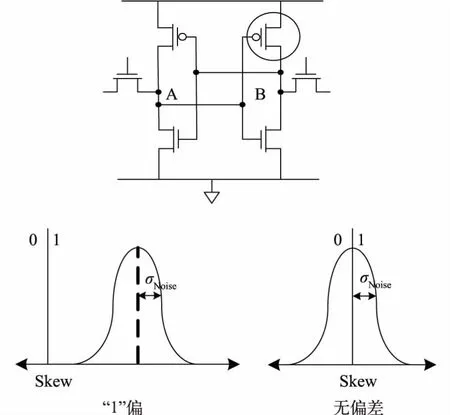

SRAM 單元及工藝噪聲影響如圖1 所示,每一位存儲單元通常包含6 個MOS 管,由2 個交叉連接的反相器和2 個讀寫開關(guān)管構(gòu)成。讀寫SRAM 存儲單元時,控制使能字線,使開關(guān)管導(dǎo)通,此時,可以通過位線對SRAM 單元進行讀寫。當(dāng)SRAM 斷電時,由于SRAM 沒有電荷存儲,所以SRAM 存儲單元瞬間無電荷,AB 狀態(tài)為“00”。由于反向器為非穩(wěn)定狀態(tài),上電時,其中一個反相器必須翻轉(zhuǎn)一次,AB 狀態(tài)變?yōu)椤?1”或“10”。理想狀態(tài)下,AB 的“01”或“10”狀態(tài)完全是隨機的,即無偏差單元。然而事實上,由于制造過程中的不可控因素,單個SRAM 存儲單元傾向“0”或者“1”,形成“0”偏(0-skewed)或“1”偏(1-skewed)存儲單元。

圖1 SRAM 單元及工藝噪聲影響

靜態(tài)噪聲容限(SNM)σNoise是描述SRAM 單元噪聲容限的指標(biāo)。單元的SNM 是給定電源電壓的最大噪聲電壓[5]。對于外界噪聲的影響,存儲單元對稱結(jié)構(gòu)匹配越好,外界噪聲的影響作用就會越大,甚至?xí)斐纱鎯ζ髌蛳喾捶较颉!?br>