一種基于重構的FPGA遠程更新方法

周 駿,宋 凱,沈 洋,丁 遜

(中國船舶集團有限公司第八研究院,南京 211153)

0 引 言

近年來FPGA遠程更新多采用ARM、CPLD等微處理器輔助方式實現[1-4],上位機通過網絡通信接口將新程序發送給微處理器,并由微處理器寫入非易失性存儲器中。FPGA配置的加載由微處理器通過I/O口模擬FPGA配置信號時序,將新程序加載到FPGA中,完成更新。在雷達應用中,FPGA承擔復雜的信號處理算法,需要大量邏輯實現,將遠程更新邏輯與用戶業務邏輯耦合在一起會大量占用業務可使用的邏輯資源。本文提出一種基于重構的FPGA遠程更新方法,將Flash芯片分成遠程更新程序區域和用戶業務邏輯區域,通過ICAP原語與IPROG命令實現遠程更新程序和用戶業務邏輯的跳轉加載。在遠程更新程序中完成Flash用戶業務邏輯區域配置文件的更新與維護,在完成更新后,跳轉至用戶業務邏輯,實現不斷電遠程更新程序的目的。

1 工作原理

基于重構的FPGA遠程更新功能依靠網絡通信功能和FPGA的MultiBoot能力[5],其中MultiBoot功能是指FPGA在不斷電的情況下,可以重新加載Flash中不同地址的配置文件,實現FPGA整片邏輯重構。將Flash按照最大配置文件大小分成用戶業務邏輯區域和遠程更新邏輯區域兩個區域:前者存儲用戶業務程序,后者存儲遠程更新程序。所有配置程序均包含重構模塊,重構模塊通過將配置區域Flash地址寫入ICAP原語并發送IPROG命令的方法,實現FPGA整片邏輯重構。

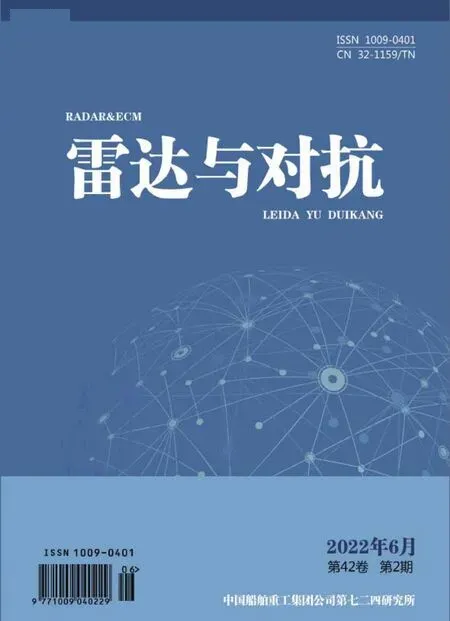

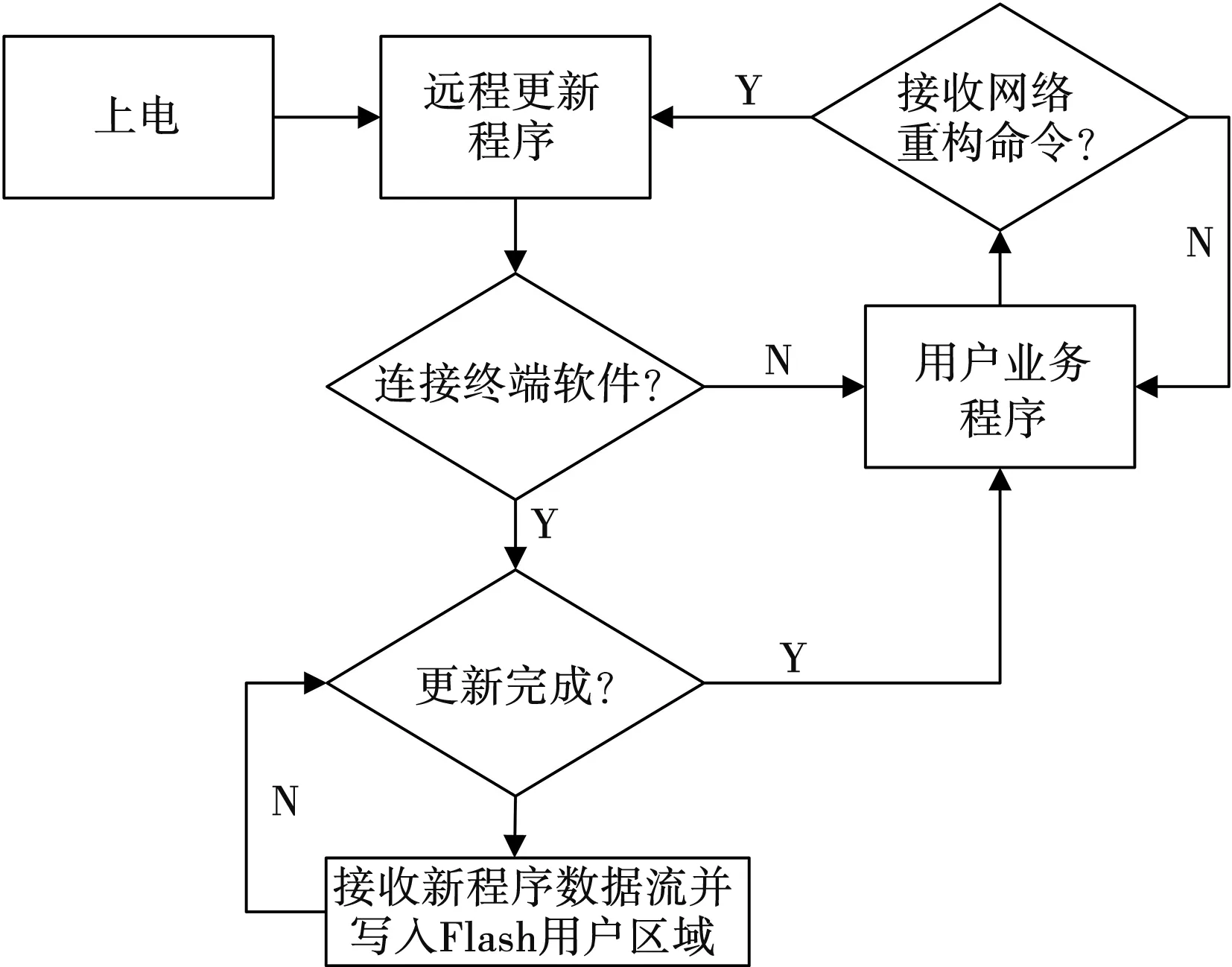

遠程更新程序邏輯由重構模塊、MicroBlaze系統以及運行于Microblaze系統上的嵌入式程序構成,可采用TCP/IP協議接收上位機傳輸的FPGA新配置,并寫入Flash用戶業務邏輯區域,實現配置文件的遠程更新,完成后再重構加載用戶業務程序即可。由圖1所示的工作原理可以看出,FPGA通過網絡接口模塊和一個簡單的狀態機以及ICAP原語完成用戶業務程序和遠程更新程序的切換,由于兩個配置邏輯文件完全獨立,可以使產品具備遠程更新功能的同時不占用用戶業務邏輯資源。

圖1 遠程更新工作原理框圖

2 設計實現

2.1 硬件架構

2.1.1 硬件設計

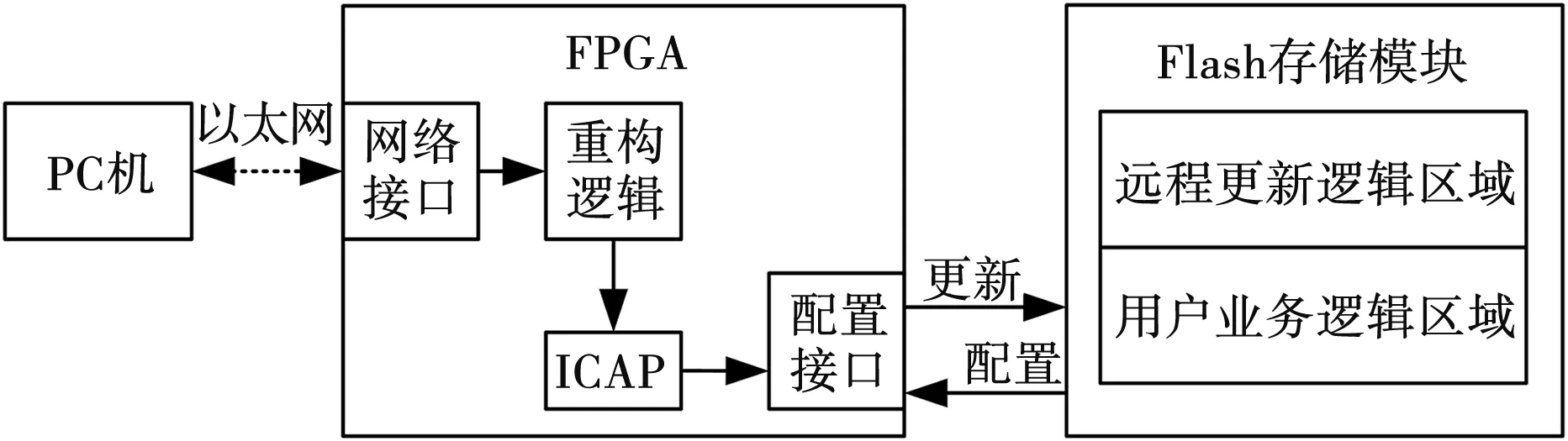

為了滿足低成本、小型化需求,系統硬件采用單片FPGA處理模塊、Flash芯片、網絡芯片構成,其硬件框如圖2所示。FPGA選用Xilinx公司的Virtex 6芯片,該芯片有充足的邏輯資源、DSP資源和RAM資源,滿足導航雷達復雜信號處理的需求,同時該芯片內置專用加載模塊,支持MultiBoot功能。網絡接口芯片采用88E1111,Flash選擇Mircon公司的JS28F512P30,存儲64 MB,滿足存儲兩個bin文件的需求。在本系統中,遠程更新邏輯與用戶業務邏輯共用相同網絡通信鏈路,避免了網絡交換芯片的使用。

圖2 遠程更新硬件框圖

2.1.2 嵌入式軟核設計

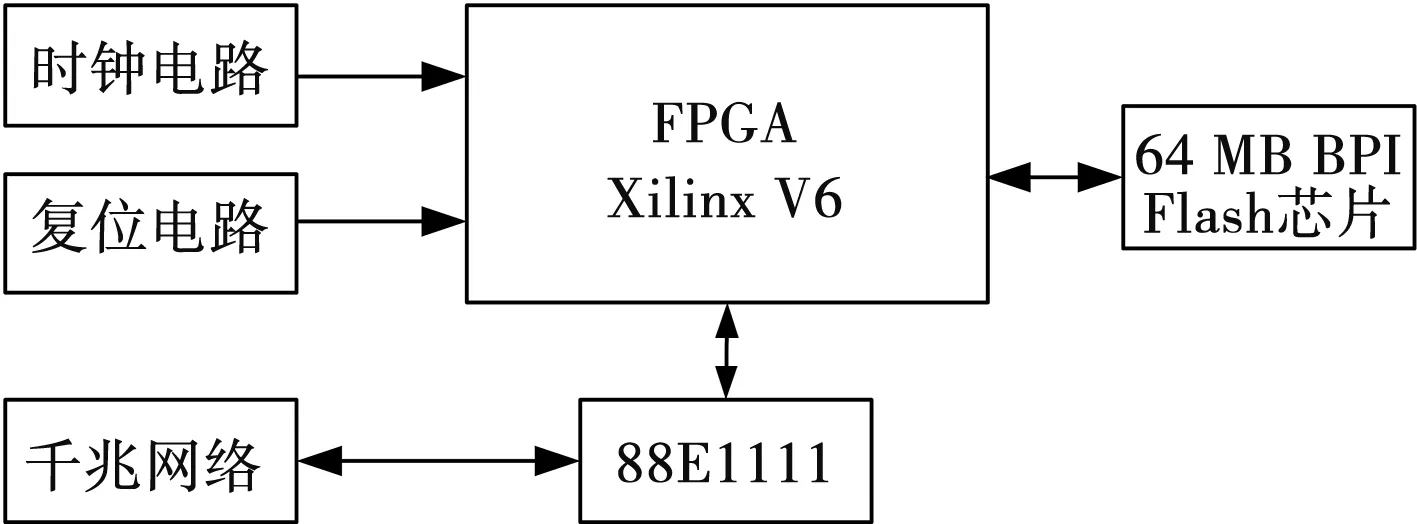

遠程更新邏輯需要實現網絡協議通信及Flash芯片控制,系統采用構建MicroBlaze嵌入式軟核來替代傳統方法中的ARM芯片。MicroBlaze系統設計如圖3所示,外設方面包括網絡接口模塊、Flash控制模塊、定時模塊、調試模塊、中斷管理模塊、存儲模塊等,其中由于本系統無DDR3芯片,為了給嵌入式程序提供足夠的運行空間,通過AXI總線將一個片內BlockRAM模塊連接到MicroBlaze的M_AXI_DC和M_AXI_IC端口充當緩存。

圖3 遠程更新MicroBlaze系統框圖

2.2 軟件設計

2.2.1 重構模塊

用戶業務邏輯和遠程更新邏輯均有重構模塊,該模塊利用FPGA的Multiboot功能可以不斷電加載Flash中不同區域FPGA配置文件,完成整片FPGA重構。當收到重構跳轉命令后,重構模塊狀態機向ICAP原語寫入內部加載邏輯指令序列,將重構區域Flash地址填入加載起始地址寄存器(WBSTAR)中,并寫入IPROG控制指令完成重構加載。

重構跳轉邏輯如圖4所示。設備上電時,FPGA默認加載遠程更新程序,如果在一定時間內無法連接上位機,則跳轉至用戶業務程序,否則等待上位機操作;當FPGA跳轉至用戶業務程序后,如果接收網絡重構命令,通過重構模塊將遠程更新邏輯區域的Flash地址寫入ICAP原語,并發送IPROG命令,FPGA將從遠程更新邏輯區域地址開始加載遠程更新邏輯,實現FPGA由用戶業務邏輯向遠程更新邏輯的重構。當FPGA重構為遠程更新邏輯時,通過TCP/IP協議連接上位機服務器,接收由上位機發送的新用戶業務邏輯bin文件數據流,寫入用戶業務邏輯區域,實現遠程更新功能。當完成更新時,遠程更新邏輯將再次利用ICAP原語,使FPGA從用戶業務區域加載更新后的程序,完成不斷電用戶業務程序更新。

圖4 重構模塊原理流程圖

2.2.2 嵌入式內核程序設計

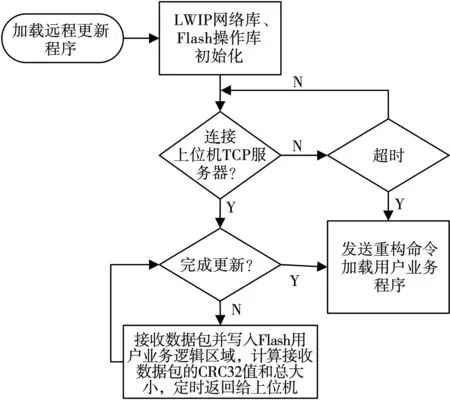

嵌入式內核程序運行于FPGA構建的MicroBlaze嵌入式軟核內,其設計基于FreeRTOS操作系統,并運行LWIP網絡協議棧,實現TCP/IP通信。嵌入式內核程序流程如圖5所示:首先完成Flash操作庫和LWIP網絡庫初始化,然后連接指定IP的TCP服務器。如果在一定時間內無法連接,則對重構模塊發送命令跳轉至用戶業務模塊。如果連接成功,將等待上位機操作。當需要更新程序時,上位機軟件通過TCP協議發送新的用戶業務程序數據包給嵌入式內核程序,嵌入式內核程序接收數據包,并寫入Flash中的用戶業務邏輯區域,將接收到的數據包CRC32校驗值和寫入的Flash數據包總大小返回給上位機程序。當上位機完成新程序文件發送,并接收到正確的CRC32校驗值和數據包大小時,認為更新完成,發送重構命令給嵌入式內核程序,實現新用戶業務程序的加載。

2.2.3 上位機程序設計

上位機采用MFC設計,通過TCP/IP協議與嵌入式內核程序進行通信,主要完成創建更新TCP服務端,UDP重構命令發送,用戶文件讀取等功能。當FPGA重構為遠程更新邏輯時,嵌入式內核程序將主動連接上位機的TCP服務端。在嵌入式內核程序連接服務器成功后,上位機讀取本地用戶更新文件,并發送給嵌入式內核程序實現更新。更新完成后,上位機發送UDP重構命令,實現FPGA由遠程更新邏輯跳轉至用戶業務邏輯;當FPGA重構為用戶業務邏輯時,上位機軟件發送UDP重構命令,FPGA收到命令后重構為遠程更新邏輯,并實現用戶業務邏輯更新。

圖5 嵌入式內核程序流程圖

2.2.4 更新失敗處理

本文方法將Flash區域劃分為用戶業務邏輯區域和遠程更新邏輯區域,其中后者起始地址為0,使FPGA上電默認啟動區域。當對用戶業務邏輯區域進行更新時,系統出現斷電、斷網等突發情況,導致用戶業務邏輯更新失敗,此時并沒有操作遠程更新邏輯區域的配置文件;當系統重新上電時,FPGA默認加載遠程更新邏輯,可以繼續實現對用戶業務邏輯的更新,可見采用遠程更新邏輯和用戶業務邏輯分離設計的方式有較高的可靠性。

3 試驗結果

為了驗證本文方法,以一型導航雷達信號處理板卡為硬件平臺,該平臺采用Xilinx V6芯片,編寫了遠程更新程序和雷達信號處理程序。由于系統的小型化,沒有采用DDR芯片,遠程更新程序使用FPGA芯片內部Block Ram作為MicroBlaze程序運存,消耗17 203個寄存器、17 316個查找表以及296個RAMB36E1,其中使用的存儲資源約占整個芯片存儲資源的27%,而用戶業務程序中使用的重構模塊僅使用了31個寄存器和70個查找表。可以看出,本文方法大大減少了遠程更新功能對用戶業務邏輯的占用。采用本文方法對15 MB大小的bin文件進行遠程更新僅需40 s,較采用JTAG下載線方式有明顯優勢。由于采用TCP協議傳輸文件流時,協議本身具備校驗和重發機制,因此本文方法可靠性較高,能為采用單片FPGA的小型化系統提供遠程更新功能。

4 結束語

本文基于重構的FPGA遠程更新方法利用FPGA的MultiBoot功能,實現遠程更新程序和用戶業務程序的分離式設計,減小遠程更新功能對資源的占用,不需要設計額外微處理芯片電路進行輔助,同時與用戶業務程序共用相同的網絡鏈路,利于設備小型化、低成本設計。目前該方法已應用于雷達產品,為其提供了穩定可靠的遠程更新功能。