一種基于CMOS工藝的低相噪壓控振蕩器的設計

齊賀飛,王磊,王鑫,王紹權,張夢月

(中國電子科技集團公司第十三研究所,河北 石家莊 050051)

0 引 言

壓控振蕩器作為通信系統中的本振信號源,其頻率范圍和相位噪聲等信號質量對通信系統的性能有重要影響,隨著集成電路工藝的發展,芯片的集成度不斷提高,片上系統(System on Chip, SoC)已經成為主流設計思路。SoC 的特點決定了需要集成電路工藝的兼容性,既要滿足微處理器(Micro Controller Unit, MCU)的Flash 存儲器的要求,又要滿足鎖相環電路需要厚金屬高Q 值電感和可變電容晶體管。傳統的III-V 族化合物集成電路工藝已經不能滿足集成度的要求。同時,隨著系統對于低功耗的要求越來越嚴苛,在片上系統SoC 中集成頻率源IP 也將逐漸替代原有的分立式頻率源電路,能夠在不影響系統性能的前提下,大幅度降低系統的面積和功耗。

本文設計了一種基于標準CMOS(Combined Metal Oxide Semiconductor, CMOS)工藝的VCO,可實現寬帶調諧范圍,從2.3 GHz ~3.3 GHz,具有寬電壓和寬溫度范圍。在2.97 V ~3.63 V 供電,-60 ~130 ℃均可穩定工作。采用了并聯的可調節電容,用于擴展VCO(Voltage Control Oscillator, VCO)的振蕩頻率范圍的同時也能保持很低的增益,從而提高了壓控振蕩器的噪聲性能。同時使用FLASH非易失性存儲器。FLASH IP 作為低成本化系統配置資源,通過通用的調試接口電路與外部通信,內部存儲了配置鎖相環所需要的控制字,對用戶使用極為方便。本芯片還可以與通用的MCU 或者FPGA 等進行工藝集成,進一步提升系統功能,提升批次一致性和可生產性,簡化外圍電路器件,降低用戶系統設計的總成本。

1 VCO 振蕩電路的相位噪聲來源

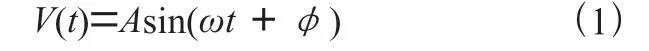

理想的LC 振蕩器輸出信號為:

其中是振蕩頻率,是振蕩幅度,是初始相位。由于和是固定值。因此理想振蕩信號的頻譜是在處的單根譜線。

實際的LC 振蕩器輸出信號為:

() 代表振幅的抖動情況,()代表相位抖動情況。是振蕩信號頻率,對于|()|<<1 我們有:

可見發現實際振蕩器的頻譜和理想的頻譜差別主要體現為頻譜的純凈度,如圖1所示。

圖1 理想振蕩器和實際振蕩器的頻譜特性圖

非理性特性在時域上體現為信號的各個周期時間不相同,在頻域上體現為頻譜的不純凈。且造成的非理想特性總體表現為VCO 的相位噪聲。

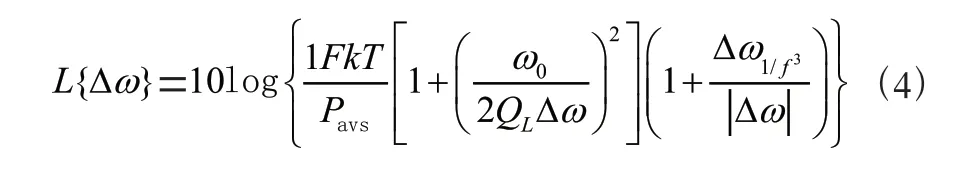

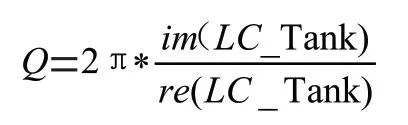

VCO 的相位噪聲模型主要有兩種。第一種模型是基于線性非時變系統建立的利森-卡特森模型

第二種模型是基于線性相位時變系統提出的吉米瑞-李模型。

基于上述模型,分析VCO 的相位噪聲來源,主要包括以下幾個方面:電流源、交叉耦合對管、可變電容管的噪聲、LC 回路熱噪聲。其中通過使用高Q 值的電感電容可以降低LC 回路的熱噪聲。可變電容的非線性會引入AM-to-FM 噪聲,通過將部分可變電容置換為電容開關陣列,可以減小可變電容的AM-to-FM 噪聲。增大輸出擺幅減小尾電流源噪聲。后面章節將從LC 諧振電路、陣列式可變電容、VCO 整體電路、自動選帶技術等幾個方面設計VCO 和降低相位噪聲。

2 LC 壓控振蕩器設計

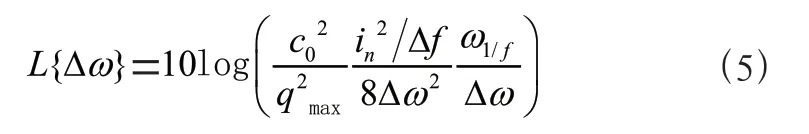

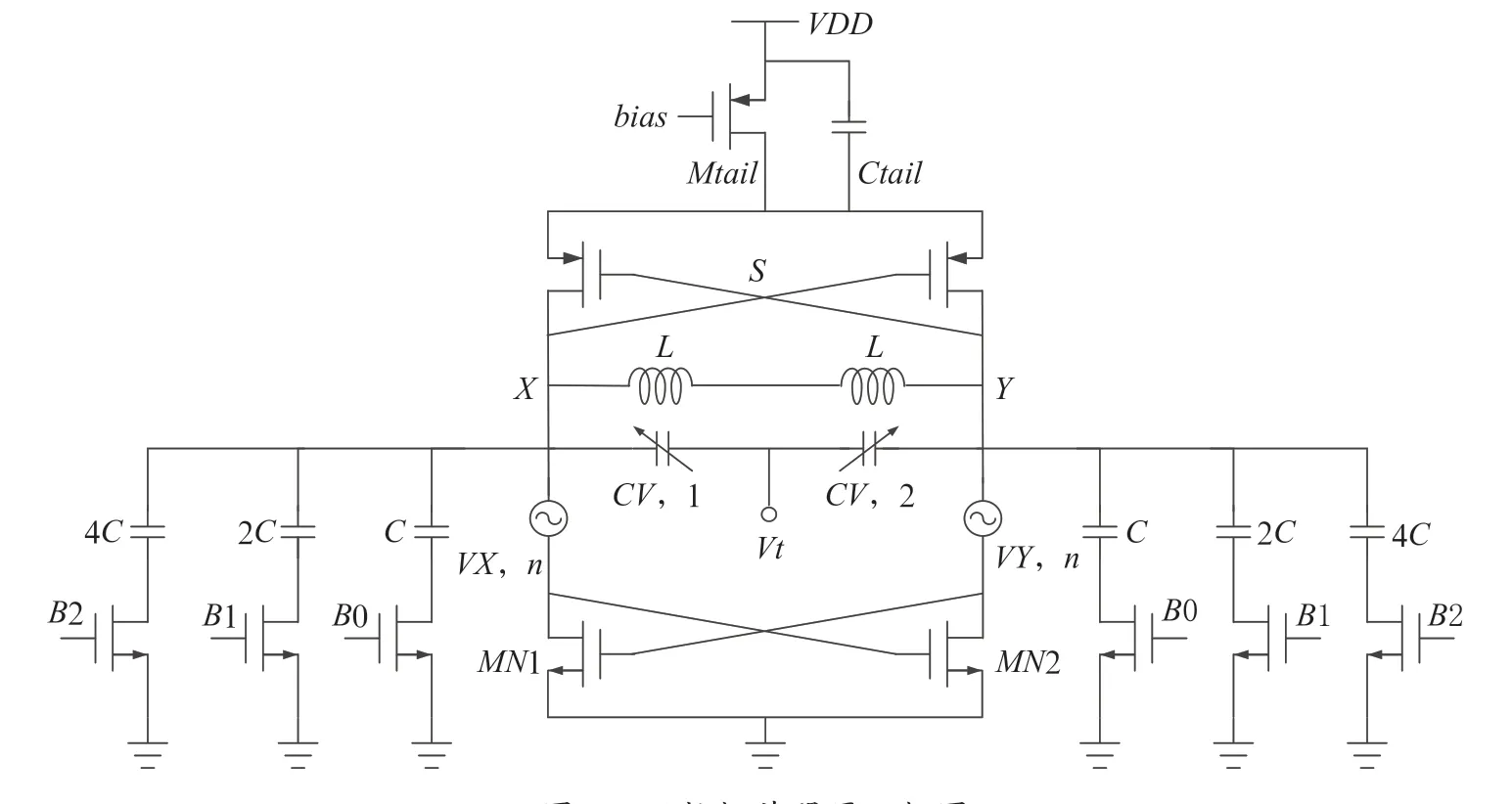

本文使用了如圖2結構的VCO,其相位噪聲主要來源為PMOS 和NMOS 的噪聲電流和非理想的L/C 電路。由于PMOS和NMOS的噪聲由工藝決定,且需要和其他工藝兼容,因此只能優化L/C 的品質因數Q 值和系統的參考電流值以降低相位噪聲。

圖2 VCO 的原理圖

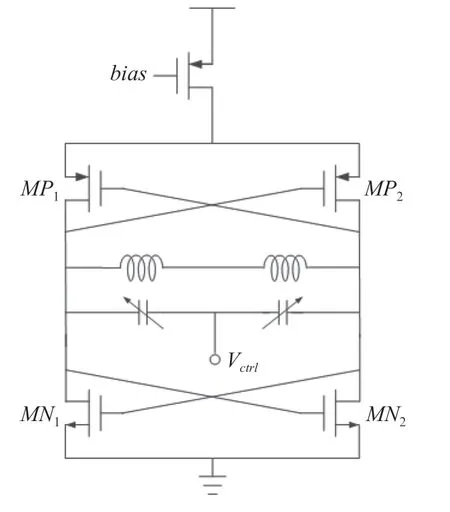

電感的值由如下公式決定:

_Tank 表示LC 振蕩腔體的系統阻抗,系統的虛部越大,實部越小,則值越高。

值越高,系統的噪聲性能越好,因此需要盡量提高值,提升方式可以選擇提高感值或降低的電阻。

對于所需要的諧振頻率,和的乘積范圍固定。如果需要提高感值則需要增加圈數,同時降低容值。在圈數固定的前提下,提高感值需要很大的版圖面積作為代價,受到工藝DR(Design Rule)設計規則的制約。

電容的值遠遠高于電感,因此降低電感的阻抗十分重要,選擇25 ~30 μm 厚度的金屬層作為電感的制造層,芯片中選擇將電感放在頂層,可以在盡量減少面積的前提下提高值。在設計規則允許的范圍內,最多可以設置4 圈的全差分電感。

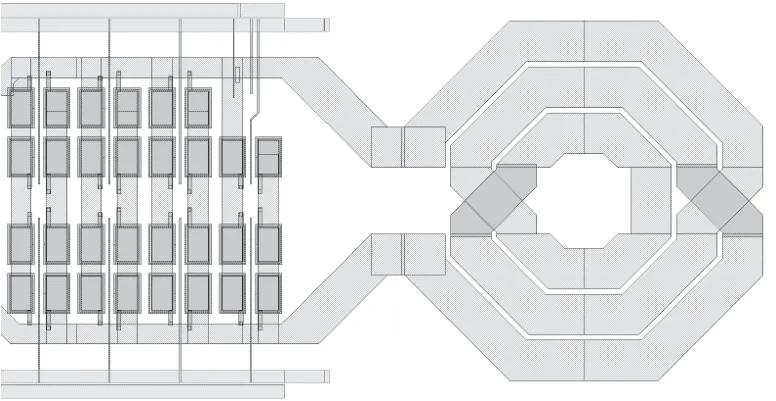

考慮到原理圖中的電感只有兩端引出,因此本文將2 個電感合并為一個電感,大幅降低了芯片面積。仿真結果:電感的感值為1 nH,阻值為0.8 歐姆。

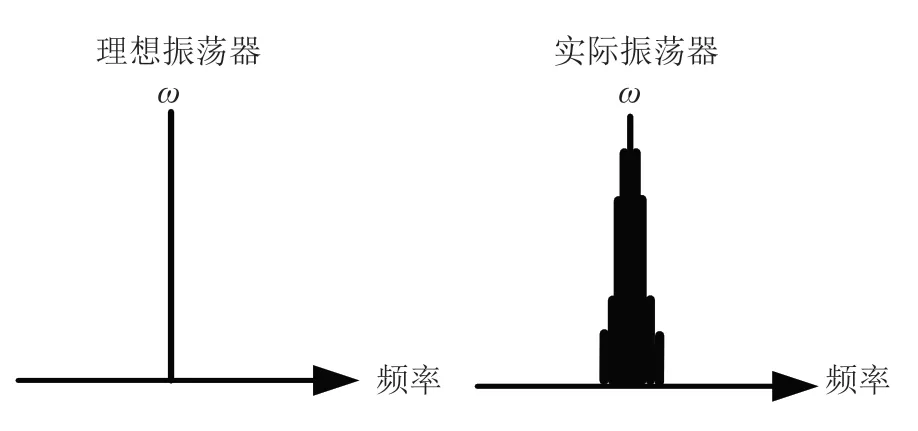

3 分段式可變電容設計

VCO 的振蕩頻率由/的值決定,改變/的值可以調整VCO 的振蕩周期。調諧可變電容器的容值范圍為16 ~32 pF,變化范圍為16 pF。設計的數控電容陣列應有50%的重復率,需要通過16 組數字碼覆蓋1 GHz 調諧范圍,則每組調諧碼硬覆蓋120 MHz 左右的頻率范圍,以便盡量選擇VT 值靠近中間的電容值從而提高系統的相位噪聲,因此數控電容的變化量應保持在8 pF。50%的VCO 頻帶重復降低了VCO的靈敏度,也可以優化VCO 相位噪聲。對電容進行二進制編碼,可以降低電容的數量,版圖布局時考慮了差分布局,因此電容數量分別為2、4、8、16。總電容數量為30 個。每對差分電容的容值均為8 pF。最終實現的電容陣列如圖4所示。每切換一組數字碼,調諧電壓不變時,頻率增加約60 MHz。

4 壓控振蕩器整體設計

VCO 的設計中,主要考慮了以下指標:

(1)靈敏度:VCO 的靈敏度與VCO 的相位噪聲成反相關關系,因此盡量降低VCO 的調諧靈敏度,本芯片設定為40 MHz/V。

(2)帶寬:VCO 的調諧頻率范圍決定了產品的應用范圍,是最高和最低頻率的差值,本芯片設定為1 000 MHz,單條頻帶帶寬為120 MHz。

(3)線性度:由于可變電容的非線性導致VCO 的調諧靈敏度并非常數,為提升芯片一致性,一般要求在整個調諧范圍內最KVCOmax 不大于KVCOmin 的2 倍。

(4)相噪:VCO 設計中最重要的指標要求,本芯片設定10 kHz 頻偏處,相位噪聲不高于-80 dBc/Hz@2.8 GHz。

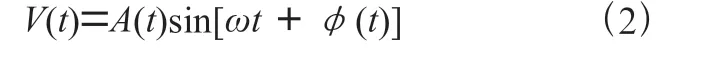

壓控振蕩器設計采用了高Q 的電容和電感作為LC 諧振回路,采用互補的NMOS 和互補的PMOS 作為負阻單元,采用開關電容陣列展寬帶寬降低VCO 靈敏度,其相位噪聲指標優勢明顯,采用了差分電感結構,節約版圖面積。VCO最終整體原理框圖如圖3所示。

圖3 壓控振蕩器原理框圖

其中MP1、MP2 和MN1、MN2 為差分負阻生成對管,用于將電流轉換為震蕩能量,L 和(CV,1)與(CV,2)組成了LC 振蕩電路,其中CV 代表可變電容器。4C、2C、C 分別代表固定電容,用于調諧VCO 的振蕩頻率范圍。B0、B1、B2 分別代表可變固定電容的開關管,用于控制電容接入。代表電調端。

最終形成的芯片版圖如圖4所示。

圖4 振蕩器的最終設計圖

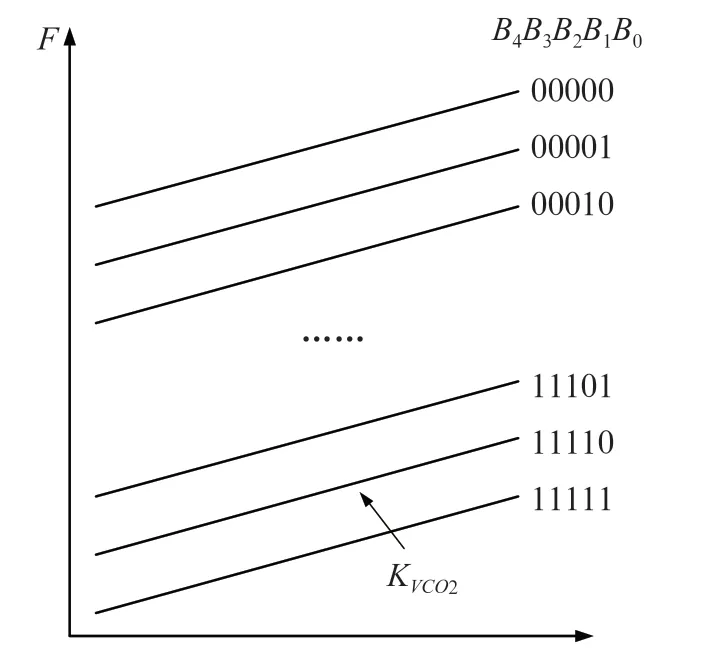

5 最優頻帶選帶技術

為了實現輸出頻段的連續性和更好的相位噪聲,所以VCO 的多個頻段是相互重疊的,如圖5所示。即實現相同的頻率輸出,可以選擇不同頻帶和不同低熱控制電壓。而為了達到最好的相位噪聲指標,應該選擇能使VCO 工作在頻段中心點附近的那個頻段。因為,工作在頻段中心點的VCO 溫度漂移最小。而且,VCO 應用在VCXO 結構中時,只有讓VCO 工作在頻帶中心點,才使得電荷泵的NMOS 和PMOS 匹配最佳,電荷泵的泄漏電流最小,電荷泵的雜散最小,使得相位噪聲達到最優。

圖5 頻帶交疊的多頻帶VCO

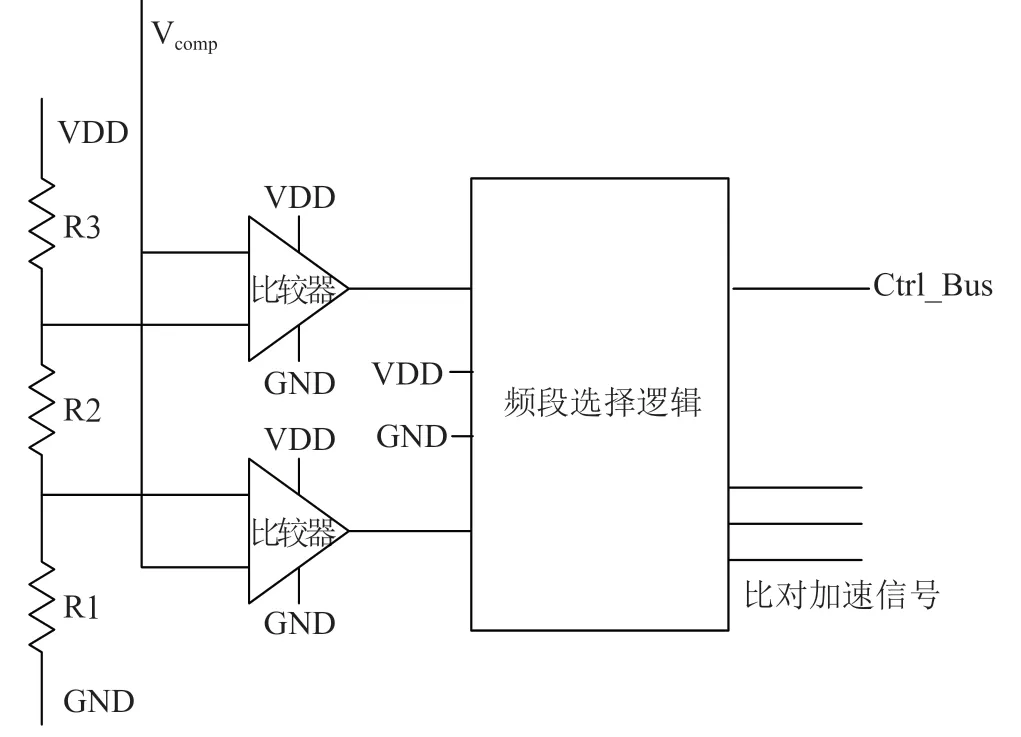

所以,本設計中加入了基于二分法原理的自動選帶技術,這就是VCO 自舉電路。VCO 應用于鎖相環電路時,從VCO的輸出端得到的振蕩信號經過分頻后、與參考頻率進入鑒相器、然后鑒相器結果輸出到電荷泵和環路低通濾波器,即可得到VCO 的電調電壓。增加與上下門限電壓的比較電路和選帶邏輯電路,即可實現頻帶的自動選擇功能。這里的選擇范圍為0.8 ~2.5 V。自適應頻段選擇電路如圖6所示。

圖6 自適應頻段選擇電路

步驟1:選擇合適的電阻來設定所需要的門限電壓,該設計中=2.5 V,=0.8 V。

步驟2:與和相比較,得到兩個值0 或者1。

步驟3:有限狀態機邏輯電路根據這兩個值產生相應的控制碼。

步驟4:VCO 根據控制碼的變化而改變開關電容陣列,使輸出頻率發生相應變化。

步驟5:VCO 的輸出端得到振蕩信號,經過分頻后、與參考頻率比較、比較結果送給電荷泵和LFP,得到新的控制信號。

步驟6:重復步驟2 ~5,直至控制碼不再變化;控制電壓在和之間;VCO 已成功選擇最優頻段,VCO輸出頻率穩定。

頻段選擇邏輯電路的內部結構是一個6 狀態的狀態機,細部結構在此不做分析。

6 芯片測試結果

芯片采用了CMOS 工藝進行設計,采用了高Q 的電容和電感作為LC 諧振回路、互補的NMOS 和PMOS 作為負阻單元、開關電容陣列展寬帶寬降低VCO 靈敏度,以及采用二叉樹的原理設計了最優頻帶選擇算法,從多個角度對相位噪聲進行了優化。

對芯片進行測試,芯片在供電電壓為3.0 ~3.6 V,溫度為-40 ℃~85 ℃之間工作穩定,性能良好,頻率范圍2.3 ~3.3 GHz,壓控增益為40 MHz/V。

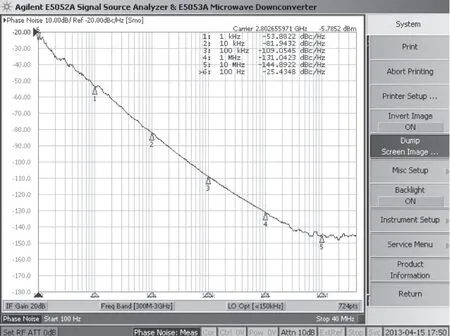

圖7為freq=2.8 GHz 時的典型測試結果。在頻偏10 kHz處相位噪聲為-81 dBc/Hz@2.8 GHz。

圖7 相位噪聲結果

7 結 論

采用國內CMOS 工藝設計了一款頻率范圍2.3 GHz ~3.3 GHz 的VCO,典型相位噪聲測試結果為-81 dBc/Hz@10 kHz。通過采用多種降低相位噪聲的設計手段,最終達到設計預期,滿足了SoC 系統集成低相位噪聲的頻率源類IP 的需求。