機載雷達多任務(wù)多功能中心機設(shè)計

張雨輪

(西安電子工程研究所,陜西 西安 710100)

0 引 言

機載偵察雷達具有全天時、全天候的特點,不受晝夜、雨霧等天氣的影響,在農(nóng)業(yè)普查、地理測繪、災(zāi)害評估、軍事偵察等領(lǐng)域均有廣泛的應(yīng)用。與傳統(tǒng)光學傳感器相比,具備探測距離遠、不受地面自然遮擋物影響等優(yōu)點。不同于普通的測距測向雷達,合成孔徑雷達利用距離向脈沖壓縮技術(shù)和方向合成孔徑原理實現(xiàn)二維高分辨,實現(xiàn)對地面靜止目標的高分辨率成像;通過和差測角和距離—多普勒效應(yīng),實現(xiàn)對地面運動目標的檢測,可以大大提高雷達的信息獲取和感知能力。

隨著該領(lǐng)域技術(shù)的不斷發(fā)展和逐步裝備,合成孔徑雷達成像、雷達動目標檢測已逐漸成為機載偵查設(shè)備的一個功能模塊。隨著近年來不對稱戰(zhàn)爭的發(fā)展,機載偵察雷達越來越多地被應(yīng)用搭載在小型旋翼機、無人機上,完成戰(zhàn)場態(tài)勢感知,提供打擊目標信息和提供毀傷效果評估等任務(wù)。而由于無人機技術(shù)和應(yīng)用的不斷普及,對機載偵察雷達的小型化和功能集成提出了更高的要求。

若沿用傳統(tǒng)架構(gòu)并使用單板機作為硬件平臺,需要數(shù)據(jù)分發(fā)板+中心控制板+數(shù)據(jù)處理板+圖像壓縮板等多達3 ~4 塊板卡硬件資源才能完成系統(tǒng)框架的搭建,難以滿足體積重量和功耗的要求。機載雷達多任務(wù)多功能中心機就是在這個背景下開始研制并投入工程化應(yīng)用。它采用結(jié)構(gòu)小型化和功能一體化集成設(shè)計,采用FPGA +DSP 架構(gòu),進行盡可能大的系統(tǒng)集成和功能復(fù)用,通過一塊標準3U 板卡實現(xiàn)硬件資源復(fù)用,除了具備雷達中心控制板的核心功能外,還具備動目標數(shù)據(jù)處理和SAR 圖像壓縮功能。

1 系統(tǒng)框架和任務(wù)分配

該系統(tǒng)設(shè)計之初有三個約束條件:實時性、機載輕量化設(shè)計以及高運算性能和多功能。

該機載雷達中心控制機,作為整個雷達系統(tǒng)的中樞,主要完成以下功能模塊:工作模式管理、雷達時序控制、波束實時穩(wěn)定、動目標數(shù)據(jù)處理、SAR 圖像壓縮、存儲板控制、雷達內(nèi)部數(shù)據(jù)路由、雷達對外通信。

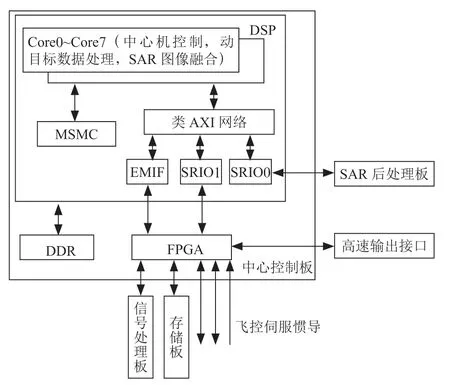

如圖1所示,中心控制機安裝在雷達信號處理機箱內(nèi),對體積重量要求高,并且要求能夠同時完成雷達控制,雷達數(shù)據(jù)處理和圖像壓縮,并集成雷達系統(tǒng)的數(shù)據(jù)流路由和存儲回放控制功能。選用支持浮點運算的高性能低功耗DSP6678,輔之以325T 大容量可編程FPGA,以及必要的輔助電路,DDR3,F(xiàn)lash 芯片等,構(gòu)成雷達中心控制機的硬件架構(gòu)。FPGA 和DSP 間通過高速4X SRIO 高速串行接口互聯(lián),SRIO 單路通信速率為3.125 Gbps,能夠滿足DSP 和FPGA 間高速數(shù)據(jù)傳輸需求。FPGA 通過多路SRIO 接口實現(xiàn)與系統(tǒng)中與信號處理板、存儲板、SAR后處理板及高速輸出接口的通信。中心控制機對外的異步422 接口,包括飛控指令、伺服和慣導(dǎo),同樣通過FPGA邏輯實現(xiàn)。

圖1 系統(tǒng)任務(wù)和硬件資源規(guī)劃

借助8 核DSP 的強大的運算性能和實時性,能夠提供足夠的運算資源完成雷達中心控制,動目標數(shù)據(jù)處理和SAR圖像壓縮等功能。DSP 內(nèi)部運行基于SYSBOIS 多核實時操作系統(tǒng),完成雷達內(nèi)部核間通信和核內(nèi)多任務(wù)調(diào)度。

DSP 的核0 為主控核,用于完成整個雷達任務(wù)調(diào)度。通過數(shù)據(jù)到來中斷驅(qū)動的方式,完成雷達系統(tǒng)的工作模式管理、時序控制和波束穩(wěn)定。通過和板內(nèi)FPGA 的協(xié)同,核0 負責完成雷達系統(tǒng)的數(shù)據(jù)流分發(fā)。通過主動發(fā)起與核1 核2 的IPC 核間中斷和消息,通知進行動目標數(shù)據(jù)處理和SAR 圖像壓縮。接收核1 和核2 的IPC 中斷,將其處理完成的動目標數(shù)據(jù)和SAR 壓縮圖像進行轉(zhuǎn)發(fā)。

DSP 的核1 負責雷達動目標數(shù)據(jù)處理。

DSP 的核2 負責雷達SAR 原始圖像的JPG 壓縮。

2 板卡框架和功能

中心控制機采用FPGA +DSP 架構(gòu),中心控制機設(shè)計的總思路是通過EMIF 接口完成低速接口通信;通過與FPGA之間的SRIO接口進行雷達內(nèi)部和對外高速數(shù)據(jù)通信。

中心控制機內(nèi)通過FPGA 與DSP 內(nèi)的EMIF 接口,實現(xiàn)外部異步RS422 接口與DSP 之間的通信,傳輸?shù)臄?shù)據(jù)類型包括:載荷平臺轉(zhuǎn)發(fā)過來的飛控指令、載荷平臺伺服碼盤信息、機載光纖捷聯(lián)慣導(dǎo)信息、存儲板狀態(tài)信息。

DSP 的核0 負責雷達工作模式管理、雷達時序控制、波束實時穩(wěn)定,存儲板控制。雷達上電自檢后工作在空閑模式,并實時接收伺服碼盤信息和機載光纖捷聯(lián)慣導(dǎo)信息。通過EMIF 接口接收到有效的工作模式指令后,根據(jù)模式類型和探測距離等參數(shù),解算出天線理想波束指向,計算雷達各分機工作參數(shù),計算雷達時序控制參數(shù);根據(jù)實時更新的機載光纖捷聯(lián)慣導(dǎo)信息,通過坐標變換進行波束穩(wěn)定,計算出在平臺當前姿態(tài)下,需要發(fā)送給伺服和波束控制計算機實際的波束控制指向角。

DSP 的核0,把計算得到的伺服指令幀、時控指令幀以及各分機的控制指令等,打包通過與FPGA 的4X SRIO,下發(fā)到信號處理板的時控單元、伺服、頻率綜合器和接收器、波束控制計算機等雷達各分機,完成雷達控制機的任務(wù)下發(fā)。

DSP 的核0 還要響應(yīng)飛控指令中的存儲板控制命令。完成存儲板的記錄指令、回放指令、刪除指令等。

DSP 的核0 運行在操作系統(tǒng)上,實現(xiàn)對多個任務(wù)的響應(yīng)和處理。任務(wù)通過定時器中斷及FPGA 發(fā)送的數(shù)據(jù)到來GPIO 中斷觸發(fā)。運行在DSP 核0 的任務(wù)主要有:飛控指令處理任務(wù)、伺服數(shù)據(jù)接收任務(wù)、慣導(dǎo)數(shù)據(jù)接收任務(wù)、CPI 中斷任務(wù)、數(shù)處數(shù)據(jù)轉(zhuǎn)發(fā)任務(wù)、存儲板控制任務(wù)以及系統(tǒng)監(jiān)控任務(wù)。另外,通過SRIO 門鈴中斷和核間IPC 中斷,實現(xiàn)對SRIO 接口和其他核間事件的響應(yīng)。

由于多個任務(wù)需要通過SRIO_1 進行數(shù)據(jù)傳輸,采用信號量互斥保證傳輸?shù)目煽啃浴?/p>

sem_wait(&semSRIO_1_Occupy);

……//SRIO 發(fā)送函數(shù)

sem_post(&semSRIO_1_Occupy);

DSP 的核1 負責雷達動目標數(shù)據(jù)處理。動目標數(shù)據(jù)處理包括坐標變換、運動補償、點跡凝聚、航跡相關(guān)、航跡更新、航跡濾波、航跡管理和航跡輸出等功能。

DSP 的核2 負責SAR 原始圖像的JPG 壓縮。采用TI 提供的JPG 圖像壓縮庫,能夠高效地完成大幅寬SAR 圖像的JPG 壓縮。

6678 的8 個核可以通過MSMC(共享內(nèi)存)或DDR3對數(shù)據(jù)進行訪問和讀寫。因此對不同核之間數(shù)據(jù)通信時的cache 一致性維護尤為重要。實際應(yīng)用中,要特別注意cache無效和cache 寫回操作的運用,保證數(shù)據(jù)傳輸?shù)恼_性。

cacheWb:cache 寫回的含義是將cache 中的數(shù)據(jù)寫回到存儲器如DDR。多核通信前,需要將需要傳遞的數(shù)據(jù)寫回到MSMC 或DDR3 中,實現(xiàn)有效數(shù)據(jù)的更新。

cacheInv:cache 無效的含義是將cache 中的數(shù)據(jù)視為無效數(shù)據(jù)。當被無效的數(shù)據(jù)需要讀寫時,CPU 會重新將目標數(shù)據(jù)讀取到cache 中操作,從而實現(xiàn)數(shù)據(jù)的更新。這樣才能保證CPU 不會讀到cache 中的臟數(shù),而是MSMC 或DDR3中有效的數(shù)據(jù)。

所有DSP 與FPGA 之間的SRIO 數(shù)據(jù)交互都是通過DSP 的核0 調(diào)度的,核1 和核2 的處理發(fā)起和處理輸出也是通過與核0 的核間IPC 中斷。因此,DSP 的核0 是整個中心控制機的核心。

DSP 的核0 通過SRIO_0 與SAR 后處理板互聯(lián),用于進行SAR 后處理的數(shù)據(jù)交互。

3 控制數(shù)據(jù)流

3.1 板內(nèi)

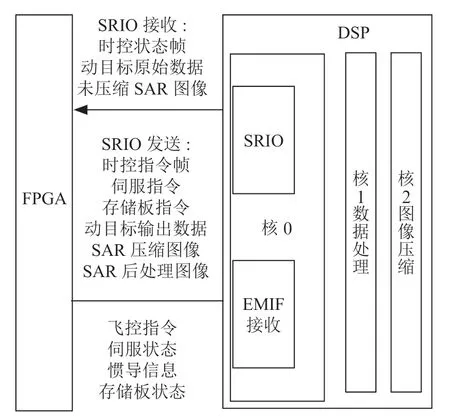

如圖2所示,中心控制機內(nèi)部的數(shù)據(jù)流主要集中在FPGA 和DSP 間的雙向4X SRIO 通路上。從DSP 到FPGA的數(shù)據(jù)類型包括:時控指令幀、伺服控制指令幀、存儲板指令幀和輸出的動目標數(shù)據(jù)、輸出的SAR 壓縮圖像、輸出的SAR 后處理圖像。從FPGA 到DSP 的數(shù)據(jù)類型包括:時控狀態(tài)幀、動目標原始點跡、未壓縮的SAR 圖像。DSP 的SRIO_1 和FPGA 間通過地址映射,來實現(xiàn)不同類型數(shù)據(jù)的交換。

圖2 中心機板內(nèi)硬件模塊組成和功能

3.2 對外接口

FPGA 負責接收載荷平臺轉(zhuǎn)發(fā)過來的飛控指令,機載慣導(dǎo)數(shù)據(jù)和載荷平臺伺服碼盤信息,并將DSP 生成的雷達系統(tǒng)工作狀態(tài)和伺服指令碼轉(zhuǎn)發(fā)給載荷平臺。

FPGA 與信號處理板通過SRIO 互聯(lián),用于接收后者發(fā)送過來的動目標原始點跡/未壓縮SAR 圖像數(shù)據(jù);FPGA 與存儲板通過SRIO 接口互聯(lián),用于SAR 圖片、動目標輸出數(shù)據(jù)、SAR 后處理圖像的記錄/回放數(shù)據(jù)通路;FPGA 與對外高速輸出接口通過SRIO 接口互聯(lián),用于回放SAR 圖片/SAR 后處理圖片到高速輸出接口。

4 系統(tǒng)實時工作流程

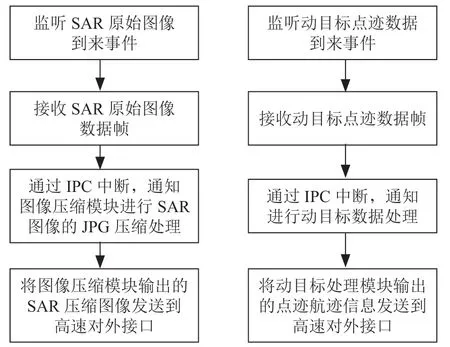

中心控制機接收飛控指令的SAR 模式/動目標模式任務(wù),實時解算出時控參數(shù)并根據(jù)當前飛行姿態(tài)進行波束穩(wěn)定,并下發(fā)時控參數(shù)和分機工作參數(shù)。時序啟動后,中心控制機繼續(xù)響應(yīng)CPI 中斷和慣導(dǎo)到來中斷,實時更新并下發(fā)時控參數(shù)和分機工作參數(shù)。時序啟動后,信號處理板進行動目標信號處理(或SAR 成像信號處理)。

中心控制機FPGA 通過SRIO 接口從信號處理板接收未壓縮SAR 圖像/動目標原始點跡,然后通過板內(nèi)的4X SRIO接口轉(zhuǎn)發(fā)給中心控制機DSP。中心控制機DSP 收到整幅圖像后,通過板內(nèi)IPC 核間中斷通知圖像壓縮模塊進行圖像壓縮(或收到動目標原始點跡后,通知動目標數(shù)據(jù)處理模塊進行動目標數(shù)據(jù)處理)。中心控制機DSP 收到圖像壓縮完成(或動目標數(shù)據(jù)處理完成)IPC 核間中斷后,將壓縮后的SAR圖像(或動目標輸出數(shù)據(jù))通過4X SRIO 回傳給中心控制機FPGA,由中心控制機FPGA一路通過SRIO發(fā)送到存儲板,一路通過SRIO 發(fā)送到高速對外接口。SAR/GMTI 實時工作流程如圖3所示。

圖3 SAR/GMTI 實時工作流程

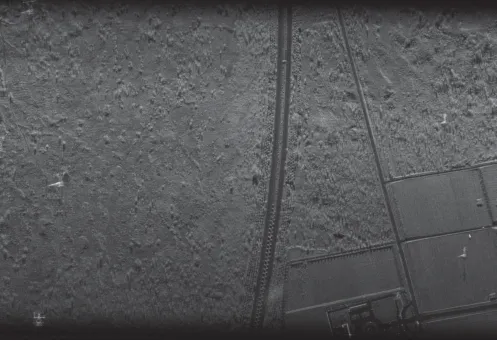

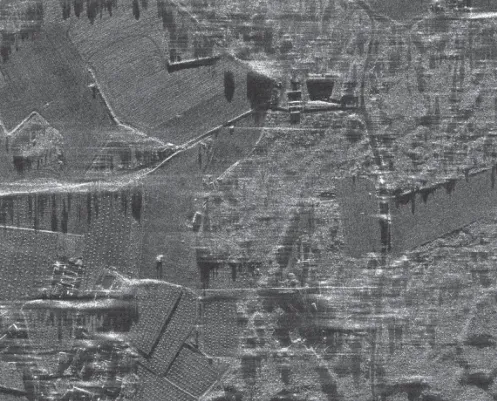

5 成像結(jié)果

該機載偵查雷達進行了多個架次無人機掛飛實驗,完成了多個分辨率合成孔徑雷達成像和運動目標檢測等科目的試驗驗證。整個過程中雷達工作穩(wěn)定可靠,成像清晰,動目標建航穩(wěn)定。實時錄取的部分分辨率下合成孔徑雷達成像圖片如圖4、圖5所示。

圖4 SAR 0.2m 局部圖

圖5 SAR 0.5m 局部圖

6 結(jié) 論

本文介紹了機載雷達多任務(wù)多功能中心機板的設(shè)計和實現(xiàn),它采用標準3U 板卡VPX 設(shè)計,采用FPGA +DSP 設(shè)計框架,由DSP 完成雷達參數(shù)解算、系統(tǒng)控制、動目標數(shù)據(jù)處理和SAR圖像壓縮,由FPGA 和DSP 共同完成與雷達分系統(tǒng)及對外接口高速通信和數(shù)據(jù)路由。掛飛試驗表明,該中心機板具備實時性強,可靠性、功能集成性高等優(yōu)點,具備工程實用價值。