基于FPGA的AD7606B控制器的設計與實現

張良浩,孫瑞祥,于安波

(珠海格力電器股份有限公司,廣東珠海,519070)

0 引言

在電機驅動應用領域,常見的模擬信號采樣功能(ADC)通常集成在MCU中。片內多通道ADC工作模式為分時循環采樣,因此無法滿足某些高速多路同步的采樣需求。在此類應用中,片外ADC芯片(AD7606B)可以更好地提高采樣的同步性和準確性。AD7606B與DSP28335內置ADC的性能對比如表1所示[1~2]。AD7606B為同步采樣、并行傳輸模式;DSP28335內置ADC為分時循環采樣,串行傳輸模式。在均采用8通道采樣的情況下,AD7606B的傳輸速率,比DSP28335內置ADC的傳輸速率快約10倍。

表1 AD7606B與片內ADC轉換模塊參數對比表

使用FPGA實現ADC芯片的控制功能,比起使用傳統MCU可以進一步提升模擬數據的傳輸效率。使用傳統MCU對ADC芯片控制會占用MCU的主頻時鐘,模擬數據的傳輸效率會受到接口讀取效率和主頻處理效率的限制;而FPGA本身為可編程邏輯型器件,其對信號的處理是通過對每個基本邏輯單元(CLB)的構建實現,因此其信號處理的速度與并行度要更為出色[3]。

1 硬件連接及功能說明[4~5]

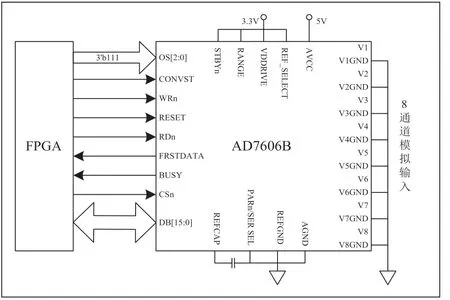

為了最大限度的提升本方案的數據傳輸效率和準確性,AD7606B的設置采用并行接口+軟件模式。FPGA與AD7606B的硬件電路連接圖如圖1所示。

圖1 FPGA與AD7606B的硬件電路連接圖

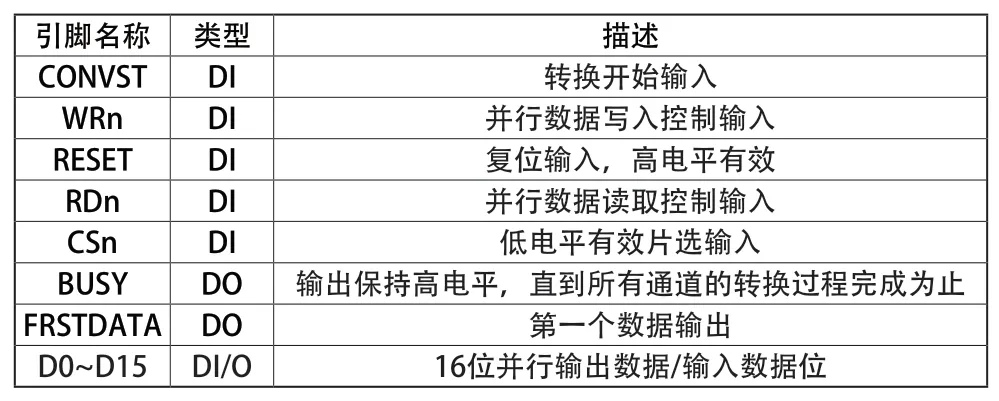

其中,OS2~OS0為硬件模式下過采樣設置引腳,軟件模式下全部置1;PAR/SER SEL為并行/串行接口選擇輸入,并行接口需置0;STBY和RANGE在軟件模式下被忽略均置1;REF SELECT為內部/外部基準電壓選擇邏輯輸入,置1選擇并使能內部基準電壓模式。AD7606B的其余各芯片引腳的功能及描述如表2所示。

表2 AD7606B通信接口功能表

2 控制器狀態機設計

軟件模式下AD7606B的控制器分為兩類:一是ADC控制器,控制AD7606B的模擬數據采集及傳輸;二是寄存器控制器,用于FPGA對AD7606B的寄存器進行讀寫操作。

■2.1 ADC控制器狀態機設計

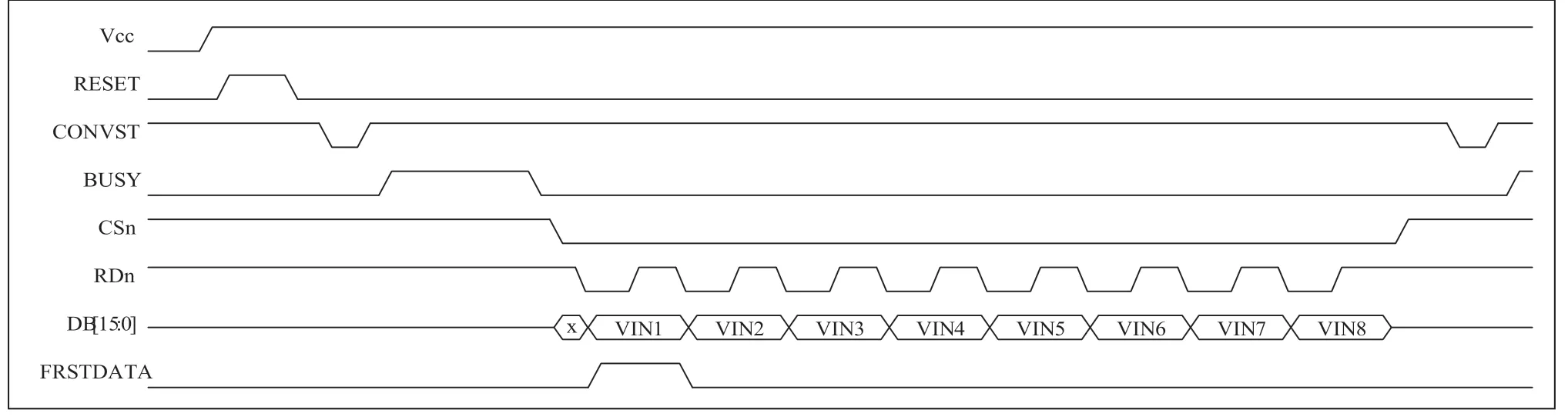

并行接口模式下AD7606B的ADC讀取時序圖如圖2所示。當AD7606B上電后,在10ms后,FPGA控制RESET信號上升。RESET保持至少3000ns高電平,即完全復位。復位完成后,經過253ns后,AD7606B進入空閑狀態。此部分屬于上電時序,不計入ADC控制器狀態機的設計中。

圖2 并行接口ADC讀取時序圖

在空閑狀態下,FPGA控制CONVEST發出上升沿,AD7606B的8個模擬采樣通道同時進行采樣。CONVEST為轉換開始輸入信號,靜默時保持高電平信號。CONVEST上升沿信號后,AD7606B給FPGA反饋BUSY高電平信號。BUSY維持高電平的時間內,AD7606B的8通道執行模擬數據轉換。轉換完成后,BUSY變為低電平信號,轉換時間在0.65~0.85μs之間。通常情況下,應在AD7606B數據轉換完成后,FPGA再對AD7606B進行數據讀取,即CSn信號拉低。

在數據讀取過程中,CSn保持低電平,FPGA通過依次發出8次RDn下降沿信號,AD7606B依次輸出從1通道到8通道的ADC數據,RDn信號的周期需滿足最小保持時間。并且AD7606B在輸出1通道的轉換值時,會發出高電平的FRSTDATA 信號(即1通道輸出標志位),意在告知FPGA當前輸出通道為1通道。完成8個通道的數據讀取后,片選信號(CSn)拉高。至此完成了一個完整的AD7606B數據轉換及讀取流程,AD7606B再次進入空閑狀態。

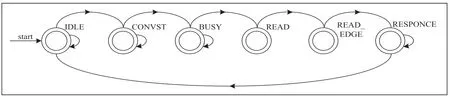

由上述分析,ADC控制器狀態機可分為6個狀態:IDLE、CONVST、BUSY、READ、READ_EDGE和RESPONSE,各狀態間的轉換關系如圖3所示[6]。

圖3 ADC模式狀態機轉換圖

IDLE:空閑狀態。所有信號及變量復位,得到控制指令,進入轉換開始狀態;

CONVST:轉換開始狀態。FPGA拉低CONVST信號,再拉高CONVST信號。得到AD7606B反饋的BUSY高電平信號,進入忙碌狀態;

BUSY:忙碌狀態。得到AD7606B反饋的BUSY低電平信號,進入讀取狀態;

READ:讀取狀態。FPGA拉低CSn和RDn信號,將16bit數據讀入數組中,并進入讀取邊沿狀態;

READ_EDGE:讀取邊沿狀態。FPGA拉高RDn信號,并邊沿計數加1。如果邊沿計數小于8,進入讀取狀態;如果邊沿計數為8,進入應答狀態;

RESPONSE:應答狀態。應答狀態變量置1,并進入空閑狀態。

■2.2 寄存器控制器狀態機設計

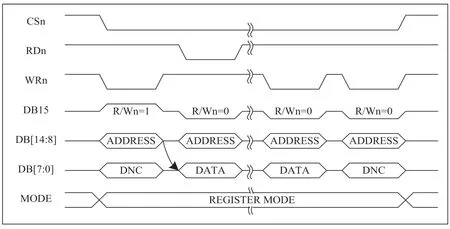

AD7606B默認工作模式為ADC模式,需要通過讀任意寄存器操作進入寄存器模式;當需要恢復到ADC模式時,需寫入地址0x00。AD7606B的寄存器讀寫時序圖如圖4所示,包括讀寄存器、寫寄存器和退出寄存器模式三部分。

圖4 并行接口寄存器讀寫時序圖

寄存器讀取通過兩幀執行:首先將讀取命令發送到AD7606B,其次是AD7606B輸出寄存器內容。

在第一幀中:

CSn和WRn置0;

位DB15置1;

位DB[14:8]為讀取寄存器地址;

位DB[7:0]被忽略。

在第二幀中:

CSn和RDn置0;

位DB15置0;

位DB[14:8]為被讀取寄存器地址;

位DB[7:0]為讀取數據。

寄存器寫命令通過單幀執行:

CSn和WRn置0;

位DB15置0;

位DB[14:8]為寫入寄存器地址;

位DB[7:0]為寫入數據。

退出寄存器模式命令同寄存器寫入命令時序格式相同,需寫入地址0x00,數據被忽略。

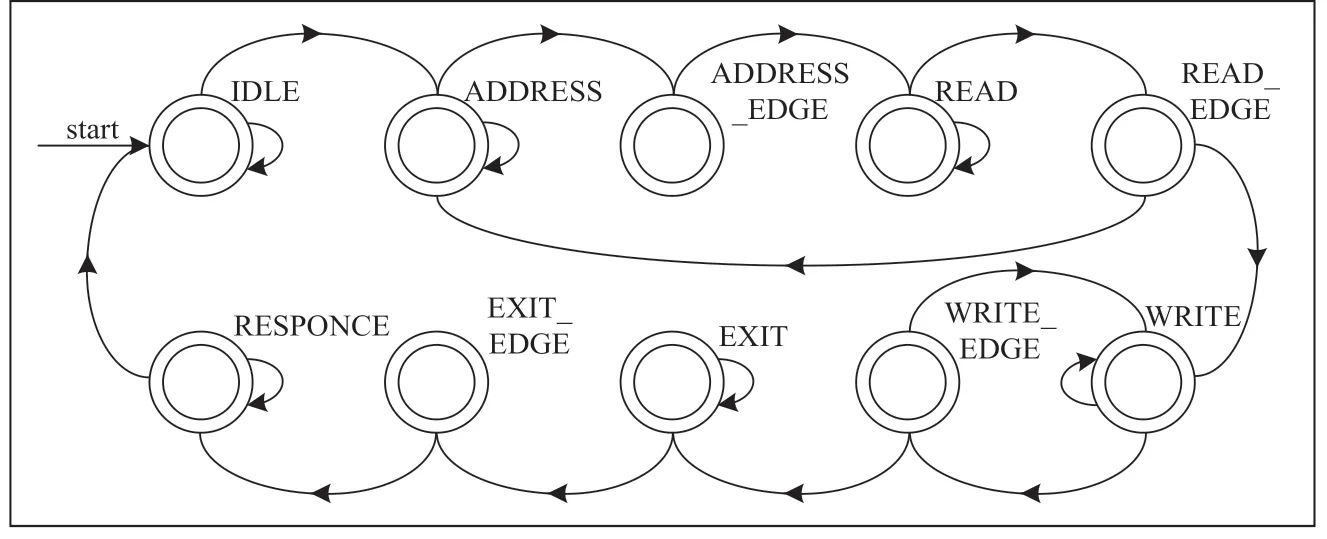

由上述分析,寄存器控制器狀態機可分為10個狀態:IDLE、ADDRESS、ADDRESS_EDGE、READ、READ_EDGE、WRITE、WRITE_EDGE、EXIT、EXIT_EDGE和RESPONSE。各狀態間的轉換關系如圖5所示。

圖5 寄存器模式狀態機轉換圖

IDLE:空閑狀態。所有信號及變量復位,得到控制指令,進入寄存器讀寫狀態;

ADDRESS:地址狀態。FPGA拉低CSn和WRn信號,并對數據線寫入{1'b1,address[6:0], 8'hxx},進入地址邊沿狀態;

ADDRESS_EDGE:地 址邊沿狀態。FPGA拉高WRn信號,并地址邊沿計數加1,進入讀取狀態;

READ:讀取狀態。FPGA拉低RDn信號,AD7606B反饋16位并行數據。FPGA讀取其中低8位所讀寄存器數據,進入讀取邊沿狀態;

READ_EDGE:讀 取 邊沿 狀 態。FPGA拉 高RDn信號。如果地址邊沿計數小于n1,進入地址狀態;如果等于n1,則進入寫入狀態;

WRITE:寫 入 狀 態。FPGA拉 低WRn信號,并對數據線寫入{1'b0,address[6:0],data[7:0]},進入寫入邊沿狀態;

WRITE_EDGE:寫入邊沿狀態。FPGA拉高WRn信號,并寫入邊沿計數加1。如果寫入邊沿計數小于n2,進入寫入狀態;如果邊沿計數為n2,進入退出狀態;

EXIT:退出狀態。FPGA拉低WRn信號,并對數據線寫入{1'b0,7'h00,8'hxx},進入退出邊沿狀態;

EXIT_EDGE:退 出 邊 沿 狀 態。FPGA拉高WRn信號,進入應答狀態;

RESPONSE:應答狀態。應答狀態變量置1,并進入空閑狀態。

3 測試驗證

本文FPGA開發使用的Quartus開發環境,其內部集成了SignalTap II邏輯分析儀,用于分析數據變化。SignalTap II是利用FPGA內部的邏輯單元和RAM資源實時捕捉和顯示信號[7]。與Modelsim仿真不同在于,SignalTap II需要與硬件結合,程序在FPGA中運行時實時顯示FPGA各引腳及內部信號的測試數據。本文通過SignalTap II來測試所述狀態機的工作波形,進而驗證狀態機設計的正確性。

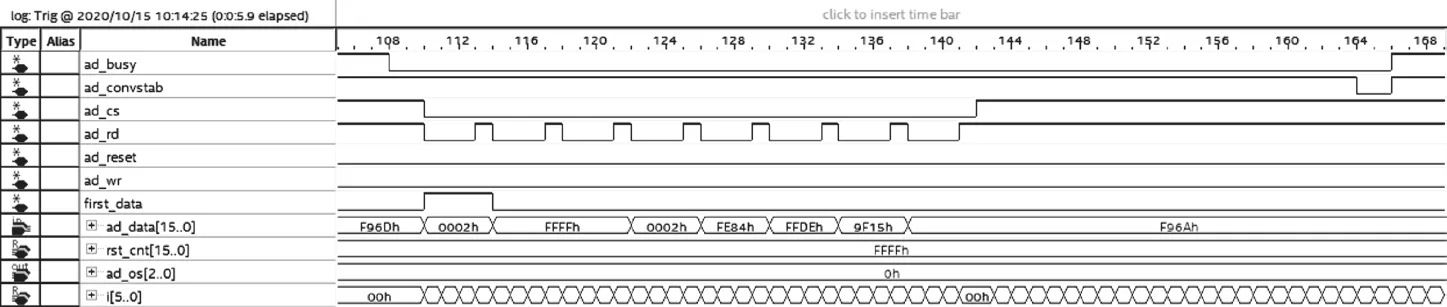

■3.1 ADC模式狀態機驗證

FPGA在ADC模式下的測試信號波形如圖6、圖7所示。可以看出各控制信號線和數據信號線的工作時序與圖2相一致。在數據讀取段的局部波形圖7中,可以更加清楚地看到各信號間的時間間隔。程序中所用時鐘為50MHz,由此計算出的各信號的建立時間、保持時間等時間間隔均滿足最小時限。

圖6 ADC模式下測試信號波形圖

圖7 ADC模式下測試信號局部波形圖

■3.2 寄存器模式狀態機驗證

寄存器模式狀態機的測試波形如圖8所示。測試波形由一次讀取、一次寫入和退出寄存器三部分組成,各控制信號和數據信號的時序均與圖4一致。讀取寄存器地址0x02,讀取數據為0x08,為該寄存器的默認數據。寫入寄存器地址0x03,寫入數據為0x22,該數據設置了AD7606B的通道1、2的輸入范圍為±10V。退出寄存器地址0x00,數據位忽略。

圖8 寄存器下測試信號波形圖

4 結束語

本文通過對AD7606B的并行接口通信時序分析和狀態機的設計,實現了AD7606B控制器功能。經過對通信關鍵信號測試,結果符合設計預期。本文中所設計的AD7606B控制器可以滿足各類電機控制所需的模擬信號采集需求,并且易于廣泛移植。