相控陣雷達信號處理器的FPGA 設計與實現

王成峰,王 鑫,邵志飛,魯冬亮

(93305 部隊,沈陽 110031)

0 引言

雷達的縮寫Radar,來源于“Radio Detection and Ranging”,使用電掃描的相控陣雷達可以使用相位來控制雷達波束的方向,主要用于確定目標的性質,測量目標的位置和運動參數,搜索目標。 由許多小天線單元組成的陣列是相控陣雷達天線,改變每個單元的相位可以產生不同的波束方向,每個單元有一個可控移相器。 一般來說,有源和無源兩種為相控陣雷達,在無源相控陣雷達中,發射器和接收器是共享的,數量有限。

1 信號處理功能的FPGA 軟件設計

1.1 FPGA 開發流程

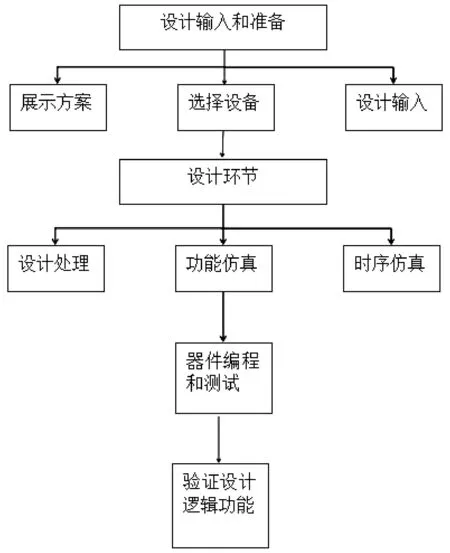

Xilinx 的ISE 是本主題的FPGA 開發軟件,主要包括以下幾個FPGA 開發過程步驟[1],第一步是設計輸入和準備。 第二步是設計環節,包括設計處理、功能仿真和時序仿真。 第三步是器件編程和測試具體流程如圖1 所示。 展示方案通常采用自頂向下的方式搭建系統框架,選擇需要的設備,設計輸入包括波形輸入、原理圖輸入和硬件描述語言輸入。 設計人員在輸入原理圖方面具有廣泛的電路知識,并且能夠從系統的元件庫中調用元件來繪制原理圖。 但是,需要重新輸入原理圖,因為PLD 器件不同。 波形輸入方法通常包括功能測試向量和輸入模擬,使用文本硬件描述語言編寫代碼,編程語言與過程無關,比較常用的是Verilog HDL和VHDL,易于轉換,效率高,且具有強大的邏輯描述和模擬功能。 在本課題使用Verilog HDL 輸入,在編譯之前功能仿真是驗證設計的邏輯功能,適用于無延遲的特征檢測。

圖1 FPGA 開發流程結構

1.2 FPGA 信號處理器程序框架

利用和差三通道波束回波數據的DBF 處理器輸出,對信號處理器目標進行檢測,并對不同的信號模式進行信號處理[2]。 通過高速 SRIO 將處理后的數據FPGA 發送給DSP,將處理結果發送給主控模塊。 調整相應接收機的速度跟蹤環的接收門閘脈沖、本振頻率、發射頻率等,將相應的控制信息反饋給接收機。 在FPGA 上實現本研究的一部分,通過3 個MGT 通道(Tile1,TileO,Tile2)DBF 處理器將回波數據發送給信號處理器,通過高電平處理后的數據發送給DSP -speed SRIO 進行處理,選擇相應的處理模塊進行處理,由其判斷回波信號數據的類型。 通過MGT 模塊接口DBF 處理器向信號處理器發送回波信號數據,傳輸協議使用32 位數據幀。 幀結構包含數據、幀頭和檢查,防止數據傳輸錯誤,保證數據傳輸可靠,幀頭采用幀類型顯示、同步信息等校驗。

1.3 HPRF-PD 模式信號處理模塊的FPGA 設計

FPGA 在HPRF-PD 模式下,主要實現窄帶和波束回波信號FFT 處理、寬帶和波束回波信號匹配濾波等相關部分[3]。

1.3.1 用于HPRF-PD 寬帶和光束信號匹配濾波的FPGA 設計

寬帶和波束信號的匹配濾波主要用于實現FPGA,在距離搜索通道中,32 位浮點數在匹配濾波的結果轉換,然后發送給DSP 進行處理。 按時間相反順序排列的輸入信號可以表示為匹配濾波器,幅度在短時間內變化不大,由于HPRF-PD 信號的脈寬很短,設計時可以簡化匹配濾波器的系數,均視為單元1。 數據模塊、時鐘模塊和匹配濾波器模塊等在程序中均有包含,可以看出,300 MHz 為程序的主處理時鐘,通過硬件板上200 MHz 晶振的Clocking Wizard IP 核差分輸入產生,同時輸出復位信號。 從解幀模塊接收到的波束回波信號和HPRF-PD 寬帶是數據模塊中的數據,匹配濾波器系數和信號數據的時域卷積是匹配濾波,即相乘、移位、累加的過程,如式1 所示。

該設計中1 為所有匹配濾波器系數,避免數據與濾波器系數相乘。 回波數據的I,Q 通道在實現過程中,采用RAM 存儲器、減法器和累加器的組合設計。如果輸入數據的個數不大于濾波器系數的個數,將每次累加的結果存儲在內存中,通過累加器對輸入信號數據進行累加,以方便后續的減法運算。 同時,0 為減法器的負端置,累加器的輸出結果接到減法器的負端。如果輸入數據的數量開始超過過濾器的長度,必須減去最初輸入的舊數據,每次添加新的輸入數據。 RAM的輸出端from ram 按順序讀取第一個存儲的數據,匹配濾波處理的結果是減法器減法的輸出,通過調用FPGA 的IP 核來實現程序中的減法器、累加器和RAM存儲器。

1.3.2 HPRF-PD 寬帶和波束信號的距離跟蹤的FPGA 設計

在FPGA 上實現的HPRF-PD 模式距離跟蹤通道,主要包括速度門窄帶濾波以及前門和后門門控,FPGA編程框架主要包括CIC 濾波器提取、門控和多普勒校正以及兩個一級半帶濾波器濾波[4]。 HPRF-PD 寬帶和波束信號的距離跟蹤的FPGA 設計如圖2 所示,該設計需要對40 MHz 為采樣率、30 MHz 為帶寬的寬帶信號進行數字濾波和抽取,最終獲取窄帶數據。 I/Q 是通道窄帶濾波器組必須滿足的頻率響應特性。 在本研究中,總抽取率為Dc=1 600,因為I 和Q 窄帶濾波器輸出的基帶回波數據f=40 MHz 和數據速率fouf=25 kHz。設計CIC 濾波器時,歸一化旁瓣電平優于-60 dB,提取后混入有效帶寬±8 kHz 的帶外抑制優于-100 dB,需要確保有效帶寬是好的。 寬±8 kHz 內的通帶抖動優于1 dB,5 級級聯CIC 濾波器可以滿足設計需求,由上可知,首先生成一個長度為400 的序列,抽取因子選擇為D1=400,1 個序列的5 級卷積就是5 級CIC 濾波器的脈沖響應,1 級CIC 濾波器的脈沖響應,首先將多普勒f和包含該信息的寬帶回波信號數據乘以多普勒補償因子,然后將補償后的數據送到CIC 抽取濾波器。 調用FPGA 的CIC 編譯器IP 核完成CIC 過濾和抽取。 400為抽取率設置,5 為級聯數設置,梳狀濾波器延遲因子設置為1。

圖2 HPRF-PD 寬帶和波束信號的距離跟蹤的FPGA 設計結構

1.4 LFM 模式信號處理模塊的FPGA 設計

波束通道脈沖壓縮模塊在乒乓結構的內存中接收到的波束回波信號數據存儲,利用FIR 濾波器完成脈沖壓縮過程并將結果發送給MTD 模塊[5]。 在乒乓RAM 內存中為防止數據丟失,接收到I 和O 數據存儲。通過輸入數據選擇單元和RAM B,輸入數據的同時分配給RAM A,在第一個數據緩存周期中,在RAM A 中輸入數據存儲。 在第二個數據緩存周期中,在RAM B中輸入數據存儲,同時由輸入數據選擇單元切換RAM A 中存儲的數據,送到后續處理模塊進行處理。 在第三個緩沖周期,將輸入數據放入RAM A,再次切換輸入數據選擇單元,同時切換輸出數據選擇單元,讀取RAM B 中存儲的數據,這個循環確保輸入和輸出數據是連續的。 如果使用乒乓操作從一個RAM 中讀取數據,可以將數據存儲在另一個RAM 中。 特別適合流水線處理,因為輸入和輸出數據流在模塊的兩端都是不間斷的。 在FPGA 處理中,將數據輸入RAM 時,需要產生一個與數據一一對應的地址總線信號。 FPGA 讀/寫控制模塊需要RAM A 和RAM B 的讀寫控制,以及輸入信號線、兩組地址線、輸出數據總線,分別進行操作。乒乓RAM 的輸入部分包含復位信號rst、輸入數據din、時鐘信號clk,需要一個信號來控制RAM B 和AMA 之間的切換,控制部分主要是兩個RAM 的讀寫切換信號,控制兩個RAM 的寫入和讀取使能。 根據1 位控制信號的高低,與地址信號類似,兩個RAM 的doutl,輸出部分主要是輸出dout0,1 取2 后的輸出dout。 0 為用于切換RAM 的控制信號設置時,在RAM0 中輸入數據存儲,并輸出存儲在RAM1 中的數據。 如果為1,則輸入數據存儲在RAM1 中,RAM0 中的數據為:輸出。 每次數據存儲完成時,該控制信號加1。

2 信號處理各FPGA 功能模塊結果分析

2.1 HPRF-PD 模式的信處模塊調試結果

在HPRF-PD 模式距離搜索信道中,匹配濾波的結果是寬帶噪聲和信號的加入,虛部代表紅線,實部代表藍線[6]。 通過調試接口導出FPGA 處理的數據,將其另存為*. txt 文件。 使用MATLAB 對數據進行分析,并與MATLAB 中實現的匹配濾波的結果進行比較。 可以看到,FPGA 處理和MATLAB 處理得到的結果是一致的,在橫軸為21 時得到最大值。 CPI1 和CPI2 在HPRF-PD 模式速度搜索通道中,具有相同的脈沖重復周期,而CPI3 和CPI4 具有相同的脈沖重復周期。 經FFT 處理后,數據傳送到 DSP 進行進一步處理。

2.2 SRIO 接口模塊調試結果

在SRIO 程序中,表示FPGA 與DSP 的連接已經成功建立為將FPGA 端的Port_initialized 顯示信號設置。此時,FPGA 作為從設備,發出DSP 請求。 一旦建立連接,FPGA 存儲空間就會對DSP 完全開放。 DSP 可以通過啟動NWRITE 指令向FPGA 存儲空間寫入數據。以編程方式將RAM 寫入起始地址設置為0x00120000。而從寫入的數據0x12345678,每次加1。 同樣,DSP 可以使用 NREAD 命令讀取FPGA 的RAM(地址設置為0x00560000)。 可以根據需要設置讀寫地址,可以設置多個RAM 進行讀寫。 地址線的高位用于選通需要操作的RAM,地址線的低位用于讀寫特定的RAM。 在調試程序時,可以看到FPGA 接收端數據和DSP 發送的數 據 每 32 位(4 字 節) 進 行 一 次 反 轉。 比 如0x1234567812345679 變成0x7856341279563412,接收到的數據需要轉置。 硬件開啟并下載程序時,FPGA 端的端口初始化信號和鏈路初始化信號可以正常上拉,DSP 也檢測到端口0 上的FPGA。