基于FPGA+AD7606 的多通道數據采樣系統設計與實現

蔣思宇,王 斌,余龍海,余騰飛

(1.武漢科技大學信息科學與工程學院,湖北武漢 430081;2.大力電工襄陽股份有限公司,湖北 襄陽 441057;3.湖北春田電工技術有限公司,湖北 武漢 430073)

“雙碳”目標的提出,促進了我國能源生產和消費的深入推進,同時也對電力系統尤其是配電網提出了更高的要求[1]。柔性互聯配電網有效實現了多個交直流區域的互聯,其將在未來電力系統轉型中扮演關鍵角色[2-3]。傳統配電方式向柔性互聯配電轉變,要求電力系統具備更強的控制、保護及測量能力,這也使得系統中控制、監測的反饋信號較多,其中包括交直流信號。為了使這類信號能夠被實時監測到,需要對其進行嚴格的同步性監測和處理,這意味著對于系統內的整個采樣電路而言,采樣精度和速度的要求必須被滿足。

該文利用具有較好采樣特性的AD7606 采樣芯片設計采樣電路,基于Altera 公司的EP4CE10F17C8型FPGA 進行采樣控制處理,充分結合狀態機思想,利用Verilog 語言編程設計采樣芯片內部的邏輯時序。實驗結果表明,該AD 采樣系統的設計有效,采樣精度及采樣可靠性滿足要求,能夠明顯提高處理器的控制效率。

1 整體設計

可編程邏輯器件FPGA 具備時鐘頻率高、速度快、并行運算能力優秀等優點,在數據采集領域發揮著重要的作用[4-6]。基于FPGA +AD7606 的采樣系統整體設計如圖1 所示。

根據該結構可知,系統中所有的電壓、電流信號并不會被直接作為AD 采樣的輸入信號,在這之前還需要通過一系列信號變換。首先霍爾傳感器的隔離縮放使得原始的電壓和電流信號全部都轉化為電壓信號,然后區分直流電壓和交流電壓信號,直流信號經過信號跟隨電路,交流信號經過信號調節電路,轉化為滿足AD 采樣芯片要求的模擬電壓信號,保證模擬信號采集的穩定性。在FPGA 控制下,AD 芯片將模擬量轉化為數字量,并將這一采樣結果存儲在內部雙口RAM 中,方便系統隨時讀取。另外,為避免電路中從外界輸入的模擬電壓值過高導致芯片燒毀的情況,在該系統中設計了信號跟隨/調理電路,作為AD 芯片輸入信號的物理隔離,同時完成接口芯片之間的電平轉換。

利用Altera 公司的EP4CE10F17C8 型號FPGA作為控制處理器,對采樣芯片進行時序控制,將采集到的數據信號在FPGA 的控制下進行鎖存,直接將其存儲到事先在FPGA 里設置的雙口RAM 中,這種存儲方式能夠有效提高數據讀取的速度和處理器CPU 的處理效率[7-9]。

2 基于FPGA的AD采樣系統

2.1 AD7606簡介

AD 采樣芯片采用的是美國Analog Device 公司推出的A/D 轉化芯片AD7606,該芯片是一款高分辨率、低功耗、同步采樣的高性能模數轉換器。其中,兩個CONVST 引腳使該芯片具備八通道同步采樣的優勢,同時芯片上集成抗混疊濾波器、高速串并行接口等模塊,使數據采集系統的設計更為簡便[10-12]。AD7606 接口電路如圖2 所示。

AD7606 采樣芯片可以靈活地實現串并行輸出,根據其數據手冊,芯片轉換時序圖如圖3 所示。其轉換過程為,首先選擇AD 轉換模式,然后給引腳CONVST 提供負脈沖,此時AD7606 芯片已經被啟動,每當CONVST 的上升沿到來時,系統內部開始進行模數轉換,信號在同一時刻被采樣,引腳BUSY 的輸出為高電平。同樣地,當下降沿到來,表明此刻各通道模數轉換已經結束,并行總線DB[15∶0]輸出的即是在信號同時控制下讀出的新數據。該文設計的基于AD7606 采樣系統選取并行輸出方式,通過FPGA 運行控制,結合硬件電路中常用的狀態機設計思想,完成對AD7606 的時序控制。

2.2 狀態機模型

對于狀態機設計而言,其最大的優勢在于能夠并行完成諸多運算和控制操作,有效提高了控制系統的工作效率。因此,在大多數并行AD/DA 元件的控制中,該模型應用領域較廣[13-15]。

狀態機模型如圖4 所示,下一個狀態輸出由當前狀態和輸入共同決定。

有限狀態機的數學模型可以寫為(Σ,Γ,S,s0,δ,ω)。式中,Σ 是輸入字母表;Γ 是輸出字母表;S是狀態的集合;s0是初始狀態;δ是狀態轉移函數;ω是輸出函數。其中有:

2.3 AD采樣系統的時序設計

在硬件電路中,狀態機的設計思想能夠在一定程度上提升系統整體運行的效果,包括其運行速度和可靠性,同時簡化了硬件編程思路。

在系統硬件編程中,相關內部時序均按照采樣芯片AD7606 的工作原理及轉換時序邏輯設計。

在AD 芯片的控制中,AD7606 轉換控制信號為CONVSTA 和CONVSTB。就采樣通道而言,CONVSTA控制V1、V2、V3、V4 通道,CONVSTB 控制V5、V6、V7、V8 通道。為得到八通道同步采樣轉換效果,該系統將CONVSTA 和CONVSTB進行短接。其中,S0是空閑狀態,此時為高電平,為高電平。根據上文介紹的AD7606 工作原理可知,BUSY 信號是判斷系統內數據轉換是否還在進行的關鍵,這一信號狀態的獲取由邊沿檢測方法實現。當八個通道的數據全部讀取完成后,回到初始S0 狀態。

根據上述狀態機所述轉換過程,繪制出如圖5所示的FPGA 硬件程序設計框圖[15],其設計思路是在FPGA 中采用verilog 語言,通過EDA 開發平臺,結合狀態機設計方法[16],完成FPGA 對AD7606 的相關配置,并將讀取的數據實時存儲在RAM 中,方便DSP對采樣結果的實時獲取,同時有利于不定長度連續地采樣數據信號。對比利用傳統中斷或查詢方式獲取采樣結果,文中的數據獲取方式減小了對DSP 的資源占用,提高了系統運行效率。

3 實驗結果

3.1 數據采集實驗

利用QUARTUS 軟件,該文結合modelsim 聯合仿真實現了基于FPGA 的多通道AD7606 芯片采樣系統的仿真實驗,為使仿真結果更加準確,首先以$random 隨機函數模擬采樣信號,其AD7606 控制時序結果與數據輸出結果分別如圖6 和圖7 所示。

對于芯片AD7606,其編碼輸出結果為16 bit,最高位為符號位:0 表示正數,1 表示負數。因此,當選取的電壓基準值為±5 V 時,其電壓換算的理論值計算公式為:

式中,U表示電壓折算成模擬值的理論電壓值;γ表示采樣碼值的正負十進制數(范圍為-32 768~32 767)。

實驗表明,基于FPGA 設計AD7606 多通道采樣系統能夠有效完成采樣功能,采樣精度及采樣可靠性滿足要求,其采樣結果圖符合上文列出AD7606的轉換時序圖(如圖3 所示),驗證了實驗結果的可行性。

3.2 采樣系統準確率測試

為測試該文所設計采樣系統的準確率,實驗采用Altera 公司的EP4CE10F17C8 型FPGA 作為可編程邏輯控件,這里以鋸齒波的采樣傳輸為例,用信號發生器中的鋸齒波作為模擬信號輸入,仿真綜合后通過軟件自帶的quartus singletap 功能抓取波形,繼而導出數據,將該數據存儲成.mat 文件,利用Matlab軟件畫出該曲線并計算出理論值,將曲線放在同一坐標下進行比較,其結果如圖8 所示。

由圖8 可知,利用AD7606 芯片進行數據轉換,其測量誤差小,說明了該系統設計的準確性。

3.3 采樣系統在柔性互聯配電網中的應用

隨著我國電網技術發展變革進入新階段,對于柔性互聯配電系統設備的要求也越來越高,電壓電流信號的實時監測成為保證電網運行可靠性的重要前提。

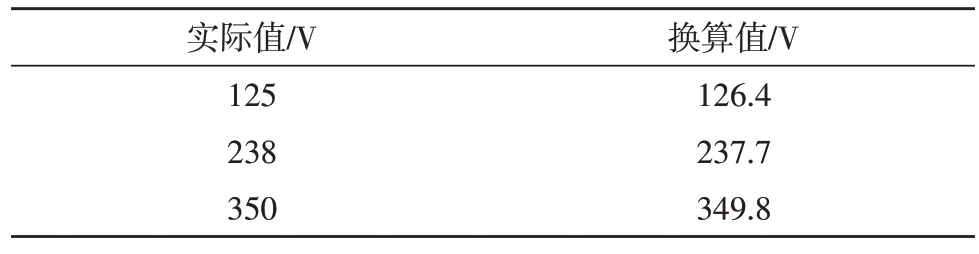

將該文設計的實時采樣控制電路應用在基于柔性互聯技術的企業級配電系統中,這里僅以某一時刻電壓的采集進行說明,表1 分別列出了幾組實際測量值和數字量換算之后電壓值的比較。

表1 電壓值采集比較

從表1 的數據可以看出,兩組值之間的誤差仍然控制在較小范圍內,該誤差主要來源于信號采樣損耗。當運用到實際采樣控制電路中時,實際電壓值越大,AD 轉換的結果就越準確。整體上來看,該采樣系統在采樣穩定性、準確性上均達到了要求。

4 結束語

結合狀態機編程思想,設計了一種基于FPGA+AD7606 控制的實時采樣電路,并將其實際運用在某企業級柔性互聯配電中心電路中。實驗表明,該采樣系統的穩定性、誤差均達到要求,能夠被很好地運用在柔性配電系統中,具有很強的工程實用價值。

FPGA 時鐘頻率高、速度快、并行運行能力強,很好地實現了對于多通道同步采樣系統的控制;同時,其內部集成的獨立運算單元和存儲器資源使其具有良好的數字信號處理能力。基于FPGA 的電路設計控制較靈活,容易在仿真軟件上進行調試驗證,方便移植到各種控制系統中。若針對其他電路系統有不同配置要求,也可以在采樣系統中采用多片AD7606進行設計。