射頻集成電路校準技術綜述

李松亭 顏 盾

①(國防科技大學空天科學學院 長沙 410073)

②(湖南大學信息科學與工程學院 長沙 410082)

1 引言

隨著產品需求逐漸向小型化、低功耗化過渡,尤其是5G大容量通信[1]、雷達探測中高穿透力高分辨率需求[2]使射頻通信頻段逐步向毫米波段過渡,射頻集成電路的制造工藝在需求牽引下逐漸由深亞微米級向納米級過渡,集成電路中元器件之間的失配、工藝偏差、非理想器件特性等都有明顯增大的趨勢,加之元器件射頻模型的不準確性以及封裝等寄生效應的影響,造成射頻集成電路產品成品率過低、產品開發時間過長等問題,給射頻集成電路產品的設計帶來了嚴峻的挑戰。以互補金屬氧化物半導體 (Complementary Metal Oxide Semiconductor, CMOS)工藝偏差帶來的電阻值隨機波動為例,采用歸一化蒙特卡洛仿真,130 nm工藝電阻值的隨機偏差位于3σ內(σ為標準高斯分布的方差),如果將工藝下降到55 nm,隨機偏差可達到5σ。這勢必會導致所設計射頻集成電路性能的降級,甚至無法滿足具體的應用場景需求。上述影響屬于靜態非理想因素,屬于射頻集成電路的一種固有屬性,當一款射頻集成電路封裝完成后,這種屬性會導致射頻集成電路性能的固定比例降級。另外,射頻集成電路的工作過程是一個典型的熱變過程,溫度的改變會動態地改變無源器件的阻抗值以及有源器件的遷移率、介電常數、跨導值等,造成電路性能降級。另外,鏈路增益以及輸入/輸出信號頻率的改變也會對電路性能產生動態影響。這些影響屬于動態非理想因素,屬于射頻集成電路的一種隨機屬性,其會動態地改變射頻集成電路的性能,造成一定程度的性能降級,甚至影響正常使用。

本文主要針對射頻集成電路的性能降級機理進行分析,歸納總結能夠提升射頻集成電路魯棒性的各類校準技術,為高性能射頻集成電路的設計提供堅實的基礎理論支撐。具體內容如表1所示。

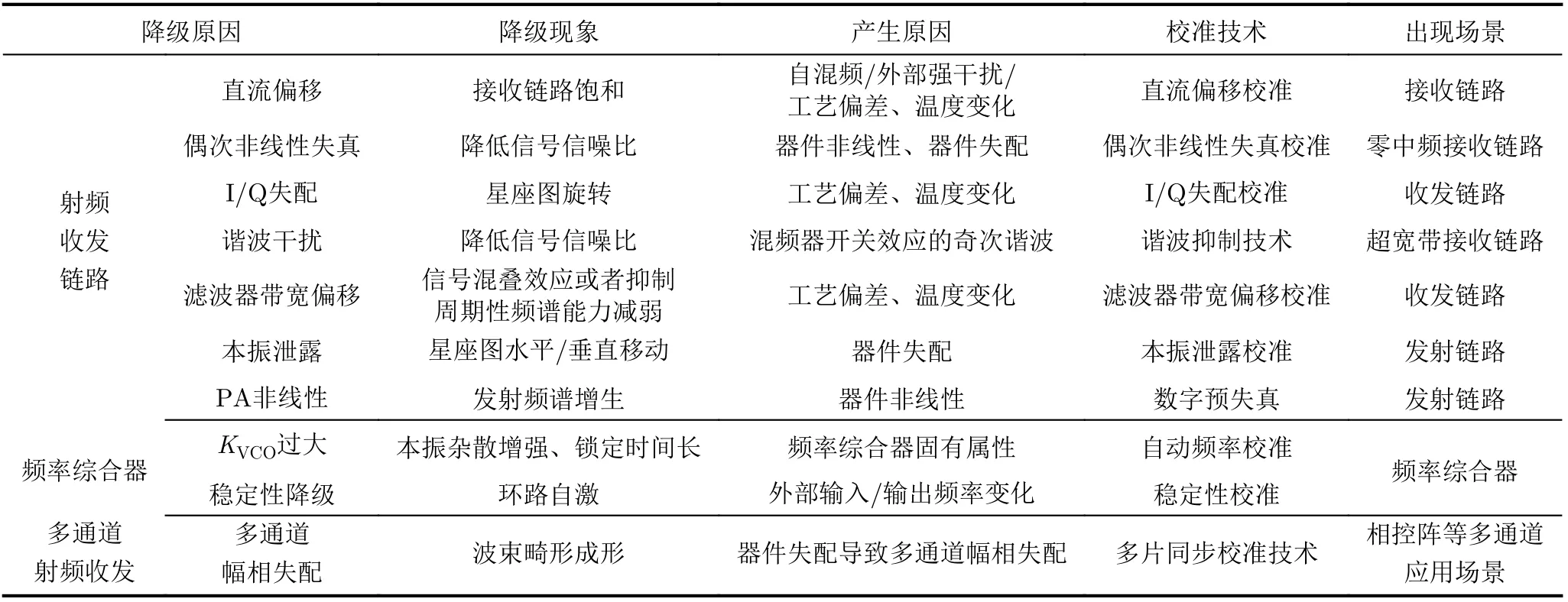

表1 本文校準技術總結

2 射頻收發鏈路校準技術

2.1 直流偏移校準

直流偏移對于射頻接收機的設計是一個極為嚴峻的挑戰,直流偏移的產生主要來自3個方面:(1)混頻器本身的自混頻效應;(2)外部的強干擾在混頻器端產生的自混頻效應;(3)工藝偏差、溫度變化導致的直流偏移。當基帶電路增益較大時,直流偏移極易導致射頻接收鏈路的飽和。

直流偏移校準(DC Offset Calibration, DCOC)通常的做法是在電路中加入交流耦合電容,但是該方法并不適用于零中頻架構以及中頻頻率較低時的低中頻架構。另一種方法是采用無源低通反饋環路[3]或者有源積分[4]反饋環路。反饋式DCOC電路的實時性可以保證靜態和動態非理想因素導致的直流偏移均被有效補償,但是當基帶電路提供的增益較高時,反饋環路中的電容值必須足夠大以確保獲得較低的高通截至頻率,很難在芯片內部實現集成,通常采用多級反饋[4]的形式來大幅降低反饋電容的大小。由于高通截至頻率的存在,上述DCOC方法并不適用于零中頻接收機,否則會導致信號低頻成分的損失,通過降低高通截至頻率可以緩解部分損失,但是反饋電容的面積會大大增加。

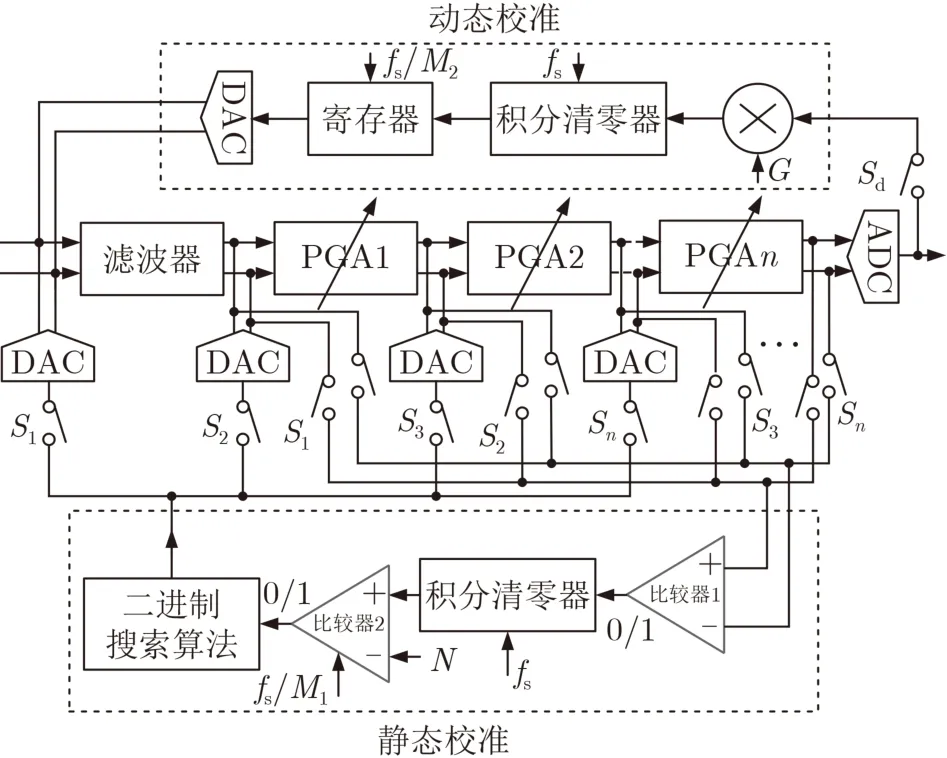

適用于零中頻接收機的DCOC電路[4–7]如圖1所示,該電路包括靜態校準和動態校準兩部分,在內部狀態機的控制下,靜態校準部分依次閉合開關S1~Sn對各電路模塊進行直流偏移校準,靜態校準模塊中的積分清零器每M1個時鐘周期清0一次,N的值通常取0,比較結果反饋至二進制搜索算法模塊通過數模轉換器(Digital to Analog Converter,DAC)以補償電流或者電壓的形式對增益模塊的直流偏移進行校準。靜態校準模塊中的比較器1采用自校準比較器避免其自身的直流偏移對校準結果產生影響[5]。基帶鏈路的DCOC效果與鏈路的增益大小密切相關,為了保證自動增益控制工作模式下的DCOC效果,通常在芯片上電后會遍歷基帶鏈路的增益值并遍歷上述DCOC過程,校準結果預先存儲于查找表中,通過增益值直接查詢補償[4]。為了解決由于帶外強干擾引入的動態直流偏移,可以在靜態DCOC過程結束后閉合開關Sd打開動態DCOC環路[8],動態DCOC環路在數字域進行實現避免模擬域采用的大電容,乘法器的目的主要用于調節高通截止頻率角,增益G的值越小,高通截止頻率角也就越小,但是直流偏移壓制效果也會越差,需要折中考慮。

圖1 適用于零中頻接收機的數字輔助DCOC

2.2 偶次非線性失真校準

奇次非線性失真對射頻電路中的各種失配不敏感,通常可以通過提升電路模塊本身的線性性能進行改善,但是偶次非線性失真對電路中的各種失配因素非常敏感,必須借助一定的校準手段進行提升。偶次非線性失真會導致接收機的輸入2階交調截取點(Input Second-order Intercept Point,IIP2)性能嚴重降級,此現象主要是由下變頻混頻器中存在的各種非線性及失配因素引起的[9]:輸入跨導管的偶階非線性、開關管/負載電阻的失配以及本振信號的非均勻占空比。文獻[9]從電路設計的角度給出了針對性的解決方案,在跨導管源端加入尾電流源與電容并聯結構,在保證跨導級正常工作的同時降低低頻時的等效跨導。另外,通過在開關管的源端加入與寄生電容在本振頻率處諧振的并聯電感減小周期性階梯信號的產生。優化后的IIP2可以達到+78 dBm。

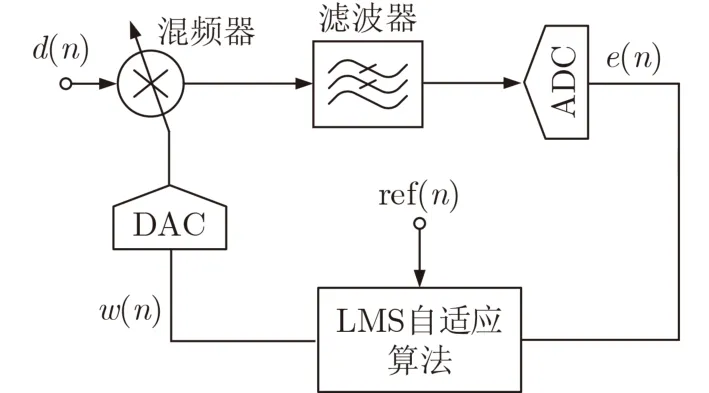

考慮到工藝、電壓以及溫度(Process, Voltage and Temperature, PVT)的影響,偶階非線性失真通常不能僅通過優化電路設計來滿足系統設計需求,同樣需要校準電路的輔助進行失真補償。最小均方(Least Mean Squares, LMS)自適應校準算法是一種典型的用于補償偶次非線性失真的自適應校準算法[10,11],如圖2所示,其中d(n)為實際輸入信號(輸入有效信號和白噪聲的疊加),e(n)為經過偶次非線性失真補償后的實際輸出信號,w(n)為用于校準補償的1階抽頭系數,ref(n)是與偶次非線性失真嚴格相關的參考信號,文獻[10]通過提取混頻器輸出端的共模信號成分并經低通濾波后作為ref(n)信號,文獻[11]通過在基帶算法中產生相應的基帶信號,通過發射與接收閉環的形式對偶次非線性失真性能進行補償校準,ref(n)信號選取為基帶信號的幅值。LMS算法生成的1階補償系數w(n)通過調整混頻器開關管的體電壓[12]、柵電壓[13,14]、混頻器中注入直流偏移電流的大小[15],或者改變用于補償功能的偶次失真量的大小[16]對偶次非線性失真成分進行補償,校準后的IIP2可高達+90 dBm[14]。

圖2 基于LMS算法的自適應偶次非線性失真校準電路

2.3 I/Q失配校準

I/Q失配主要是指收發鏈路中I/Q兩路的幅相失配以及正交本振(Local Oscillator, LO)信號的相位失配,在零中頻接收機中,I/Q失配導致的鏡像頻譜增生會使星座圖產生旋轉,對諸如多進制正交幅度調制(Multiple Quadrature Amplitude Modulation, MQAM)等高階調制系統產生嚴重的影響,對于正交頻分復用(Orthogonal Frequency Division Multiple, OFDM)多載波調制系統,鏡像信號的存在會干擾其子載波成分,惡化信噪比。對于高階調制系統,要求的鏡像抑制能力通常需要超過60 dB,幅相失配必須控制在10 mdB和0.1o以內[17]。在低中頻接收機中,I/Q失配會導致復數域鏡像抑制濾波器的鏡像抑制能力降低,無干擾情況下,低中頻接收機的鏡像抑制能力必須超過16 dB才能保證對信噪比的影響小于0.1 dB[18],在存在干擾的情況下,需要的鏡像抑制能力會明顯增加。對于零中頻發射機,I/Q失配同樣會在有效頻帶內引入鏡像干擾降低有效信號的信噪比,對于低中頻發射機,I/Q失配會導致天線輸出端產生明顯的鏡像干擾信號,污染臨近信道,同時還會降低針對功率放大器線性化的數字預失真精度[19]。

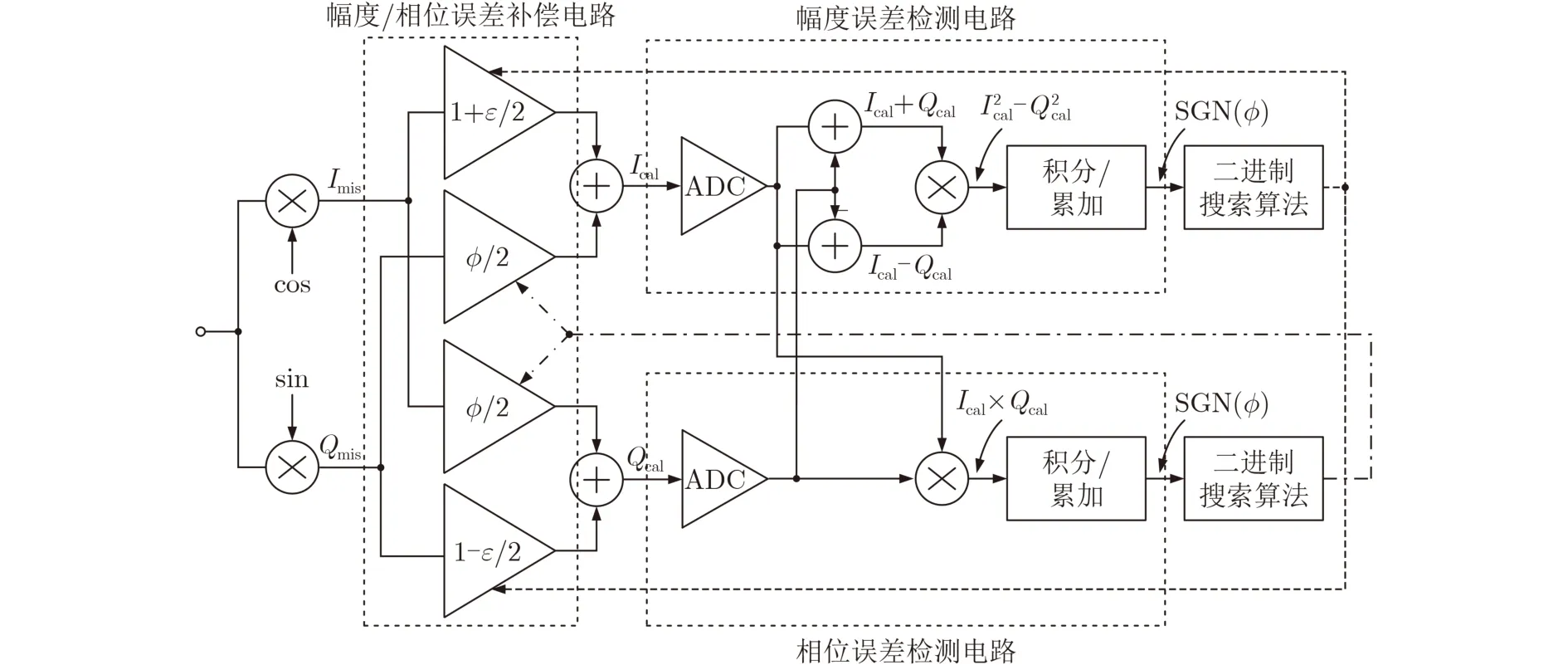

低中頻接收機中的I/Q失配校準模塊通常位于下變頻混頻器和復數域鏡像抑制濾波器之間用以提升濾波器的鏡像抑制能力,采用數模混合設計的方法,具體的補償電路結構如圖3所示[20,21],其中Imis/Qmis, Ical/Qcal分別表示校準前后的下變頻正交信號,ε和φ分別指I/Q通路的幅度和相位誤差。該校準電路中幅度誤差檢測電路和相位誤差檢測電路輸出的均是相應的檢測符號,并通過二進制搜索算法調整幅度/相位誤差補償電路的配置,從而補償正交失配。需要注意的是,幅度/相位誤差檢測電路檢測結果的準確性依賴幅度/相位誤差的大小,較大的幅度/相位誤差會引入較大的檢測結果誤差,因此,如果采用二進制搜索算法,則幅度誤差校準和相位誤差校準必須分時進行,否則會無法完成正常的失配校準。如果使用步進式加減算法則可以同時對幅度失配和相位失配進行校準。輸入端的信號可以是一個單音信號[20]亦或采用經低噪放放大后的白噪聲[21],幅度/誤差補償電路可以在模擬域構建相應的放大器和加法器進行實現[21]。

圖3 適用于低中頻接收機的正交失配校準電路

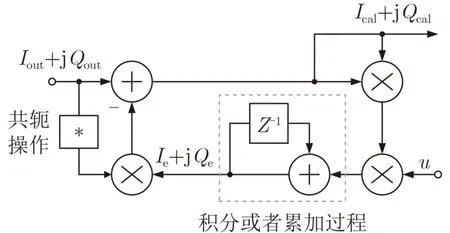

零中頻接收機的I/Q失配校準通常在數字基帶處理模塊中進行補償[22–25],典型校準電路結構如圖4所示[22],其補償原理與圖3相似,只是采用LMS算法逐步將誤差補償電路中補償參數的最優值估計出來。校準過程中的I/Q支路輸入參數只要具有平穩隨機特性,均適用于該校準機制。發射鏈路的I/Q失配需要借助接收機形成回環的方式進行校準,文獻[23]采用串行校準的方式,首先采用內置的本振產生的單音信號注入射頻接收機中對其I/Q通路進行失配校準,然后發射和接收鏈路形成回環,在基帶中基于直接數字頻率綜合器(Direct Digital Synthesizer, DDS)提供單音信號,經過回環鏈路后估計出的I/Q通路失配即為發射鏈路的I/Q失配參數。發射鏈路中的失配校準電路除了在基帶中實現以外,還可以采用具有雙開關結構的上變頻混頻器在模擬域進行實現[17]。為了進一步加快校準速度,文獻[24,25]利用I/Q失配能夠引入鏡像信號的原理,采用多個不同頻率的單音信號[24]或者設置不同的收發本振頻率[25]在頻域上對收發鏈路的鏡像信號進行區分,可以同時對收發鏈路進行校準。

圖4 I/Q失配基帶自適應LMS校準電路

對于寬帶通信系統,I/Q誤差失配除了與PVT,LO相位失配等因素相關外,還與頻率有著明顯的關系(濾波器的群時延失配導致I/Q相位失配與頻率密切相關),文獻[26]通過在回環鏈路的發射輸入端注入兩個不同頻率的單音信號,通過交叉回環連接的方式,利用線性內插可以同時計算出收發鏈路群時延失配與頻率的關系,通過在I/Q支路中引入具有不同群時延特性的FIR濾波器[26]或者負載電容調諧[27]來補償I/Q支路的相位失配與頻率的關系。文獻[28]在文獻[26]的基礎上通過引入相位旋轉模塊有效解決了I/Q幅度失配與頻率之間的依賴關系。針對溫度變化對I/Q失配的影響,文獻[29]提出了一種基于迭代技術的在線追蹤方案,可有效跟蹤溫度變化對發射機I/Q失配造成的影響并進行動態補償。

2.4 諧波抑制技術

諧波抑制技術是軟件定義無線電射頻接收機中的一個關鍵指標[30–32],由于混頻器LO開關引入的奇次諧波,接收機輸入端在無聲表面波(Surface Acoustic Wave, SAW)濾波器或者SAW濾波器帶外抑制性能較差時,輸入端存在的奇次諧波干擾會通過與LO信號的奇次諧波混頻干擾有效頻帶內的信號。

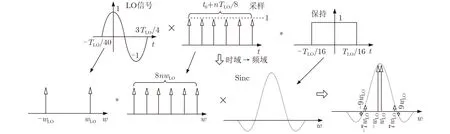

典型的雙平衡混頻器(Gilbert架構)等效于對LO信號進行2倍頻采樣保持,正交雙平衡結構等效于對LO信號進行4倍頻采樣保持,此兩種結構中的本振信號均會提供3/5/7···等奇次諧波,幅度與保持功能對應的頻域辛克(Sinc)函數直接相關,無法滿足諧波抑制功能。諧波抑制的典型電路結構是采用多相(>4)混頻結構[33],以8相為例[34],相應的LO開關頻譜如圖5所示,8倍頻采樣可以有效地避免LO信號中3/5次諧波的出現,有效地抑制輸入信號中存在的3/5次諧波干擾。為了抑制更高的奇次諧波,還可以采用16相甚至更高的多相采樣結構[35]。

圖5 八相混頻器本振信號頻域等效圖

為了避免多相電路結構對壓控振蕩器(Voltage Controlled Oscillator, VCO)的高輸出頻率要求以及多相支路累加結構帶來的復雜度,文獻[30]在雙平衡無源混頻器的基礎上提出了一種采樣保持型電容負載結合可調本振信號占空比的組合結構,該結構通過改變本振信號的占空比動態調整Sinc函數幅頻響應的過零點,可以有效地抑制輸入端的各奇次諧波。文獻[36]通過對占空比為25%的四相信號引入相同時間寬度的頻隙和頻帶同樣也會產生相應的諧波抑制能力。文獻[37]采用基于脈寬調制技術提供的本振信號也實現了較好的諧波抑制能力。但是為了實現上述技術,最終的硬件開銷以及設計復雜度并不比采用多相結構占據多少優勢,在具體設計過程中需要折中考慮。

多相本振信號的相位失配以及接收鏈路中的延遲及增益失配會明顯地限制電路的諧波抑制能力,典型情況下,多相混頻結構提供的諧波抑制比在30~35 dB[37],文獻[38,39]提出了采用兩級諧波抑制結構增強電路魯棒性的設計方法,配合對多相本振信號的重定時電路,諧波抑制比可以超過70 dB[39]。但是重定時結構通常面臨亞穩態的問題,且補償的相位精度與重定時時鐘抖動密切相關。文獻[31]提出了基于高精度時間-數字轉換器(Time to Digital Converter, TDC)估計多相本振信號相位失配及補償的具體電路結構進一步改善LO信號的輸出相位關系。文獻[32]提出了一種數模混合的接收機幅相失配校準方法,在輸入端輸入相應的諧波信號,基帶通過對殘留下變頻信號的功率進行估計動態調整多相支路中的增益值以達到最優的諧波抑制性能,校準后的3/5次諧波抑制能力分別超過70 dB和50 dB[32]。文獻[32]還基于仿真手段對輸入諧波頻率與失配參數之間建立了1階對應關系,并在實際測試中驗證了模型的準確性。文獻[40]在數字域首先對多相支路中的失配參數矩陣進行估計,并提出了一種基于優化后Jacobi疊代方法進行諧波抑制的失配參數補償方法,補償后的諧波抑制性能可以超過80 dB,但是該方法需要模擬域提供多相支路輸出,是以犧牲硬件設計的復雜度及功耗為代價的。

2.5 濾波器帶寬校準

射頻接收機中集成的基帶或者中頻濾波器主要用于避免采樣過程中的混疊現象,低中頻結構中還需提供鏡像抑制能力。發射機中由于單邊帶架構的原因,通常集成低通濾波器,起到抑制基帶信號中周期性頻譜的作用。射頻收發機中通常集成連續時間濾波器,主要包括有源電阻電容(Resistor and Capacitor, RC)[6,21,41]以及Gm-C[42]兩種結構,有源RC結構采用閉環結構,線性度較高,但是需要進行復雜的穩定性設計,Gm-C結構采用開環結構,穩定性較好,但是線性度較差。兩者提供的帶寬精度分別與時間常數RC以及C/Gm有關,由于PVT的影響,濾波器提供的帶寬精度通常有±20%的波動范圍[41]。帶寬的波動可能會導致有效信號邊沿頻譜的抑制或者影響采樣過程中的抗混疊效果,導致信噪比的惡化。因此設計過程中需要對時間常數進行PVT補償。

對于有源RC濾波器,典型的補償算法通常采用基于RC時間常數的開關電容充放電機制對帶寬偏差進行校準[6,41–44],但是由于校準自由度的限制,這種帶寬校準電路并不適用于軟件定義無線電射頻收發機的設計中,這是因為在濾波器設計中每增加1個帶寬頻點,就必然要在每一個電容或者電阻網絡中加入一個相應的電容或者電阻元件,導致設計復雜度較高、芯片面積較大。另外,為了適應不同的晶振輸入頻率需求,文獻[45]通過引入一個可變的電阻網絡與其進行匹配,但是僅支持8個不同的晶振輸入頻率,不能滿足對寬范圍晶振輸入頻率的需求。文獻[6]通過增加濾波器帶寬校準自由度,在較低復雜度和較小面積條件下,提出了一種適用于軟件定義無線電應用場景的濾波器帶寬校準機制,但是其校準過程需要構建RC振蕩器以及頻率綜合器及小數分頻器的支持,且校準算法比較復雜,功耗及資源消耗量較高。此外,在文獻[6]的基礎上,文獻[46]通過RC振蕩器與標準參考時鐘的比較,實現了濾波器帶寬的動態校準,避免了溫度波動對濾波器帶寬的影響。在文獻[6,46]的基礎上,一種更簡潔的寬帶濾波器校準方案如圖6所示,此時的電阻和電容既可以用來調節濾波器的帶寬,同時也可以起到校準帶寬精度的作用。該方法需要預先在典型工藝角情況下建立帶寬調整控制信號與調節電壓Vadj之間的查找表關系,通過改變帶寬調整控制信號得到高精度的濾波器帶寬配置。針對Gm-C濾波器,文獻[42]提出了一種收發回環校準機制,通過DDS模塊動態改變發射單音信號的頻率,在接收端掃描濾波器的幅頻響應曲線預估濾波器的帶寬,通過與預設帶寬的比較逐步調整Gm的值提升濾波器帶寬精度。文獻[47]將跨導放大器的Gm值通過反饋結構等效于一個電阻值,并通過構造一個RC振蕩器來校準其時間常數。文獻[48]通過構造Gm-C積分器,并通過自動鎖幅原理與參考電壓相比較來校準時間常數的值。

圖6 寬帶濾波器帶寬校準電路

通過人為增加濾波器的帶寬避免由于PVT波動造成的帶寬壓縮抑制有效信號的邊緣頻帶也可以保證電路的正常功能[49],但是為了避免采樣混疊或者獲得更好的周期頻譜抑制比,必須提高ADC/DAC的采樣頻率,同時更高的帶寬設置還需要更高的運算放大器增益帶寬積或者更高的Gm,會明顯增加電路的整體功耗。

2.6 本振泄露校準

LO泄露同時存在于射頻的收發鏈路中,主要是由I/Q支路中存在的直流偏移、混頻器開關管以及驅動管的失配導致的。接收鏈路中的LO泄露向解調方向會導致直流偏移飽和接收機,向天線方向會導致直接泄露。直流偏移可以通過直流偏移校準有效抑制,向天線方向的直接泄露由于低噪放較高的反向隔離度也可以忽略不計。但是對于對線性性能要求較高的Mixer-first接收機而言[50],為了避免對其他通信系統的干擾,必須對缺少反向隔離導致的天線端LO輻射進行抑制。文獻[50]通過將混頻器進行DAC化,實現了對LO開關管及驅動管1%的尺寸微調功能,有效抑制了LO的反向輻射大小。

發射機中的LO泄露會導致調制信號星座圖的移位(直接上變頻)、發射頻譜增生(帶子載波上變頻),對于FDD收發機,嚴重時會飽和接收鏈路。發射鏈路的LO泄露校準通常采用收發回環的校準方式[25,26,51–55],通過泄露幅值檢測(圖7)[54]、下變頻至基帶或者直流進行數字域功率檢測(頻域檢測[25,27,53]或者時域檢測[52])等方式估計泄露LO信號的大小,并與預設功率值進行比較,產生的反饋信號通過DAC對I/Q兩路的失配進行電壓或者電流補償以抑制LO泄露的大小。為了避免功率預估過程引入的電路設計復雜度,文獻[51]提出了數字域微分及符號量化的方式并采用二進制搜索算法對I/Q兩路的直流失配分別進行補償,復雜度得到了有效降低,且校準時間僅為16 μs。文獻[56,57]采用高精度ADC直接對發射機中的差分支路進行直流偏移檢測,根據反饋的差值對相應差分支路進行補償,避免了收發回環過程帶來的較高設計復雜度,但是此類方法對ADC的精度要求較高,且無法校準由于混頻器開關管以及驅動管的失配導致的LO泄露。

圖7 發射端載波泄露校準電路

2.7 數字預失真

功率放大器(Power Amplifier, PA)的線性化是射頻集成電路中一項重要的性能優化工作,由于AM/AM以及AM/PM失真的存在,PA的輸出頻譜中存在大量的交調失真信號,除了導致嚴重的頻譜增生效應外,還會惡化發射機的發射信號性能,尤其是對于具有較大峰均比的高階調制。通常采用功率回退的方式增大PA的線性性能,但是會明顯降低PA的功率轉換效率。為了在較高效率的情況下減小失真的存在,包絡跟蹤PA[58]、G類(Class-G)PA[59,60]、 異相(Outphasing)PA[61]、多合體(Doherty)PA[62]、Class-G+Doherty混合PA[63]等結構分別被提了出來,但是上述結構僅從PA本身的構造出發,為了保證較高的增益及轉換效率,仍無法有效遏制PA線性性能的惡化。數字預失真(Digital Pre-Distortion, DPD)技術通過在PA前級基帶電路中加入預失真模塊補償AM/AM以及AM/PM失真來有效提升PA的線性性能,在目前的高性能PA設計中得到了廣泛的應用。

本節主要從PA行為模型、DPD學習結構、DPD參數辨識方法以及DPD補償模塊模型4個方面對DPD技術進行總結。

PA的行為模型包含無記憶行為模型[64,65]和有記憶行為模型[66,67]兩種,PA的記憶行為表現為電路中電容/電感元件的頻率敏感性引入的AM/PM失真,在窄帶通信情況下,電容/電感元件的頻率敏感性會大大降低,PA的行為模型可近似采用無記憶行為模型等效。常用的無記憶行為模型有Saleh模型[68]、Rapp模型[69]、Ghorbani模型[70]、冪級數模型[71]等。而對于寬帶通信系統或者多載波通信系統(4G/5G等),常用的有記憶行為模型為Volterra級數模型[72]、Wiener模型[73]、Hammerstein模型[74]、Wiener-Hammerstein模型[75]、并聯Hammerstein模型[73]、并聯Wiener模型[76]、神經網絡模型[77]等。相較于其他有記憶模型,Volterra級數模型可以方便地將PA的非線性和記憶特性結合在一起,能夠精準地對PA進行建模,但是隨著非線性階次及記憶深度的增加,需要計算的參數量也會迅速增加[66],很難直接用于高階有記憶的DPD的設計中,在大多數設計中通常均采用簡化后的基于Volterra級數模型的記憶多項式模型[64–67,78–86]對PA進行近似建模。

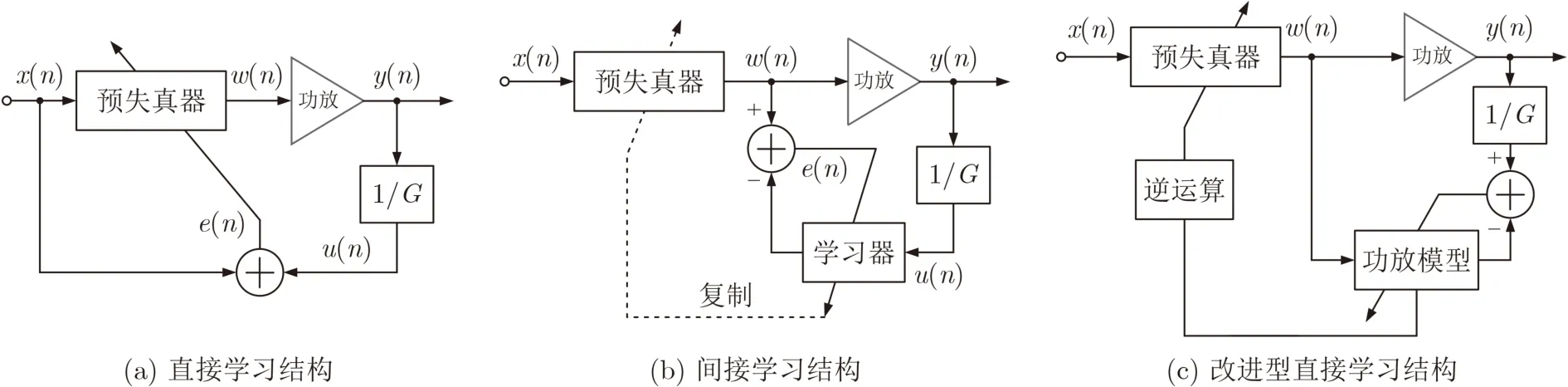

DPD的學習結構包括直接學習結構[83,84,86]、間接學習結構[80,86]、改進型直接學習結構[64]3種,如圖8所示,直接學習結構通過求取功放的前逆對PA的非線性進行補償,但由于預失真器的輸出直接影響PA的輸出,因此是一個閉環反饋系統,存在穩定性問題。如果采用的DPD參數辨識方法不收斂或者遇到外界干擾,可能導致系統的非正常工作。而間接學習結構通過增加一個學習器求取PA的后逆,再將通過辨識算法計算出的后逆參數送至預失真器來補償PA的非線性,學習過程開環化,避免了穩定性問題,間接學習結構對于大部分PA均是成立的,目前的商用化數字預失真器中大多采用此類結構,但是對于部分較復雜的PA模型,其后逆與前逆并不一定相等,因此會引入部分補償誤差,同時PA中產生的噪聲也會導致學習器的收斂值部分偏離預期[87]。而改進型直接學習結構兼顧直接學習結構和間接學習結構的優點,首先求取PA模型,再通過求逆運算將預失真器等效為PA的前逆,但是求逆計算量往往較大。

典型的DPD參數的辨識方法包括LMS算法[64]和遞歸最小二乘(Recursive Least Squares, RLS)算法[80,85]兩種,由于LMS算法涉及期望值的求解,因此要求輸入的信號必須具備廣義平穩特性,而RLS算法則無此要求,且RLS收斂速度快,不存在穩態誤差,辨識性能更高。但是由于涉及矩陣乘法及向量除法運算,消耗的資源量是非常巨大的,目前工程實現中多數仍采用LMS算法。

DPD補償模塊模型,即圖8中的預失真器模型,包括查找表結構和矩陣多項式結構[66,80,85]兩種,查找表結構又包括映射查找表[88,89]、復增益查找表[90]以及極坐標查找表結構[91],其中映射查找表的補償速度最快,且需要的資源量最小,但是其通常適用于無記憶PA模型,無法校準PA的AM/PM失真[89]。根據PA是否采用記憶模型,復增益查找表還可分為無記憶查找表[64,65]和有記憶查找表[70]兩類。查找表結構是一種靜態DPD機制,通常在上電復位后完成校準并將補償參數寫入查找表。而矩陣多項式結構是一種動態DPD機制,可以根據實時的輸入與輸出信號動態調整預失真器內的矩陣多項式參數值,跟蹤性能優良,但是消耗的計算資源、補償時長、功耗等均較高。

圖8 DPD學習結構

目前對DPD技術的研究主要集中在上述4個方面,近年來多數的創新性成果大多是對具體的電路結構及應用場景進行優化設計,例如,傳統的DPD反饋鏈路需要I/Q兩個支路同時存在,且由于PA的非線性效應,反饋支路ADC的采樣率需要達到輸入信號帶寬的5倍以上才能準確預估PA的前逆或者后逆模型[78],需要的硬件開銷及功耗均較大,文獻[79,80]分別提出了基于單支路硬件架構[79]以及欠采樣條件下[80]的DPD補償電路模型,大大簡化了電路設計的復雜度。同時,相控陣[81,82]以及多載波應用場景(4G/5G)[64,83]條件下的DPD補償技術也逐漸成熟化。

3 頻率綜合器校準技術

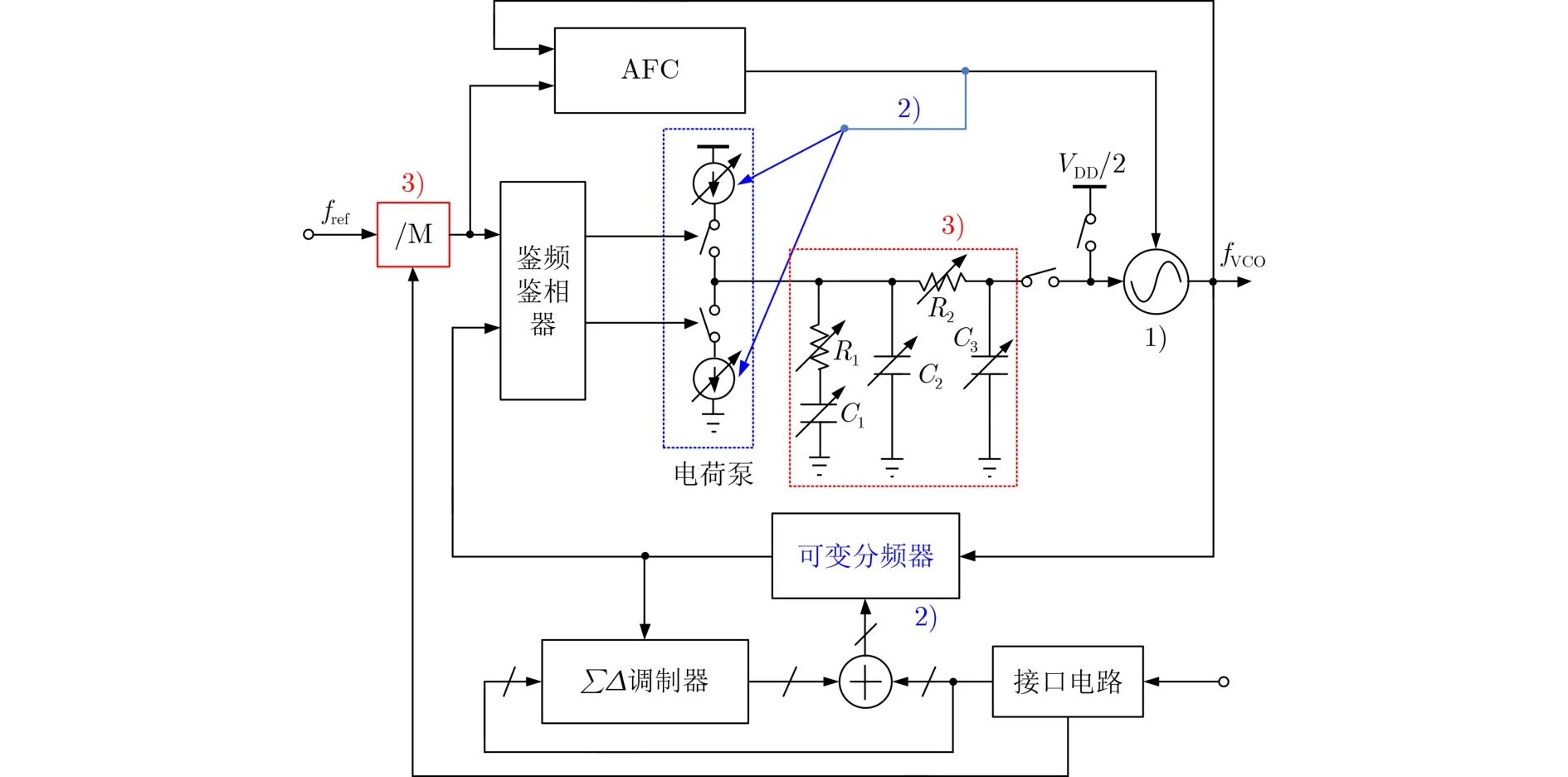

在實際的工程實現中,VCO振蕩頻率的PVT相關性會導致設計的振蕩頻率偏離10%~15%,因此為了覆蓋所需的頻點,頻率綜合器的設計通常都是具有一定輸出頻率范圍的寬帶電路,對于軟件定義無線電等寬帶應用場景更是如此。這就要求頻率綜合器在設計過程中需要在兩個方面特別注意[4]:一是必須增加必要的自動頻率校準(Automatic Frequency Calibration, AFC)功能,射頻收發機中的VCO一般采用LC負阻結構,金屬-絕緣體-金屬(Metal-Insulator-Metal, MIM)電容網絡實現輸出頻率的粗掃描,可變電容提供輸出頻率的精確鎖定,粗掃描過程是由AFC模塊來完成的,精確鎖定通過鎖相環來實現;二是必須提供穩定性校準功能,寬帶頻率綜合器中的分頻器通常會設計為小數分頻結構,為了抑制SD調制器引入的高頻噪聲,鎖相環通常采用4階II型結構,當確定了鎖相環的環路帶寬后,無源濾波器的參數值決定了環路的穩定性,在寬帶頻率綜合器中,輸出頻率以及輸入參考頻率的改變會改變環路帶寬的值,同時隨著頻率的改變,VCO的電壓-頻率KVCO也會發生變化,對環路帶寬同樣也會造成明顯的影響,惡化環路的相位裕量,甚至有可能出現自激的情況。

3.1 自動頻率校準

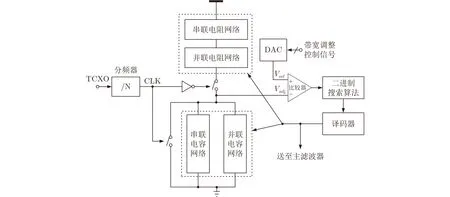

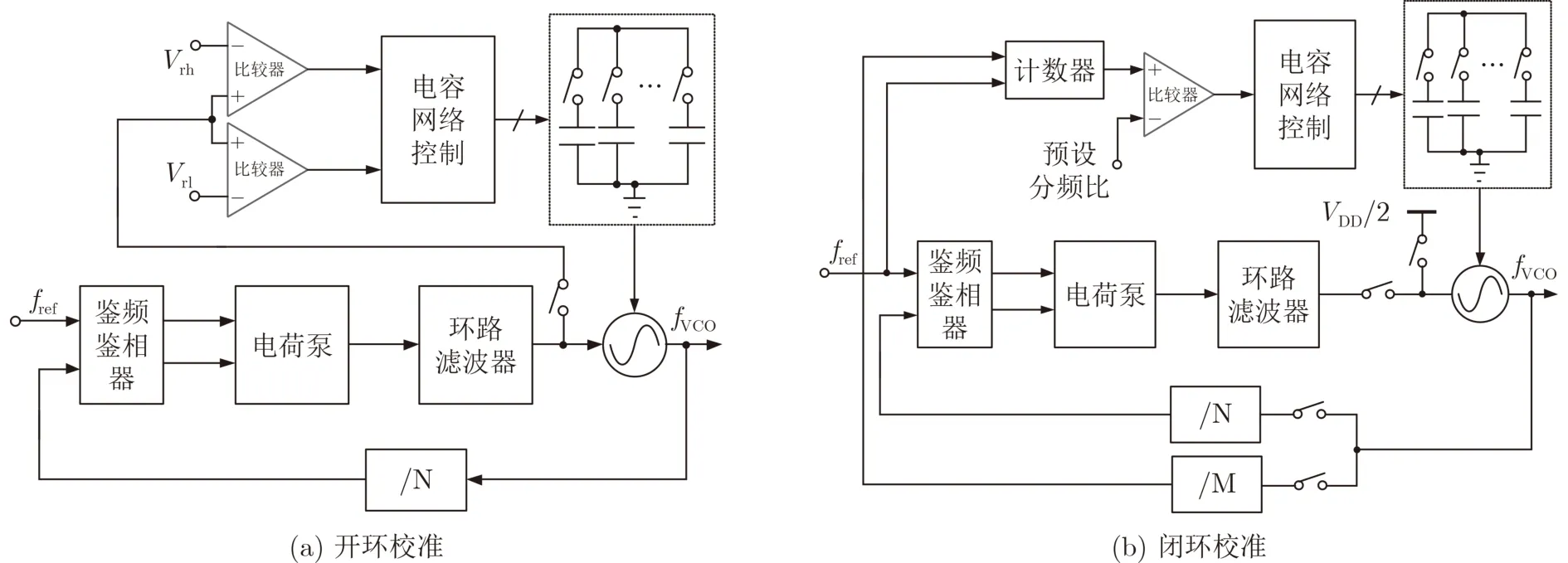

AFC分為開環AFC和閉環AFC兩種[92],如圖9所示,開環AFC的鎖定標記為VCO的控制電壓位于兩個參考電壓Vrh和Vrl之間,其鎖定速度較快,無須搜索完電容陣列的所有編碼,僅以電壓范圍作為判決標準,但是開環結構容易受工藝及溫度偏差的影響,不易鎖定最優頻率調諧線。閉環結構中,VCO的時鐘頻率對分頻后的參考時鐘高電平周期進行計數,隨著MIM電容網絡控制字的變化,VCO的輸出振蕩頻率也變化,根據計數值與預設分頻比的對比結果調整二進制搜索算法的搜索方向,并最終確定MIM電容網絡的控制字。閉環結構中的計數器類型有單相(計數誤差為1)[93]、雙相(計數誤差為1/2)[94]以及四相(計數誤差為1/4)[92,95]等,其校準精度依次提升,但是所需要的計數器也會逐漸增多,電路設計復雜度及功耗相應增加。在上述基礎上,文獻[92,94,95]通過引入最小誤差寄存比較模塊使AFC的最終校準結果始終落在最優點所在的調諧曲線上,進一步加快了鎖相環的鎖定速度,同時增加了對PVT變化的魯棒性。

圖9 AFC校準方法

為了在減少計數器的情況下進一步提升AFC的鎖定精度,文獻[21]提出了一種僅需1個計數器的帶有小數誤差補償邏輯的八相計數器,在減小電路設計復雜度的情況下將計數誤差減小至1/8。為了進一步提高計數精度,在同樣只需要1個計數器的情況下,文獻[96]提出了一種基于TDC結構的小數誤差補償邏輯,可以將計數誤差減小至任意范圍之內,但是精度越高,TDC中所需的反相器和觸發器也會越多,需要折中考慮。為了加快AFC的鎖定速度,文獻[97]提出了一種首先預存各頻率調諧曲線對應的分頻比的快速鎖定方案,大大加快了AFC的鎖定速度,但是此方法要求輸入的參考頻率是固定的,不適用于軟件定義無線電場景。上述校準方法的校準時序均受控于輸入參考頻率,文獻[98]提出了一種校準時序受控于VCO輸出頻率的校準方法,并采用計數誤差自適應的方式盡可能在VCO高頻情況下完成AFC過程,在沒有增加復雜度的情況下大大減小了鎖定時間。

對于包含多個VCO的頻率綜合器而言[94],在進行AFC鎖定之前,首先需要確定選擇哪一個合適的VCO,VCO的選擇依賴頻率綜合器輸出頻率的大小。

3.2 穩定性校準

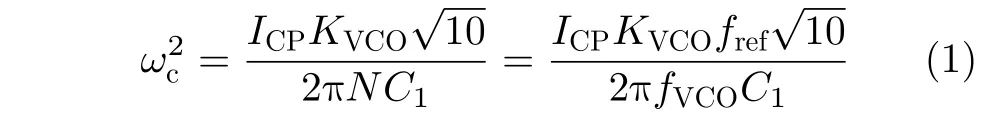

頻率綜合器環路穩定性的維持需要在完成穩定性預設計后保證環路帶寬的恒定性,以4階II型頻率綜合器為例,如圖10所示,其環路帶寬的表達式為[4]

其中,ICP為電荷泵的充放電電流,N為頻率綜合器的分頻比,C1為環路濾波器的第1級電容值。因此如何維持上述參數之間的平衡性是穩定性校準需要解決的問題。

由于KVCO與輸出頻率的3次方成正比[4],為了避免KVCO的較大波動對環路穩定性造成影響,首先需要將KVCO恒定化,典型的做法有可變電容串聯補償方法[99]、分段補償法[100]、溫度計編碼補償法[101]等。完成KVCO的補償后,通過電荷泵充放電電流ICP的可配置化(AFC控制)補償分頻比N的變化從而保證環路的穩定性[101]。在軟件定義無線電應用場景中,需要兼容寬范圍的輸入參考頻率,在輸出頻率保持不變的情況下,輸入參考頻率的變化會導致分頻比N的變化,通常的做法是首先在最大輸入參考頻率的情況下按照上述步驟對環路進行補償,然后在此基礎上,通過將環路濾波器中的各無源器件參數值等比例可配置化來補償輸入參考頻率的變化[4]。相應的校準示意圖如圖10所示,校準過程可概括為:(1)KVCO恒定化;(2)可配置ICP補償分頻比N的變化;(3)通過可配置化輸入參考頻率分頻器和環路濾波器補償輸入參考頻率的變化。

圖10 頻率綜合器穩定型校準示意圖

上述校準過程可以支持非常寬的輸出頻率范圍及輸入參考頻率范圍,但是電路復雜性較高,根據式(1)右邊等式可知,環路帶寬的恒定性僅與輸出頻率的平方成正比,因此僅通過可配置化ICP對輸出頻率的變化進行補償也可以維持環路的穩定性[102]。但是此方法也面臨一個嚴重的問題:當輸入頻率范圍較寬時,低頻段的KVCO值會被壓縮得非常小,對工藝及溫度變化的魯棒性變差,極易導致失鎖問題。為了解決此問題,通常的做法是通過等比例改變VCO中的電感值集成多個VCO,保證KVCO變化處于可接受的范圍內[94]。

4 射頻集成電路多片同步校準技術

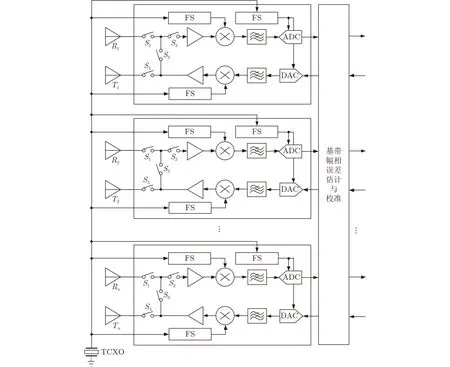

5G時代,相控陣、MIMO技術得到了大規模應用,致使多通道射頻收發集成電路逐漸出現,最典型的為ADI公司的2×2多通道RFIC—AD9361/AD9371/AD9375系列芯片以及4×4多通道RFIC—AD9026芯片。上述應用場景除了多通道需求外,還要求多通道射頻收發具備射頻同步性、基帶同步性以及多通道的幅相匹配性。

多通道射頻同步性主要依靠收發通道本振信號的相位同步性來保證,對于整數型頻率綜合器,只要能夠保證輸入參考頻率的一致性,多個頻率綜合器在鎖定后會自動保持一致。但是對于小數型頻率合成器,即使處于鎖定狀態,由于Σ?調制器的存在,無法保證可編程分頻器的分頻值順序是完全相同的,因此多個小數分頻器之間的相位是隨機的,需要在鎖定后重新復位Σ?調制器,使可編程分頻器的分頻值順序趨于一致,完成射頻同步[103]。基帶同步性主要是為了保證ADC和DAC的采樣時鐘是同步的,除了保證用于提供采樣時鐘的基帶頻率綜合器的輸出頻率同步性以外(與射頻同步相同),還必須在基帶頻率綜合器完成同步后復位后續的外部分頻器以保證采樣頻率的同步性,完成基帶同步[49]。

對于射頻通道的幅相匹配性,校準過程如下:首先在外部放置一個單音發射源,同時閉合開關S1和S2,選取任意接收通道為參考通道,剩余接收通道的輸出依次(或者同時)與該參考通道的輸出進行比較(相除),并將比較結果依次作為各對應接收通道的幅相補償值[104,105],具體工作原理如圖11所示。完成接收通道的校準后,可以將對應的系數寫入(上電置位)數字基帶處理模塊中,避免每次上電后均需要校準。發射通道的校準是在接收通道校準完成的基礎上通過回環的方式完成的(閉合S2和S3,斷開S1和S4),校準方式與接收通道類似,只是信號需要通過發射鏈路從基帶輸入[106]。為了避免溫度變化對幅相失配的影響,通常還需要在不同的溫度值下進行幅相失配校準并存儲校準系數,然后根據溫度傳感器選擇需要切換的補償系數。

圖11 多通道幅相校準圖

采用校準系數存儲的方案對各通道由于老化導致的失配較敏感,為了保證校準精度的實時性,接收通道幅相失配校準的信號源可以通過芯片內部的頻率綜合器提供,即接收通道校準時的輸入信號源可以由發射通道的射頻頻率綜合器提供(射頻同步完成后),這樣可以保證芯片在每次上電時都可以進行一次校準,保證校準的實時性。

5 結束語

射頻集成電路中的校準技術是高性能射頻集成電路設計必須要克服的關鍵技術,這些校準技術種類繁多,實現復雜,且需要通過嚴格的狀態控制逐一完成,是一項高難度的系統性工程。文中所述的校準技術是目前應用最廣泛、效果最明顯的10個核心校準技術,涉及射頻收發鏈路、頻率綜合器、多片同步等3大方向,并且較全地給出了目前各類典型的校準算法,為高性能射頻集成電路的設計打下了良好的基礎。

前述的綜述部分主要針對模擬域的收發架構進行了校準技術的歸納,由于工藝移植的便捷性、較強的抗干擾性以及對工藝溫度偏差的極高魯棒性,數字化技術逐漸成為射頻集成電路設計中的一個重要發展趨勢,下面簡要從數字化的角度進行相關校準技術的綜述。

(1)射頻收發鏈路:射頻收發鏈路的數字化可以很大程度上避免多數校準技術的使用,例如DCOC、偶次非線性失真、I/Q失配校準、諧波抑制技術、濾波器帶寬校準以及本振泄露校準等,但是對于接收鏈路而言,目前數字化技術的主要矛盾還是集中在高精度高采樣速率ADC的研究上,針對某些專用應用場景,射頻接收鏈路的數字化具備較大的實現可能性,但是在大多數應用場景中,尤其是軟件定義無線電應用場景,短期內并不能取得較明顯的突破,可以肯定的是,零中頻架構和低中頻架構仍會在射頻接收鏈路的設計實現中占據可觀的時間長度,上述校準技術仍是高性能接收電路設計所必需的。發射鏈路的數字化目前已經取得了非常明顯的進步,典型的數字化發射架構包括數字極化發射機[107–109]、數字正交發射機以及數字LINC發射機[108],內置的數字化PA包括數字Doherty PA[62]、數字化Class-D PA[107]、數字化Class-G PA[59,60]、LINC class-E PA[110]等。但是數字化發射機內部的工作時鐘通常處于過采樣狀態,對于高碼速率通信系統而言消耗的功耗較高。如果采用極化發射架構,還需內置數字相位插值器[111],該插值器的固有延遲對工藝/溫度變化同樣敏感,極易惡化PA的頻譜性能。另外,極化/LINC架構中內置的Cordic算法本身固有的非線性會進一步拓展幅度支路和相位支路的帶寬,對芯片內部的工作時鐘要求更高。同時,正交架構和LINC架構還需額外增加一個數字PA來實現相應的電路功能[108],在發射功率較大時,功耗會明顯上升。

但是,無論是采用模擬架構還是數字架構,對于發射鏈路而言,PA的DPD補償在調制信號的峰均比較高的情況下仍是確保高性能發射的必需手段。

(2)頻率綜合器:全數字頻率綜合器(All Digital Frequency Synthesizer, ADFS)最早是2003年由TI公司的Staszewski等人[112]提出并設計實現的,采用計數器和TDC結構替換模擬域的PFD+CP結構,數字濾波器替換環路濾波器等實現頻率綜合器的數字化,根據計數器位置的不同,可分為鎖相或者鎖頻型數字頻率綜合器。數字頻率綜合器中不存在模擬域中PFD+CP和環路濾波器引入的相位噪聲,但是各模塊卻增加了量化噪聲,并且異步時鐘(LO時鐘和輸入參考時鐘)的同步操作還會引入不可避免的亞穩態現象。其校準仍分為AFC和穩定性校準兩部分[113],AFC部分的校準相較于模擬域電路而言,更加復雜,為了避免VCO中電容陣列過大,AFC過程共包括3部分:粗精度AFC、中等精度AFC以及高精度AFC,通過對濾波后的數字相位誤差進行判決實現三者之間的串行切換。ADFS同樣也存在穩定性的問題,但是ADFS中不存在電荷泵、分頻器等模擬模塊,因此穩定性僅受數控振蕩器(Digital Controlled Oscillator, DCO)增益KDCO的影響,DFS的穩定性校準通常是通過對DCO模塊進行增益歸一化實現的[113]。

(3)多片同步校準:由于ADFS是通過TDC產生相位/頻率誤差的小數部分,因此不存在Σ?調制器產生的隨機分頻現象,鎖定后ADFS即實現輸出頻率的相位同步,同時發射鏈路的數字化也無需進行多通道發射鏈路的幅相失配校準。