基于三維線性反饋移位寄存器的三維堆疊集成電路可重構(gòu)測(cè)試方案

陳田,魯建勇,劉軍,梁華國,魯迎春

(1.合肥工業(yè)大學(xué) 計(jì)算機(jī)與信息學(xué)院,合肥 230601;2.情感計(jì)算與先進(jìn)智能機(jī)器安徽省重點(diǎn)實(shí)驗(yàn)室(合肥工業(yè)大學(xué)),合肥 230601;3.合肥工業(yè)大學(xué) 微電子學(xué)院,合肥 230601)

0 引言

傳統(tǒng)二維集成電路(Two-Dimensional Integrated Circuit,2D IC)的發(fā)展速度已經(jīng)變慢,而高密度垂直互連的三維集成架構(gòu)是目前作為延續(xù)摩爾定律的替代方案之一。三維集成技術(shù)包括在三個(gè)維度上互連的集成電路[1],這種從水平互連到垂直互連的轉(zhuǎn)換在信號(hào)傳輸速度和提升集成電路的(Integrated Circuit,IC)整體性能上非常有前景。利用過硅通孔(Through Silicon Vias,TSV)作為中間介質(zhì)的三維堆疊技術(shù)也是三維集成技術(shù)的一種,該技術(shù)的特點(diǎn)是能夠減少裸片間的互連長度,降低功耗以及增加帶寬等,相較于2D IC,提高了集成電路性能[2-4]。但更高的性能也對(duì)集成電路測(cè)試技術(shù)提出更高的要求,而在三維芯片生產(chǎn)成本中,測(cè)試成本占據(jù)了48%[5],本文的主要目標(biāo)是降低測(cè)試成本。

相較于2D IC,三維堆疊集成電路(Three-Dimensional Stacked Integrated Circuit,3D SIC)的測(cè)試流程更復(fù)雜,在每次堆疊后都要進(jìn)行一次測(cè)試,一共經(jīng)歷綁定前、綁定中和綁定后測(cè)試三個(gè)階段[6-7],以確保良率。復(fù)雜的測(cè)試流程容易出現(xiàn)冗余的測(cè)試資源與較大的測(cè)試時(shí)間開銷。測(cè)試時(shí)間會(huì)影響芯片的生產(chǎn)周期,而測(cè)試結(jié)構(gòu)的硅面積開銷是重要的測(cè)試資源,一顆芯片上的可用測(cè)試面積有限。如何利用各個(gè)階段的測(cè)試資源并降低測(cè)試時(shí)間,是降低測(cè)試成本的重要方向。

在集成電路測(cè)試技術(shù)中,內(nèi)建自測(cè)試(Built-In Self-Test,BIST)是在電路中植入相關(guān)的功能電路以實(shí)現(xiàn)待測(cè)電路自我測(cè)試功能的技術(shù),一般由測(cè)試模式生成器、響應(yīng)分析器和BIST 控制器組成[8]。線性反饋移位寄存器(Linear Feedback Shift Register,LFSR)作為測(cè)試模式生成器,結(jié)構(gòu)簡單,能夠以較小的測(cè)試數(shù)據(jù)存儲(chǔ)量生成所需的測(cè)試模式,同樣適用于3D SIC;但LFSR 生成的測(cè)試模式具有偽隨機(jī)特性,測(cè)試功耗較高,如何降低測(cè)試功耗,是降低測(cè)試成本的重要方向。

測(cè)試結(jié)構(gòu)的硅面積開銷、測(cè)試功耗以及測(cè)試時(shí)間開銷都是測(cè)試成本的重要組成部分,本文基于LFSR 構(gòu)建了一種可重構(gòu)的三維LFSR(Three-Dimensional LFSR,3D-LFSR)測(cè)試結(jié)構(gòu),適用于3D SIC 的不同測(cè)試階段,以降低測(cè)試成本。

本文的主要工作如下:1)設(shè)計(jì)了一種3D SIC 測(cè)試中的低功耗測(cè)試結(jié)構(gòu),以降低測(cè)試功耗;2)設(shè)計(jì)了一種適用于不同測(cè)試階段的可重構(gòu)3D-LFSR 測(cè)試結(jié)構(gòu),能夠充分復(fù)用不同階段的測(cè)試資源,以降低測(cè)試結(jié)構(gòu)的硅面積開銷;3)對(duì)測(cè)試數(shù)據(jù)進(jìn)行了測(cè)試前處理,采用串并行混合測(cè)試模式降低測(cè)試時(shí)間。

1 相關(guān)工作

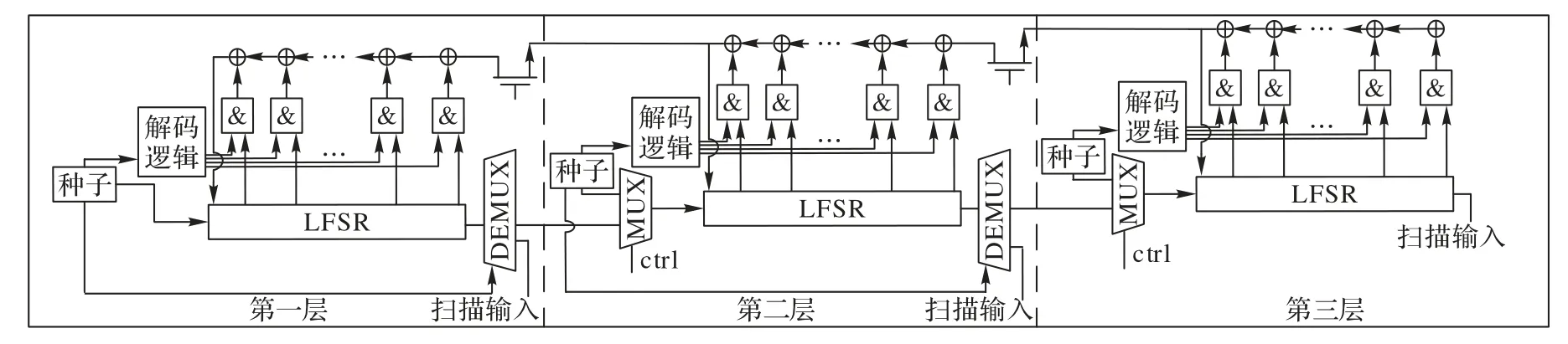

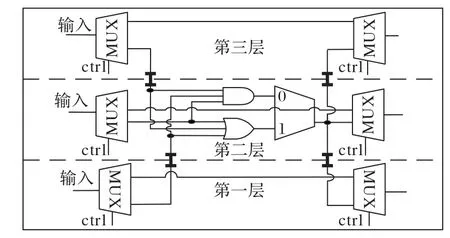

BIST 對(duì)偽隨機(jī)生成器LFSR 生成測(cè)試模式的故障覆蓋率要求較高,因此使用重新設(shè)定種子的技術(shù)[9-10]以提升故障覆蓋率。如圖1 為BIST 下多重多項(xiàng)式LFSR 的結(jié)構(gòu),通過與門和解碼邏輯電路能夠更改反饋系數(shù),即更改多項(xiàng)式,達(dá)到提升故障覆蓋率的目的。本文基于多重多項(xiàng)式的LFSR,利用了可變多項(xiàng)式的特性,連接多層LFSR 以形成級(jí)數(shù)更大的LFSR 結(jié)構(gòu),能夠滿足綁定后形成更大的測(cè)試電路的需求。

圖1 多重多項(xiàng)式LFSR結(jié)構(gòu)Fig.1 Structure of multiple-polynomial LFSR

2D IC 測(cè)試通常只需經(jīng)歷晶圓測(cè)試和最終測(cè)試。晶圓測(cè)試在組裝和封裝前篩選出有缺陷的集成電路,防止不必要的封裝成本;而最終測(cè)試則保證封裝芯片的質(zhì)量,以減少測(cè)試逃逸。但對(duì)于3D SIC,需要定義其他測(cè)試,例如部分堆疊后的測(cè)試。3D SIC 測(cè)試需要經(jīng)歷綁定前、綁定中和綁定后測(cè)試[6-7]:綁定前是為了可以測(cè)試芯片的傳統(tǒng)功能,也可以應(yīng)用于初步的TSV 測(cè)試;綁定中和綁定后則是在堆疊后,確認(rèn)堆疊過程中芯片的完好性。復(fù)雜的測(cè)試流程對(duì)控制測(cè)試成本的要求更高。如何在各個(gè)測(cè)試階段充分利用測(cè)試資源,是降低測(cè)試成本的關(guān)鍵因素。

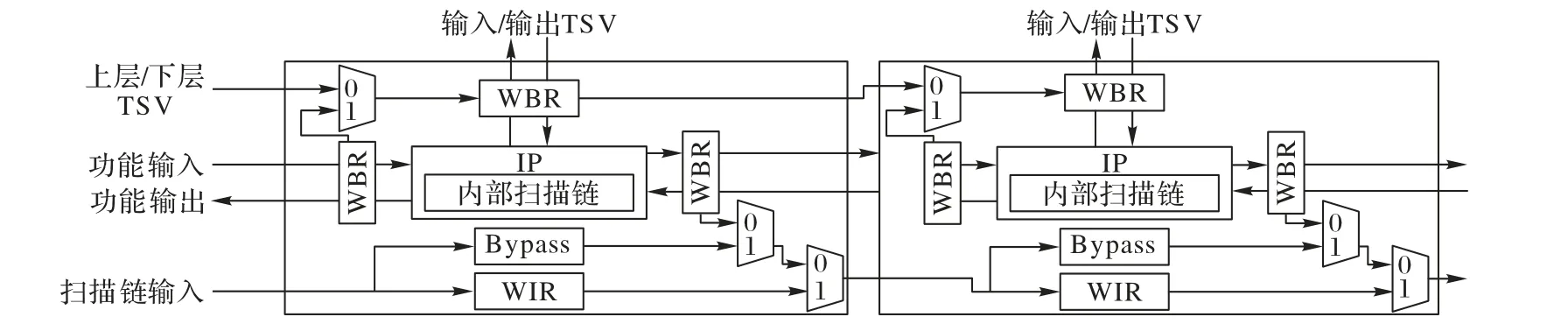

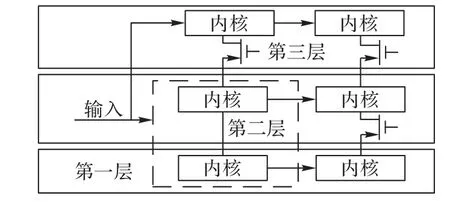

文獻(xiàn)[11]中指出,三維集成電路的測(cè)試技術(shù)和可測(cè)試性設(shè)計(jì)(Design For Testability,DFT)仍是3D 技術(shù)成功的關(guān)鍵。目前嵌入式內(nèi)核的測(cè)試wrapper 已經(jīng)由電氣與電子工程師協(xié)會(huì)(Institute of Electrical and Electronics Engineers,IEEE)進(jìn)行了標(biāo)準(zhǔn)化,該標(biāo)準(zhǔn)稱為IEEE Std1500[11-12],在此基礎(chǔ)上,IEEE制定的Std P1838標(biāo)準(zhǔn)[13-14]廣泛用于3D 堆疊芯片。圖2 為IEEE Std P1838 標(biāo)準(zhǔn)結(jié)構(gòu)圖[15],一層內(nèi) 有兩個(gè) 知識(shí)產(chǎn) 權(quán)(Intellectual Property,IP)核,測(cè)試外殼指令寄存器(Wrapper Instruction Register,WIR)用于封裝測(cè)試指令的譯碼器和控制器,控制各個(gè)IP 核的狀態(tài)轉(zhuǎn)換,進(jìn)行測(cè)試模式的選擇和切換。WIR 除了在IP 核的輸入輸出處添加,也在TSV 的兩端添加,以保證層間的IP 核狀態(tài)的可控性和可觀性。測(cè)試外殼旁路寄存器(Wrapper Bypass Register,WBR)由多個(gè)可掃描的觸發(fā)單元組成,每個(gè)單元由一個(gè)D 觸發(fā)器和兩個(gè)數(shù)據(jù)選擇器組成,多個(gè)觸發(fā)單元連接起來就類似于掃描鏈。內(nèi)部測(cè)試模式連接WBR 與內(nèi)部掃描鏈進(jìn)行使用。外部測(cè)試模式則單獨(dú)使用WBR。為了解決層間和層內(nèi)內(nèi)核之間穿行和并行測(cè)試之間的轉(zhuǎn)換,在該結(jié)構(gòu)的基礎(chǔ)上,本文設(shè)計(jì)了不同層的核間并行和串行測(cè)試,增加少量電路以構(gòu)建低功耗路由模塊,同時(shí)減少了測(cè)試時(shí)間和功耗。

圖2 IEEE std P1838標(biāo)準(zhǔn)結(jié)構(gòu)Fig.2 IEEE std P1838 standard structure

2 本文方案

2.1 整體結(jié)構(gòu)

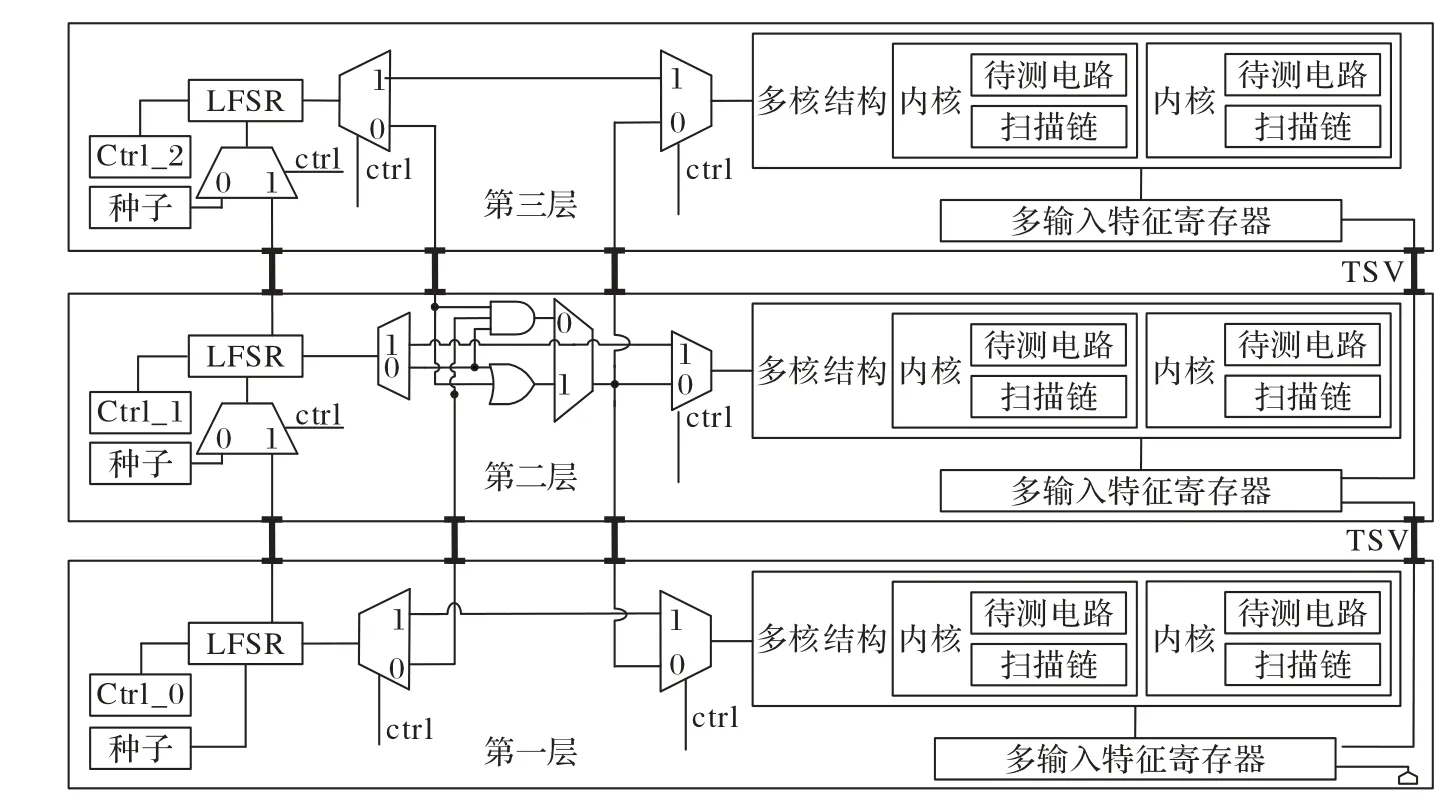

本文方案的總體片上測(cè)試結(jié)構(gòu)如圖3 所示,主要由3DLFSR、低功耗路由結(jié)構(gòu)、核間互連結(jié)構(gòu)組成。3D-LFSR 復(fù)用了綁定前的LFSR,能夠在較低測(cè)試面積和存儲(chǔ)開銷的情況下生成測(cè)試模式;低功耗路由結(jié)構(gòu)負(fù)責(zé)將測(cè)試模式轉(zhuǎn)換為低功耗的測(cè)試模式;核間互連結(jié)構(gòu)則能很好地完成各個(gè)內(nèi)核的并行或串行測(cè)試。

圖3 本文方案的總體測(cè)試結(jié)構(gòu)Fig.3 Overall test structure of proposed scheme

2.2 3D-LFSR結(jié)構(gòu)

重構(gòu)后的3D-LFSR 如圖4 所示,每層的測(cè)試模式生成器包括可更換多項(xiàng)式的LFSR、解碼邏輯、控制重構(gòu)的多路復(fù)用器和多路分配器。多項(xiàng)式的更換是通過與門更改LFSR 的抽頭位置(tap locations),與門的選擇需綜合考慮測(cè)試面積。多重多項(xiàng)式的LFSR 能夠提高測(cè)試集編碼的成功率。但在三維堆疊集成電路中,若綁定后的LFSR 形成了更大的待測(cè)試電路,此時(shí)單層的測(cè)試模式生成器無法滿足測(cè)試需求;若在單層設(shè)計(jì)更大的測(cè)試模式生成器,在非綁定后測(cè)試階段,測(cè)試資源會(huì)被閑置。本文提出綁定后重構(gòu)LFSR 以解決該問題。

圖4 3D-LFSR結(jié)構(gòu)Fig.4 3D-LFSR structure

各層獨(dú)立的LFSR 通過層間TSV 連接,然后通過附加的多路選擇器和多路分配器選擇性地決定是否連接LFSR,以組成一個(gè)更大的LFSR。本文構(gòu)建的是三層的3D SIC。當(dāng)對(duì)整體測(cè)試時(shí),各層的LFSR 會(huì)連接起來。第二層的LFSR 通過使用多路復(fù)用器對(duì)連接后的LFSR 進(jìn)行拆分,最終形成兩個(gè)LFSR:主LFSR 用于生成待測(cè)電路所需的測(cè)試模式,次LFSR則用于輔助最終生成低功耗測(cè)試模式。LFSR 的拆分點(diǎn)根據(jù)測(cè)試集能夠求得的種子的最小級(jí)數(shù)來拆分。

綁定前測(cè)試:測(cè)試模式被編碼成由一個(gè)多項(xiàng)式標(biāo)識(shí)符、1-2 多路分配器的控制信號(hào)以及各自多項(xiàng)式的種子組成的輸入模式。本文將編碼后的數(shù)據(jù)仍然統(tǒng)稱為種子。在測(cè)試模式下,建立與多項(xiàng)式標(biāo)識(shí)符、控制信號(hào)的反饋鏈路,將種子加載到LFSR 中,經(jīng)過移位轉(zhuǎn)換后,生成與原有種子相容的測(cè)試模式,最后通過低功耗路由模塊加載到掃描鏈中。

綁定后測(cè)試:綁定后形成了一個(gè)更大的功能電路,如果進(jìn)行總體結(jié)構(gòu)測(cè)試,所需的LFSR 的級(jí)數(shù)更大,此時(shí)通過控制1-2 多路分配器和2-1 多路選擇器的輸出端,連接相鄰層的LFSR,以形成一個(gè)更大的LFSR。通過更換多項(xiàng)式,進(jìn)行重新編碼。

2.3 低功耗路由結(jié)構(gòu)

LFSR 作為測(cè)試模式生成器,能夠很好地對(duì)測(cè)試模式進(jìn)行編碼壓縮,但生成的二進(jìn)制測(cè)試序列具有偽隨機(jī)性,在測(cè)試模式下會(huì)產(chǎn)生高跳變活動(dòng),從而增加功耗。由于三維堆疊集成電路結(jié)構(gòu)的復(fù)雜性,這個(gè)問題變得更為突出。如圖5 所示,本文設(shè)計(jì)了低功耗路由模塊來降低測(cè)試功耗。

圖5 低功耗路由結(jié)構(gòu)Fig.5 Low-power routing structure

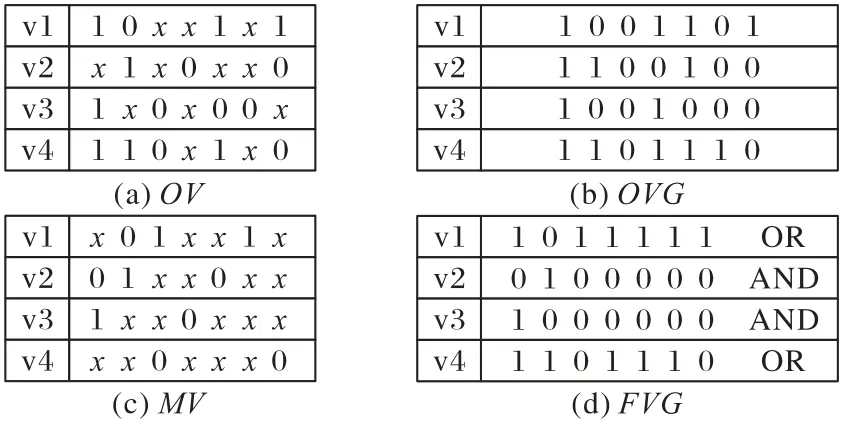

將主LFSR 和次LFSR 生成的測(cè)試模式經(jīng)過與門和或門電路,生成低功耗的測(cè)試模式后再路由到待測(cè)內(nèi)核的掃描鏈中。具體原理如下:如圖6(a)所示,原始測(cè)試集(OV)是帶有無關(guān)位的測(cè)試集,測(cè)試集中0 和1 表示確定位,x為無關(guān)位。對(duì)于測(cè)試模式中的無關(guān)位,如果能夠全部為0 或1,移位功耗會(huì)達(dá)到最低。OV在不經(jīng)過任何處理的情況下由主LFSR 生成不帶無關(guān)位的測(cè)試集(OVG),對(duì)應(yīng)圖6(b)。OV轉(zhuǎn)換后的測(cè)試集(MV)由次LFSR 生成,對(duì)應(yīng)圖6(c)。將OV和MV經(jīng)由主LFSR 產(chǎn)生的不帶x位的測(cè)試集(OVG,MVG)中對(duì)應(yīng)的測(cè)試模式進(jìn)行與/或運(yùn)算,生成最終送入掃描鏈中的低功耗測(cè)試集(FVG),對(duì)應(yīng)圖6(d)。

圖6 低功耗處理過程中產(chǎn)生的測(cè)試集Fig.6 Test sets generated during low-power processing

式(1)中k為測(cè)試模式的確定位中數(shù)目更大的一方;OVi是OV中的第i條測(cè)試模式;count0(OVi)是OV中第i條測(cè)試模式中確定位0 的數(shù)目;count1(OVi)是OV中第i條測(cè)試模式中確定位1 的數(shù)目。

式(2)中MVij是測(cè)試集MV的第i條測(cè)試模式中第j位的值;OVij是原始測(cè)試集OV的第i條測(cè)試模式中第j位的值;x是無關(guān)位為對(duì)k取非。OV根據(jù)式(2)后得到MV':

式(3)對(duì)MV'進(jìn)行無關(guān)位填充得到MV。對(duì)于LFSR 重播種,LFSR 級(jí)數(shù)的設(shè)定不小于Smax+4 時(shí)(Smax為測(cè)試集中最大確定位數(shù)目),LFSR 不能成功編碼的幾率小于10-6[16]。進(jìn)行無關(guān)位填充后,若確定位的數(shù)目大于測(cè)試集中最大確定位數(shù)目,會(huì)導(dǎo)致LFSR 級(jí)數(shù)增加以及種子的長度增加,即增加一定的面積開銷和測(cè)試數(shù)據(jù)存儲(chǔ)量。因此需要權(quán)衡存儲(chǔ)量和移位功耗,本文提出填充無關(guān)位后確定位的數(shù)目不大于原始測(cè)試集中的測(cè)試模式的最大確定位數(shù)目,在不增加面積開銷的前提下,仍可通過編程來調(diào)控存儲(chǔ)量和移位功耗,保證了方案的靈活性。

式(4)中OVG、ijMVGij是OV和MV的i條測(cè)試模式中第j位的值,為了使最終送入掃描鏈的測(cè)試模式的跳變數(shù)更低,將它們與測(cè)試集MV中第i條測(cè)試模式按位進(jìn)行與運(yùn)算,反之進(jìn)行或運(yùn)算,通過式(4)生成所需的低功耗測(cè)試集FVG。

2.4 核間互連結(jié)構(gòu)

在多核的3D SIC 中,除了考慮同一層中內(nèi)核之間的連接,還要考慮不同層的內(nèi)核之間的連接。如何使用一組接口訪問多層芯片并且能有效地輸入和輸出測(cè)試數(shù)據(jù),針對(duì)這個(gè)問題,提出了IEEE P1838 標(biāo)準(zhǔn)[15]。結(jié)合該標(biāo)準(zhǔn),本文的內(nèi)核間的互連結(jié)構(gòu)如圖7 所示,虛線框中是綁定后形成的更大的待測(cè)試電路。IEEE P1838 的標(biāo)準(zhǔn)結(jié)構(gòu)支持串行和并行兩種傳輸方式。串行測(cè)試為了節(jié)省測(cè)試帶寬,串聯(lián)所有IP 核,將測(cè)試數(shù)據(jù)依次輸入各個(gè)內(nèi)核,它的缺點(diǎn)是一次只能測(cè)一個(gè)內(nèi)核,其他的內(nèi)核則處于旁路狀態(tài)。并行測(cè)試能夠同時(shí)測(cè)試所有內(nèi)核以節(jié)省測(cè)試時(shí)間,但缺點(diǎn)是測(cè)試帶寬較大。

圖7 內(nèi)核間的互連結(jié)構(gòu)Fig.7 Interconnection structure between cores

如果在層內(nèi)采用并行測(cè)試,根據(jù)IEEE Std P1838 的控制邏輯,通過旁路寄存器將測(cè)試模式并行送入掃描鏈中;如果層與層之間的內(nèi)核間符合并行的測(cè)試模式,通過IEEE Std P1838 標(biāo)準(zhǔn)提供的層間掃描端口,將測(cè)試模式并行送到其他層。并行測(cè)試需要滿足測(cè)試帶寬和測(cè)試功耗的約束。對(duì)于內(nèi)核間的串行測(cè)試,IEEE Std P1838 標(biāo)準(zhǔn)提供了層間和層內(nèi)的串行接口,使兩內(nèi)核間的掃描鏈合并為一條以實(shí)現(xiàn)串行測(cè)試。在整個(gè)測(cè)試過程中,只采用串行測(cè)試會(huì)大幅度增加測(cè)試時(shí)間;只采用并行測(cè)試,內(nèi)核所用的測(cè)試模式也無法滿足帶寬和功耗的需求,采用多通道則會(huì)增加帶寬。串行和并行混合的測(cè)試方法將層間的MOS 管作為開關(guān)電路用于控制數(shù)據(jù)傳輸,能很好地均衡以上問題。在本文方案中,串行和并行的選擇根據(jù)測(cè)試數(shù)據(jù)壓縮算法來定,能夠合并的測(cè)試模式采用并行測(cè)試方法,否則采用串行的測(cè)試方法。

2.5 整體的信號(hào)控制

結(jié)合圖3 來看,每層用2 位的控制信號(hào)控制數(shù)據(jù)的輸入輸出選擇,第二層還需附加1 位對(duì)低功耗模塊的控制。對(duì)于1-2 多路分配器,控制信號(hào)為0 表示數(shù)據(jù)需要經(jīng)過低功耗模塊,即此時(shí)的數(shù)據(jù)滿足了低功耗測(cè)試生成所需的基本條件,可通過低功耗模塊降低移位功耗;控制信號(hào)為1 表示數(shù)據(jù)不經(jīng)過低功耗模塊直接到達(dá)后面的2-1 多路選擇器。對(duì)于靠近掃描鏈的2-1 多路選擇器,控制信號(hào)為0 表示將經(jīng)過低功耗模塊的數(shù)據(jù)輸入掃描鏈;控制信號(hào)為1 表示將未經(jīng)過低功耗模塊的數(shù)據(jù)輸入掃描鏈,也可以表示為不輸入數(shù)據(jù)到當(dāng)前層的掃描鏈中,這取決于當(dāng)前層的LFSR 是否輸出了測(cè)試數(shù)據(jù)。

總體的控制信號(hào)主要分為00、01、10 和11。控制信號(hào)00表示測(cè)試數(shù)據(jù)需要經(jīng)過低功耗模塊后傳輸?shù)剿鶎賹拥膾呙桄湥豢刂菩盘?hào)01 表示測(cè)試數(shù)據(jù)經(jīng)過低功耗模塊但不傳輸?shù)剿鶎賹拥膾呙桄湣?刂菩盘?hào)01 和10 發(fā)生的情況為:當(dāng)前測(cè)試數(shù)據(jù)所覆蓋的為多層邏輯待測(cè)電路時(shí),不屬于當(dāng)前待測(cè)電路層的LFSR 模塊作為次LFSR,控制信號(hào)設(shè)置為01;當(dāng)三層待測(cè)電路的測(cè)試模式相容且滿足測(cè)試模式生成的條件時(shí),若僅需兩層的測(cè)試模式便能達(dá)到所設(shè)的閾值,則無需使用另一層的LFSR 模塊,測(cè)試控制信號(hào)設(shè)置為10。

該結(jié)構(gòu)適用于三種測(cè)試模式的測(cè)試成本優(yōu)化:綁定前、綁定中和綁定后測(cè)試。在綁定前測(cè)試只需把控制信號(hào)設(shè)置為11,此時(shí)的測(cè)試邏輯電路與常規(guī)的基于LFSR 測(cè)試電路相同,由LFSR 輸出的測(cè)試模式直接輸入掃描鏈。對(duì)于當(dāng)前層有多個(gè)內(nèi)核的情況,掃描鏈中相容的測(cè)試數(shù)據(jù)可以并行測(cè)試,以減少測(cè)試時(shí)間。

綁定中和綁定后測(cè)試模式的實(shí)現(xiàn)過程基本一致。每層邏輯電路在堆疊后存在兩種情況:1)若當(dāng)前層的測(cè)試數(shù)據(jù)不與其他層的測(cè)試數(shù)據(jù)相容且不滿足低功耗測(cè)試模式的生成條件,當(dāng)前層進(jìn)行單獨(dú)測(cè)試,在不超過測(cè)試功率閾值的前提下,多層可以并發(fā)測(cè)試,減少了測(cè)試時(shí)間;2)當(dāng)前層的測(cè)試模式與其他層的測(cè)試模式相容且滿足低功耗測(cè)試模式的生成條件,多層LFSR 并行輸出測(cè)試模式到低功耗模塊中,然后并行輸出到對(duì)應(yīng)的測(cè)試掃描鏈中。

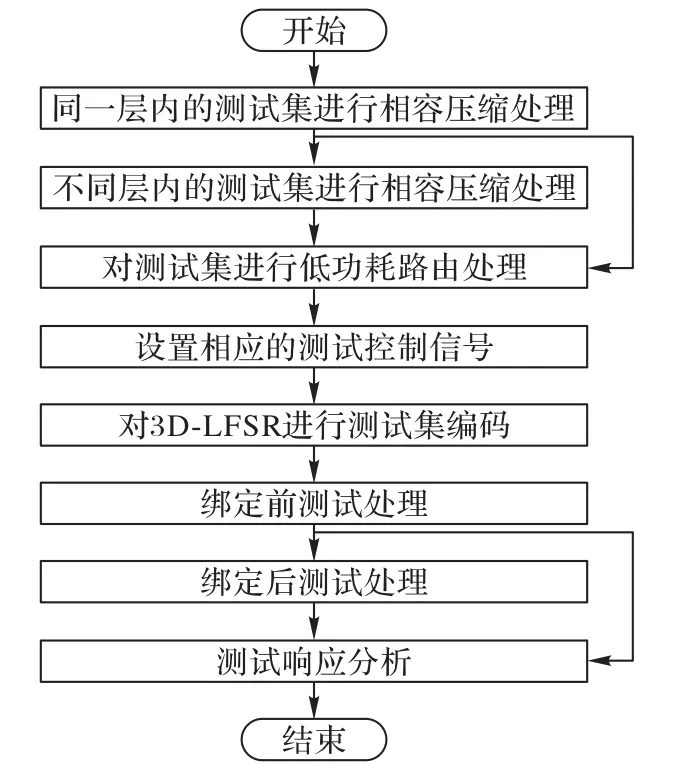

3 測(cè)試流程

三維芯片測(cè)試包含三種測(cè)試模式[8]:綁定前、綁定中和綁定后測(cè)試。三維芯片的輸入輸出引腳在最上層或最底層。本文中三維芯片的所有輸入輸出口均位于芯片底層,綁定后的測(cè)試模式均從底層向上傳輸,測(cè)試流程如圖8 所示。

圖8 本文方案的測(cè)試流程Fig.8 Testing process of proposed scheme

測(cè)試相容定義:如果兩個(gè)測(cè)試模式對(duì)應(yīng)位置的確定位相同或者其中一方為無關(guān)位,則這兩條測(cè)試模式相容。例如兩條測(cè)試模式V0=(a0,a1,…,am-1),V1=(b0,b1,…,bm-1),如果測(cè)試模式V0中的任何位置i(0 ≤i≤m-1)的值ai是0 或1,在測(cè)試模式V1的對(duì)應(yīng)位置bi是相同值或無關(guān)位,則稱測(cè)試模式V0和V1相容。

綁定前測(cè)試階段:根據(jù)測(cè)試數(shù)據(jù)相容壓縮原理,對(duì)同一層的所有內(nèi)核進(jìn)行測(cè)試集相容壓縮,設(shè)置相應(yīng)的路由控制信號(hào),實(shí)現(xiàn)對(duì)同一層內(nèi)的多個(gè)內(nèi)核同時(shí)測(cè)試,以降低測(cè)試時(shí)間。對(duì)相容壓縮后形成的更大的測(cè)試集進(jìn)行低功耗處理,再進(jìn)行LFSR 編碼,填充種子,進(jìn)行綁定前測(cè)試。

綁定后測(cè)試階段:將綁定前各層經(jīng)過處理后的測(cè)試集進(jìn)行相容測(cè)試壓縮,設(shè)置相應(yīng)的路由控制信號(hào),實(shí)現(xiàn)對(duì)多層的多個(gè)內(nèi)核同時(shí)測(cè)試,以降低測(cè)試時(shí)間。對(duì)相容壓縮后形成的更大的測(cè)試集進(jìn)行低功耗處理,再進(jìn)行3D-LFSR 編碼,填充種子,進(jìn)行綁定后測(cè)試。

無論是綁定前還是綁定后測(cè)試,LFSR 的級(jí)數(shù)不僅需要滿足綁定前的測(cè)試,也需要滿足綁定后的測(cè)試。具體的級(jí)數(shù)在測(cè)試前根據(jù)測(cè)試集編碼種子后再設(shè)置。

4 實(shí)驗(yàn)與結(jié)果分析

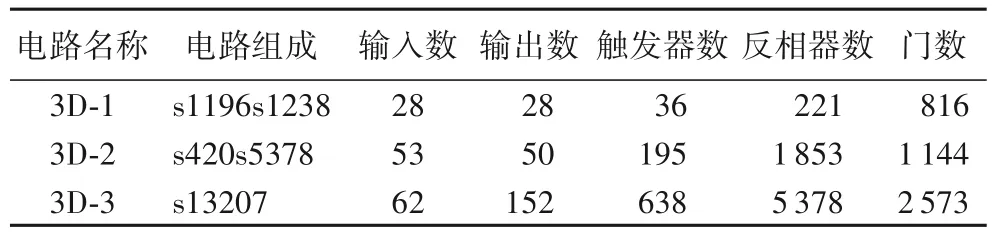

為了驗(yàn)證本文方案的有效性,采用ISCAS’89 基準(zhǔn)電路作為實(shí)驗(yàn)電路。采用的數(shù)據(jù)集為ATPG(Automatic Test Pattern Generation)工具生成的測(cè)試集。與3D-LFSR 結(jié)構(gòu)進(jìn)行對(duì)比的測(cè)試結(jié)構(gòu)來自文獻(xiàn)[17-18]。文獻(xiàn)[17]對(duì)雙LFSR測(cè)試結(jié)構(gòu)進(jìn)行優(yōu)化,以降低測(cè)試功耗。文獻(xiàn)[18]提出一種多模塊連接的LFSR 測(cè)試結(jié)構(gòu)Parallel-LFSR 以降低種子存儲(chǔ)量和硬件開銷。本文將文獻(xiàn)[17-18]中的LFSR 測(cè)試結(jié)構(gòu)在本文方案中的三維堆疊IC 結(jié)構(gòu)上進(jìn)行實(shí)驗(yàn),與3D-LFSR 結(jié)構(gòu)進(jìn)行對(duì)比。三維堆疊集成電路設(shè)置為三層,具體設(shè)置如表1所示。測(cè)試成本的組成主要有:測(cè)試數(shù)據(jù)壓縮、測(cè)試功耗、測(cè)試時(shí)間以及測(cè)試結(jié)構(gòu)面積開銷。

表1 實(shí)驗(yàn)電路參數(shù)Tab.1 Experimental circuit parameters

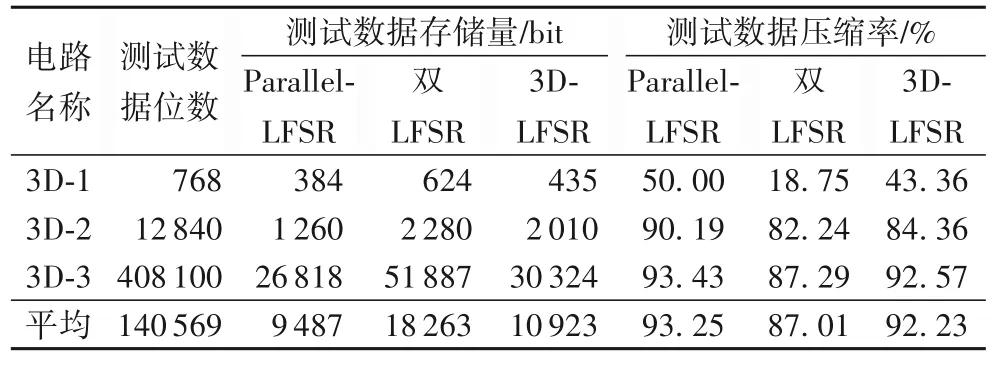

測(cè)試數(shù)據(jù)壓縮結(jié)果如表2 所示,主要由測(cè)試數(shù)據(jù)二進(jìn)制位數(shù)、測(cè)試數(shù)據(jù)存儲(chǔ)量以及測(cè)試數(shù)據(jù)壓縮率組成。相較于Parallel-LFSR,3D-LFSR 的平均測(cè)試數(shù)據(jù)存儲(chǔ)量增加了15.14%,平均測(cè)試數(shù)據(jù)壓縮率降低了1.09%。造成測(cè)試數(shù)據(jù)量增加以及測(cè)試數(shù)據(jù)壓縮率降低的主要原因是3D-LFSR中加入了低功耗路由模塊,增加了較多的控制信號(hào)。相較于雙LFSR,3D-LFSR 的平均測(cè)試數(shù)據(jù)存儲(chǔ)量降低40.19%,平均測(cè)試數(shù)據(jù)壓縮率提升了6.00%。可以看出,相較于雙LFSR,3D-LFSR 的測(cè)試數(shù)據(jù)壓縮效果明顯。

表2 測(cè)試數(shù)據(jù)壓縮實(shí)驗(yàn)結(jié)果Tab.2 Experiment results of test data compression

對(duì)于測(cè)試功耗,本文主要針對(duì)測(cè)試過程中的移位功耗。文獻(xiàn)[19]提出用測(cè)試模式在掃描單元中的翻轉(zhuǎn)次數(shù)度量移位功耗,稱為加權(quán)跳變度量(Weighted Transition Metric,WTM)。設(shè)Vi=(bi1,bi2,…,bil)是移入掃描鏈的第i條測(cè)試模式,WTM 定義如下:

有N條測(cè)試模式的測(cè)試集的峰值功耗如下:

平均移入功耗如式(7)所示:

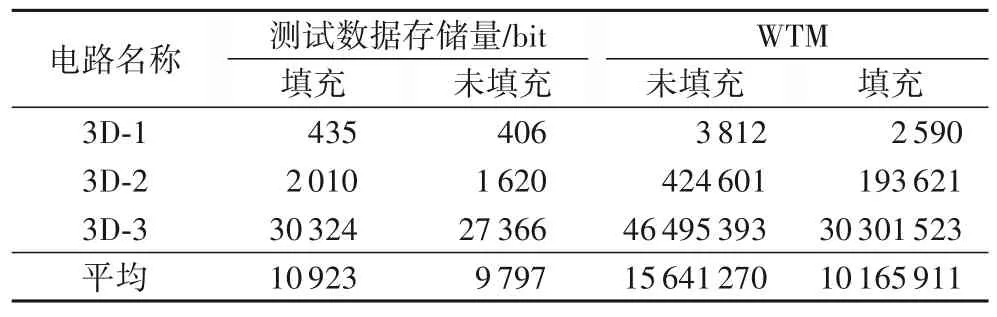

在測(cè)試集處理階段,在不增加面積開銷的前提下,無關(guān)位的填充能夠影響測(cè)試數(shù)據(jù)存儲(chǔ)量和測(cè)試功耗。表3 是測(cè)試集處理中是否進(jìn)行無關(guān)位填充的測(cè)試數(shù)據(jù)結(jié)果。本文的無關(guān)位填充指在不增加LFSR 級(jí)數(shù)的情況下進(jìn)行最大限度的填充。可以看到,填充后的平均測(cè)試數(shù)據(jù)存儲(chǔ)量相較于未填充的平均測(cè)試數(shù)據(jù)存儲(chǔ)量增加了11.49%。填充后的平均WTM 相較于未填充降低了35.00%。實(shí)驗(yàn)結(jié)果表明,在增加少量測(cè)試數(shù)據(jù)存儲(chǔ)量的情況下,相較于不填充無關(guān)位,無關(guān)位填充對(duì)測(cè)試功耗的改善更明顯,本文在與其他結(jié)構(gòu)的實(shí)驗(yàn)對(duì)比中,采用了填充無關(guān)位后的測(cè)試數(shù)據(jù)。

表3 無關(guān)位填充與未填充的對(duì)比結(jié)果Tab.3 Comparison results of filled and unfilled irrelevant bits

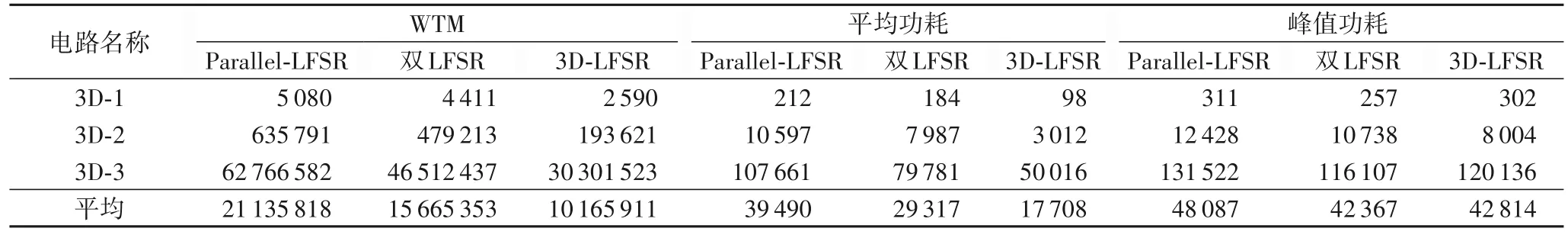

測(cè)試功耗結(jié)果如表4 所示。3D-LFSR 的WTM 和平均功耗均低于對(duì)比的測(cè)試結(jié)構(gòu)。相較于Parallel-LFSR 和雙LFSR,3D-LFSR 的平均WTM 分別降低了51.90%和35.11%;平均功耗分別降低了55.16%和39.60%。3D-LFSR 的峰值功耗略高于雙LFSR,而峰值功耗只要滿足低于電路可接受閾值即可。實(shí)驗(yàn)結(jié)果表明,3D-LFSR 結(jié)構(gòu)在降低測(cè)試功耗上效果明顯。

表4 測(cè)試功耗實(shí)驗(yàn)結(jié)果Tab.4 Experimental results of test power consumption

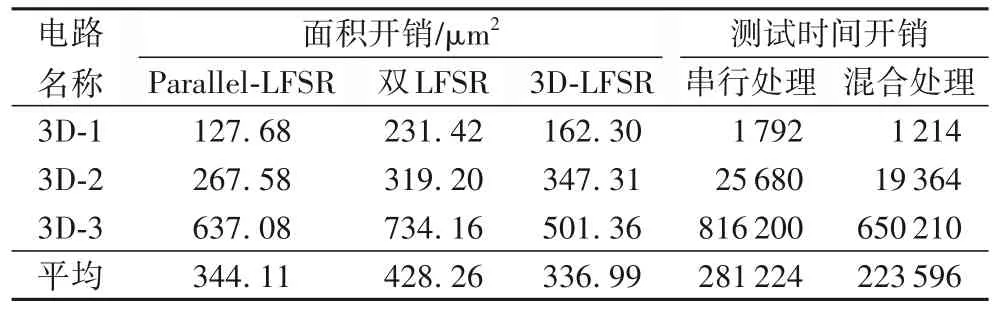

本文使用45 nm 標(biāo)準(zhǔn)庫計(jì)算面積開銷,通過計(jì)算測(cè)試模式在掃描鏈中的周期數(shù)以得到測(cè)試時(shí)間。本文中的面積開銷只考慮測(cè)試結(jié)構(gòu)的開銷,不考慮待測(cè)試電路以及核間標(biāo)準(zhǔn)結(jié)構(gòu)的面積開銷。如表5 所示,相較于Parallel-LFSR 和雙LFSR,3D-LFSR 的平均測(cè)試面積分別下降了2.07% 和21.31%。實(shí)驗(yàn)結(jié)果表明,重構(gòu)后的3D-LFSR 結(jié)構(gòu)在降低測(cè)試面積開銷上效果明顯。測(cè)試時(shí)間的對(duì)比主要針對(duì)混合測(cè)試和串行測(cè)試,為了不增加額外的測(cè)試帶寬,并不涉及完全并行測(cè)試的對(duì)比,在不增加的帶寬的前提下采用串行和并行的混合測(cè)試模式。實(shí)驗(yàn)結(jié)果表明,相較于串行測(cè)試,混合測(cè)試下的測(cè)試時(shí)間更短,平均測(cè)試時(shí)間減小了20.49%。

表5 測(cè)試面積與測(cè)試時(shí)間開銷Tab.5 Test area and test time overhead

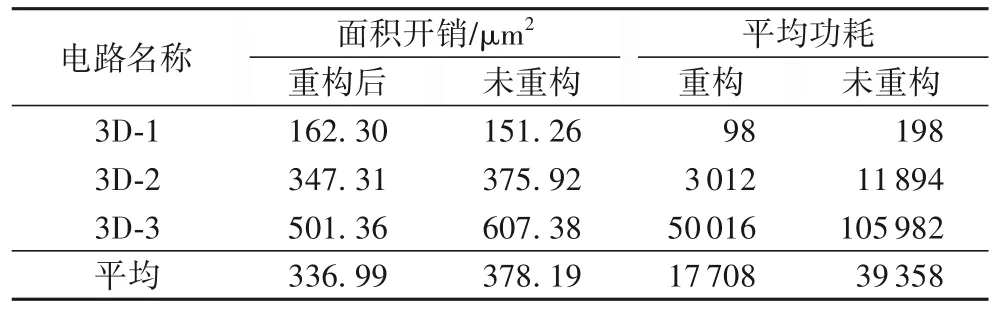

表6 是測(cè)試結(jié)構(gòu)是否復(fù)用重構(gòu)的對(duì)比結(jié)果。實(shí)驗(yàn)結(jié)果表明,相較于未重構(gòu),復(fù)用重構(gòu)后的平均面積開銷降低了10.89%。為進(jìn)一步降低測(cè)試功耗,復(fù)用重構(gòu)后的測(cè)試結(jié)構(gòu)中包括了低功耗路由模塊。復(fù)用重構(gòu)后的平均功耗開銷相較于未重構(gòu)后降低了55.01%。

表6 重構(gòu)與未重構(gòu)的實(shí)驗(yàn)結(jié)果對(duì)比Tab.6 Comparison of experimental results of reconstructed and unreconstructed structures

5 結(jié)語

針對(duì)目前三維堆疊集成電路測(cè)試中測(cè)試成本較高的問題,本文考慮測(cè)試成本中的測(cè)試資源、測(cè)試功耗以及測(cè)試時(shí)間,提出了一種低成本三維堆疊集成電路測(cè)試方案。測(cè)試方案中基于LFSR 設(shè)計(jì)了一種能夠較好地適用于三維堆疊集成電路測(cè)試的3D-LFSR 測(cè)試結(jié)構(gòu),該結(jié)構(gòu)在綁定后測(cè)試階段能夠充分復(fù)用綁定前的測(cè)試資源,降低了測(cè)試資源開銷。此外,在測(cè)試結(jié)構(gòu)中加入低功耗模塊,并結(jié)合串行和并行測(cè)試的混合測(cè)試方法,在僅增加少量測(cè)試面積開銷的前提下,降低了測(cè)試功耗和測(cè)試時(shí)間。實(shí)驗(yàn)結(jié)果表明,本文方案能夠有效地降低測(cè)試成本。未來的工作中,將結(jié)合三維堆疊集成電路中的TSV 測(cè)試開展進(jìn)一步研究。