一種多種接口時序兼容性驗證設計方法

楊帆 王哲

摘 要 針對接口從設備兼容性弱的問題,提出一種多種接口時序兼容性驗證方法,實現了靈活、方便、可控的接口從設備時序拉偏驗證功能。

關鍵詞 時序拉偏測試 接口從設備 物聯網 時序邏輯驗證 兼容

中圖分類號 TP206? ?文獻標識碼 B? ?文章編號 1000?3932(2023)03?0392?04

作者簡介:楊帆(1992-),工程師,從事軟件設計工作,yangfan@hed.com.cn。

引用本文:楊帆,王哲.一種多種接口時序兼容性驗證設計方法[J].化工自動化及儀表,2023,50(3):392-395.

隨著物聯網的發展,接口種類越來越來多,應用環境越來越復雜,接口從設備需要應對各種各樣的主設備,接口驗證不僅局限于接口協議要求,對時序兼容性的需求也越來越高。市場上不同廠家的各類接口產品設計也存在著或多或少的不同之處,因此產品需要有較高的接口兼容性。

把接口兼容性問題攔截在驗證階段,可以降低投入市場后的兼容性風險。對于從設備接口樣品驗證而言,接口的兼容性測試是十分必要的,但目前尚無靈活、方便、可控的時序拉偏驗證方法的報道。為此,筆者提出一種多種接口時序兼容性驗證設計方法,利用上位機軟件下發測試命令,通過FPGA芯片電路設計應用,靈活輸出可控的接口測試時序,將時序測試結果返回上位機,從而滿足從設備接口時序兼容性的要求,直觀準確地測試出從設備的時序拉偏性能。

1 驗證方法設計

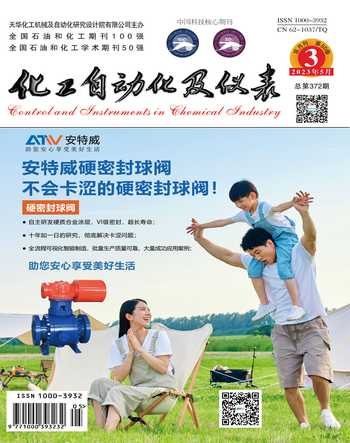

首先設計并開發FPGA芯片電路,包括5個模塊:接口解析模塊、存儲模塊、主控電路單元模塊、時鐘處理模塊和協議處理模塊,整體模塊框圖如圖1所示。接口解析模塊。選擇并配置上位機與FPGA芯片電路的通信接口,上位機軟件下發指令,接口解析模塊對指令進行解析,根據解析結果,通過主控電路單元模塊控制調用其他模塊,完成指令功能。接口解析模塊也具有將測試結果進行解析并通過與上位機連接的接口返回給上位機的功能。

存儲模塊。上位機下發存儲指令,接口解析模塊對指令進行解析,由主控電路單元模塊將目標接口驗證時序向量存儲在存儲模塊中。上位機下發測試指令,由主控電路單元模塊調取存儲模塊中已存儲的目標接口驗證時序向量,通過協議處理模塊輸出驗證時序向量,并且將采集的從接口返回的測試結果,通過主控電路單元模塊存儲在存儲模塊中,待上位機發送測試結果讀取指令時調用。

時鐘處理模塊。上位機下發時鐘配置指令,接口解析模塊對指令進行解析,通過主控電路單元模塊選擇高頻時鐘源,并經過時鐘處理模塊進行處理,以得到滿足目標時鐘時序需求的時鐘時序。

主控電路單元模塊。用于控制調用各模塊工作。上位機下發存儲指令,接口解析模塊對指令進行解析,由主控電路單元將目標接口驗證時序向量存儲在存儲模塊中。上位機軟件下發時鐘配置指令,接口解析模塊對指令進行解析,由主控電路單元模塊調用選擇高頻時鐘源,并調用時鐘處理模塊對時鐘源進行信號處理,以得到滿足目標時鐘時序需求的時鐘時序。上位機軟件下發協議選擇指令,接口解析模塊對指令進行解析,由主控電路單元模塊調用協議處理模塊進行接口協議配置。上位機軟件下發測試指令,接口解析模塊對指令進行解析,由主控電路單元模塊調用存儲模塊中已存儲的接口驗證時序向量,并調用協議處理模塊,輸出驗證時序,同時協議處理模塊采集測試結果,通過主控電路單元模塊存儲在存儲模塊中。上位機下發測試結果讀取指令,接口解析模塊對指令解析后,由主控電路單元模塊調用存儲模塊中存儲的測試結果,經接口解析模塊進行解析,通過FPGA芯片電路與上位機連接的接口返回給上位機。

協議處理模塊。在上位機發送協議選擇指令時,接口解析模塊對指令解析后,由主控電路單元模塊調用協議處理模塊,根據目標接口協議,對接口性能進行相應配置。在上位機發送測試指令時,經過接口解析模塊解析命令后,由主控電路單元模塊調用存儲模塊中的接口驗證時序向量,經協議處理模塊輸出接口驗證時序,并經協議處理模塊采集從接口時序測試結果,通過主控電路單元模塊存儲在存儲模塊中。

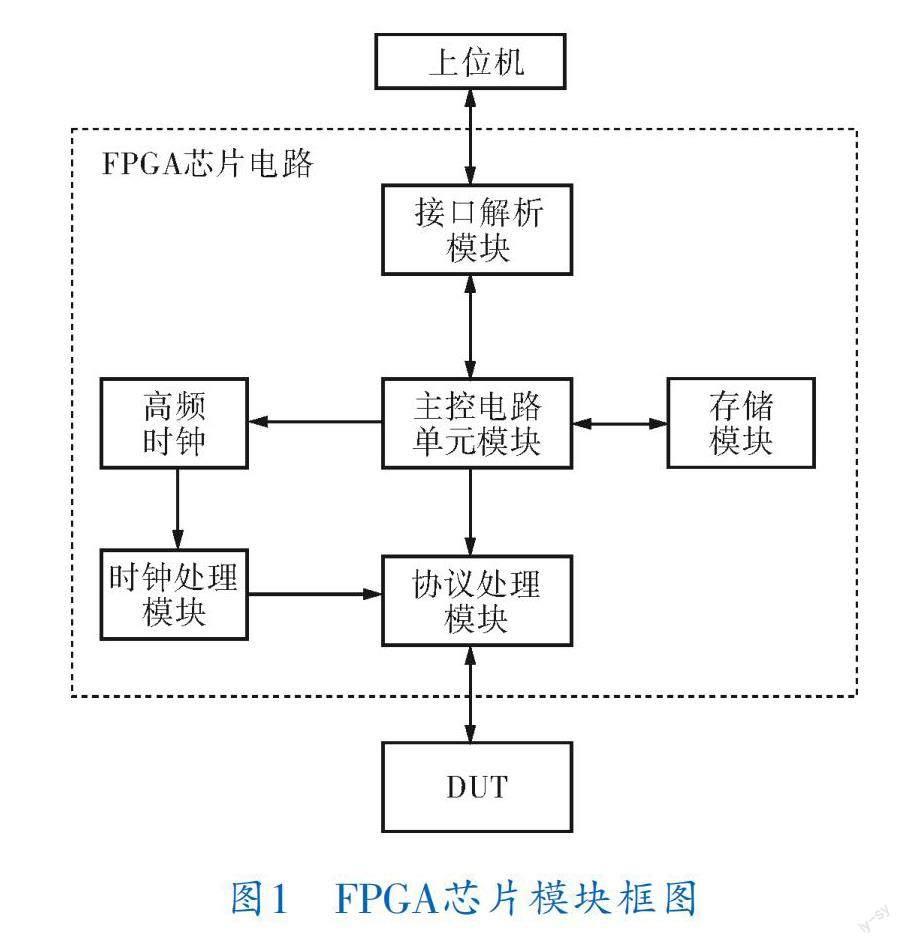

配置上位機與FPGA芯片電路的通信接口,使用上位機軟件下發測試時序向量存儲指令、時鐘配置指令、接口協議選擇指令、測試指令和測試結果讀取指令。上位機接口通信結構框圖如圖2所示。

通過接口解析模塊解析上位機指令。

通過主控電路單元模塊協調控制FPGA電路各模塊,驗證時序向量存儲的功能,選擇高頻時鐘并對時鐘信號進行處理的功能,選擇接口協議并對目標接口時序進行協議特性配置的功能,時序測試功能,以及測試結果的讀取功能。

通過靈活的指令配置,存儲并調用不同的時序向量,從而滿足對從設備接口時序拉偏驗證的要求,直觀準確地測試出從設備的時序兼容性能。

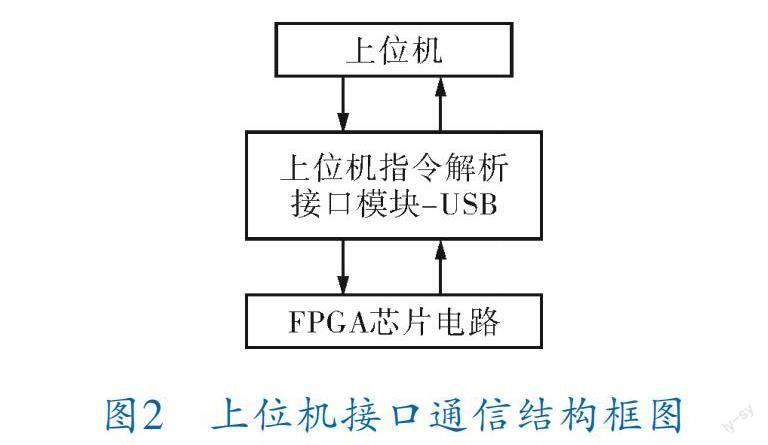

2 目標接口時序測試流程

目標接口時序測試流程如圖3所示。

上位機與FPGA芯片電路的通信接口。上位機軟件下發指令,接口解析模塊對指令進行解析,根據解析結果,通過主控電路單元模塊控制調用其他模塊,完成指令功能。接口解析模塊也可以將測試結果進行解析,并通過與上位機連接的接口返回給上位機。

上位機下發不同的驗證時序向量存儲指令。由接口解析模塊對指令進行解析后,通過主控電路單元模塊將驗證時序向量存放在存儲模塊中。

上位機下發時鐘配置指令。FPGA接口解析模塊對指令進行解析后,利用主控電路單元模塊選擇高頻時鐘源,并通過時鐘處理模塊對時鐘信號進行處理,得到滿足接口時序驗證需求的時鐘信號。

上位機下發接口協議選擇指令。接口解析模塊對指令進行解析后,利用主控電路單元模塊調用協議處理模塊,對目標接口時序進行協議配置。

上位機下發測試指令。接口解析模塊對指令進行解析后,通過主控電路單元模塊調用存儲模塊中已經存儲的不同的接口驗證時序向量,通過協議處理模塊,靈活輸出驗證時序,并采集測試結果,通過主控電路單元模塊將其存儲在存儲模塊中。

上位機下發測試結果讀取指令。接口解析模塊對指令進行解析后,由主控電路單元模塊調用存儲模塊中存儲的測試結果,經接口解析模塊進行解析后,通過與上位機連接的接口返回給上位機。

重復以上操作,遍歷需要的接口時序,就能滿足接口時序拉偏兼容性驗證。

3 方法例舉

筆者舉例說明本設計的具體實施方式。本設計方法使用的軟、硬件實現方式,可在實際操作時指定。

第1步 設計并開發FPGA芯片電路,包括5個模塊(圖1)。

第2步 PC機通過USB接口向FPGA芯片電路發送I2C接口驗證時序向量存儲指令,接口解析模塊對命令進行解析(圖2)。之后,通過主控電路單元模塊調用存儲模塊,將接收到的I2C接口驗證時序向量存儲在內部RAM中。

第3步 PC機通過USB接口向FPGA芯片電路發送I2C接口時鐘配置指令,接口解析模塊對命令進行解析后,主控電路單元模塊選擇時鐘源,并調用時鐘處理模塊將高頻時鐘源進行信號處理(圖4),即可得到滿足接口時序驗證需求的時鐘時序。

第4步 PC機通過USB接口向FPGA芯片電路發送I2C接口協議選擇指令,接口解析模塊對命令進行解析。由主控電路單元模塊調用協議處理模塊,按照I2C協議要求配置接口設置。

第5步 PC機通過USB接口向FPGA芯片電路發送I2C接口測試指令,接口解析模塊對命令進行解析。由主控電路單元模塊調用存儲模塊,讀取內部RAM中已存儲的接口拉偏驗證時序向量。通過協議處理模塊,按照I2C協議要求輸出接口驗證時序。從設備接收驗證時序后響應,通過協議處理模塊采集響應結果,并通過主控電路單元模存儲在內部RAM中。

第6步 PC機通過USB接口向FPGA芯片電路發送測試結果讀取指令,接口解析模塊對命令進行解析,主控電路單元模塊調用存儲模塊,讀取內部RAM中已存儲的測試結果,接口解析模塊對測試結果進行解析,并從USB接口向PC機返回測試結果。

第7步 重復以上操作,遍歷需要驗證的接口時序。

4 結束語

筆者提出的多種接口時序兼容性驗證設計方法,通過指令操控,利用FPGA芯片電路靈活可編程的優點,可以靈活、可控地輸出多種目標接口時序,并根據存儲的接口時序向量對接口時序進行拉偏測試,滿足了市場上從設備接口的時序兼容性驗證需求。

(收稿日期:2022-08-16)