基于STM32的EtherCAT轉(zhuǎn)UDP通信轉(zhuǎn)換系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

摘要:工業(yè)以太網(wǎng)總線技術(shù)EtherCAT是一種基于以太網(wǎng)的高性能、低成本的實(shí)時(shí)通信技術(shù),它可以實(shí)現(xiàn)分布式控制系統(tǒng)的高速、低延遲、同步和確定性的通信。EtherCAT在工業(yè)自動(dòng)化領(lǐng)域有著廣泛的應(yīng)用,如機(jī)器人、數(shù)控機(jī)床、汽車制造等。然而,EtherCAT與工控機(jī)端的通信網(wǎng)絡(luò)一般采用TCP/IP協(xié)議,由于其非實(shí)時(shí)性通信方式,不能直接與EtherCAT從站交換數(shù)據(jù),需先進(jìn)行通信協(xié)議轉(zhuǎn)換。通信轉(zhuǎn)換需要借用硬件介質(zhì)來實(shí)現(xiàn)。為了實(shí)現(xiàn)EtherCAT與工控機(jī)端的TCP/IP協(xié)議的互通,本文設(shè)計(jì)了一種基于STM32單片機(jī)的通信轉(zhuǎn)換系統(tǒng),該系統(tǒng)利用FPGA開發(fā)的高速、低延遲、同步和確定性的TCP/IP通信模塊,實(shí)現(xiàn)了EtherCAT與TCP/IP協(xié)議的轉(zhuǎn)換。本文介紹了系統(tǒng)的硬件結(jié)構(gòu)和軟件設(shè)計(jì),驗(yàn)證了系統(tǒng)的通信性能和效率。

關(guān)鍵詞:STM32F103;EtherCAT;FPGA;UDP;通信轉(zhuǎn)換

以太網(wǎng)控制自動(dòng)化技術(shù)EtherCAT在工業(yè)自動(dòng)化領(lǐng)域應(yīng)用廣泛。在工業(yè)以太網(wǎng)總線技術(shù)EtherCAT中,從站之間的通信采用分布式時(shí)鐘同步機(jī)制,保證了通信的高速、低延遲、同步和確定性。然而,EtherCAT與工控機(jī)端的通信網(wǎng)絡(luò)一般采用TCP/IP協(xié)議,由于其需要建立連接和確認(rèn)數(shù)據(jù)的傳輸,無法與EtherCAT直接進(jìn)行數(shù)據(jù)交互,導(dǎo)致了通信的非實(shí)時(shí)性,因此,需借用硬件介質(zhì)進(jìn)行通信協(xié)議轉(zhuǎn)換。伺服電機(jī)、步進(jìn)電機(jī)和輸入/輸出口的控制過程非常復(fù)雜,任何一個(gè)控制環(huán)節(jié)出錯(cuò)都會(huì)造成控制系統(tǒng)運(yùn)行不穩(wěn)。

在實(shí)際產(chǎn)品開發(fā)中,考慮成本因素?zé)o法直接在控制系統(tǒng)中運(yùn)行實(shí)時(shí)分析軟件,而是要將相應(yīng)數(shù)據(jù)實(shí)時(shí)地傳輸?shù)絇C機(jī)上,通過PC機(jī)上的數(shù)據(jù)采集、分析軟件中查找、定位問題根源。為了實(shí)現(xiàn)EtherCAT與工控機(jī)端的TCP/IP協(xié)議的互通,本文提出了一種基于UDP協(xié)議的通信轉(zhuǎn)換方案,利用UDP協(xié)議的無連接和高帶寬特點(diǎn),提高通信的效率和速度,同時(shí)利用FPGA開發(fā)的高性能TCP/IP通信模塊,保證通信的實(shí)時(shí)性和可靠性。

一、系統(tǒng)硬件設(shè)計(jì)

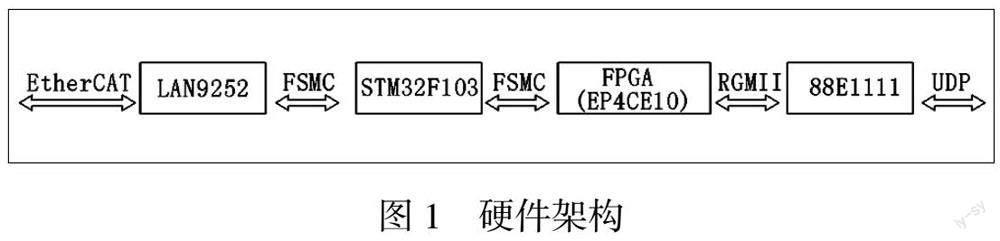

系統(tǒng)的控制部分包括STM32F103、FPGA。STM32F103程序負(fù)責(zé)控制LAN9252和FPGA的通信,以及配置88E1111 PHY芯片的寄存器。FPGA程序負(fù)責(zé)實(shí)現(xiàn)可變靜態(tài)存儲(chǔ)控制器通信模塊、UDP通信模塊和88E1111 PHY芯片配置模塊。可變靜態(tài)存儲(chǔ)控制器通信模塊用于與STM32F103進(jìn)行數(shù)據(jù)交換,UDP通信模塊用于封裝和解析UDP數(shù)據(jù)包,88E1111 PHY芯片配置模塊用于設(shè)置PHY芯片的工作模式和速率。整體硬件架構(gòu)如圖1所示。

LAN9252和STM32F103的接口電路如圖2所示。

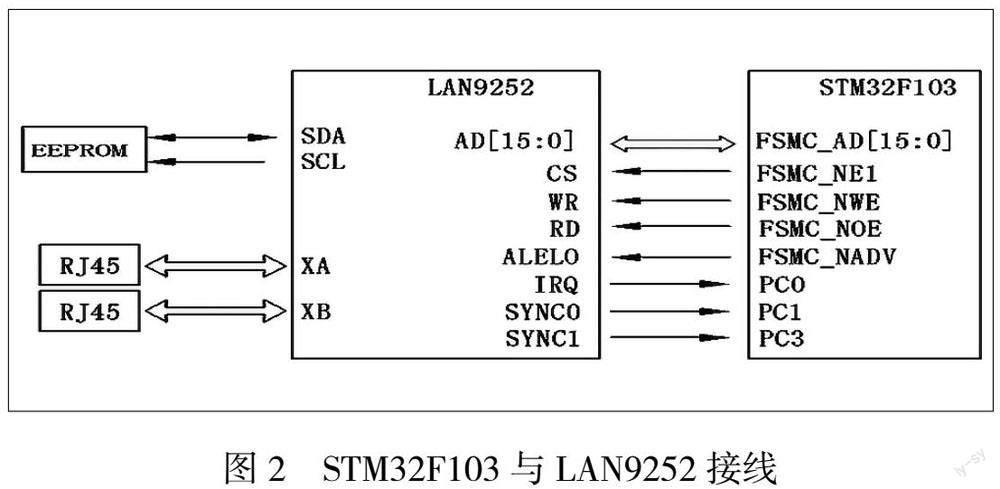

FPGA選用EP4CE10,是一種低成本、高性能的可編程邏輯器件,可以實(shí)現(xiàn)復(fù)雜的通信協(xié)議和算法。FPGA與STM32F103通過可變靜態(tài)存儲(chǔ)控制器總線進(jìn)行數(shù)據(jù)交換。

88E1111支持10/100/1000Mbps的自適應(yīng)速率,具有低功耗、高集成度、高穩(wěn)定性的特點(diǎn)。88E1111與FPGA通過GMII總線進(jìn)行數(shù)據(jù)傳輸,88E1111與工控機(jī)端的網(wǎng)卡通過RJ45接口進(jìn)行數(shù)據(jù)通信。STM32F103、FPGA與88E1111連接圖如圖3所示。

電源采用5 V供電,需要轉(zhuǎn)換成3.3V、2.5V及1.2V。

二、系統(tǒng)軟件設(shè)計(jì)

(一) STM32F103單片機(jī)程序

STM32F103是系統(tǒng)的控制核心,用于系統(tǒng)初始化,F(xiàn)PGA、LAN9252模塊之間的通信。

為了實(shí)現(xiàn)從站微控制單元的EtherCAT通信功能,本文使用SSC工具生成協(xié)議棧代碼,配置協(xié)議棧、物理層之間的接口,如可變靜態(tài)存儲(chǔ)控制器并行總線配置和輸入/輸出中斷入口配置。協(xié)議棧包含EtherCAT從站通訊模塊輸出信號(hào),需將模塊的中斷處理函數(shù)與STM32F103引腳綁定,引腳中斷功能關(guān)鍵代碼如下。

# define? ? INIT _ESC_INT? ? ?EXTIO _ Configtiration ( )

# define? ? Ecatlsr? ? ? ? ? EXTIO _ IRQHandler ;

SYNCO? ?對(duì)應(yīng)中斷功能配置及映射

#define? ? INIT_SYNC0_TEXTI3 _ Configoation ( ) ;

#define? ? Syllc0Isr? ? ? ? EXTI3_IRQHandler;

SYNC1? ? 對(duì)應(yīng)中斷功能配置及映射

#define? ?INIT_SYNC1 _INT? ? EXTI1_ Configuration ( );

#define? ? Sync1lsr? ? EXTl1_ IRQHandler;

為確保引腳快速準(zhǔn)確地響應(yīng)通信模塊信號(hào),需要在配置函數(shù)中激活引腳的中斷功能,并將其映射到外部中斷0,設(shè)置中斷優(yōu)先級(jí)為最高。再配置可變靜態(tài)存儲(chǔ)控制器并行總線,選擇異步多路PS隨機(jī)存取存儲(chǔ)器/NOR作為輸出通信方式。生成新XML文件之后,需在協(xié)議棧代碼里,修改數(shù)據(jù)定義、讀取模塊,使其與XML生成的數(shù)據(jù)量一致。在協(xié)議棧的數(shù)據(jù)定義頭文件里,修改結(jié)構(gòu)體數(shù)據(jù)量大小及初始值。生成的協(xié)議棧的代碼

如下。

typedef struct OBJ_STRUCT_PACKED_ START {

UINT16? ?ul6SulbIndexo;/ * * < \ brief Sublndex 0* /

UINT32? ?aEntries [ 32 ];? / * * < \ brief Entry? buffer * /

} OBJ_STRUCT_PACKED _END

TOBJ1601;

typedef struct OBJ_STRUCT _PACKED _ START {

UINT16? ?ul6SubIndex0; / * * < \ brief SubIndex 0* /

UINT32? ?aEntries [4]; / * * < \ brief Entry buffer * /

} OBJ_STRUCT_PACKED_END

TOBJ 1A00;

在中斷入口函數(shù)中修改數(shù)據(jù)操作,確保數(shù)據(jù)格式與XML文件保持一致,以免EtherCAT網(wǎng)絡(luò)通信不能實(shí)現(xiàn)初始化。

(二) FPGA程序開發(fā)

FPGA主要功能模塊包含:可變靜態(tài)存儲(chǔ)控制器通信、UDP收接、UDP發(fā)送、PHY配置、以太網(wǎng)MAC,F(xiàn)PGA功能模塊如圖4所示。

可變靜態(tài)存儲(chǔ)控制器通信模塊可以讀寫單片機(jī)的數(shù)據(jù),也可以發(fā)送和接收UDP數(shù)據(jù)。讀寫單片機(jī)的數(shù)據(jù)時(shí),需要進(jìn)行數(shù)據(jù)類型轉(zhuǎn)換和緩存;發(fā)送和接收UDP數(shù)據(jù)時(shí),需要解析UDP協(xié)議和添加協(xié)議頭尾。可變靜態(tài)存儲(chǔ)控制器通信模塊使用隨機(jī)存取存儲(chǔ)器作為緩存器,單片機(jī)接收到一定量的數(shù)據(jù)后,UDP發(fā)送模塊開始發(fā)送數(shù)據(jù)。88E1111是PHY芯片,通過FPGA實(shí)現(xiàn)標(biāo)識(shí)具體的網(wǎng)絡(luò)節(jié)點(diǎn)。基于ALTERA芯片,可以使用QuartusII提供的TSE IP核。TSE IP核包含數(shù)據(jù)接收、數(shù)據(jù)發(fā)送、配置和RGMII四個(gè)接口,配置接口用于設(shè)置88E1111的寄存器和連接方式。UDP協(xié)議是一種簡(jiǎn)單的面向消息的傳輸層協(xié)議,不保證消息的可靠傳遞,也不維護(hù)消息的狀態(tài),其優(yōu)點(diǎn)是簡(jiǎn)單、快速、靈活,適用于實(shí)時(shí)性要求高的應(yīng)用場(chǎng)景,如流媒體、語音、視頻等。UDP協(xié)議使用16位端口號(hào)來區(qū)分不同的應(yīng)用程序,并提供校驗(yàn)和來驗(yàn)證數(shù)據(jù)的完整性,并且還包含一個(gè)偽首部,用于計(jì)算校驗(yàn)和實(shí)時(shí)檢查IP地址是否正確。

三、系統(tǒng)調(diào)試

系統(tǒng)調(diào)試裝置如圖6所示。

調(diào)試的基本步驟如下:

1.應(yīng)用程序離線調(diào)試

在開發(fā)環(huán)境中使用模擬器或仿真器對(duì)STM32F103程序和FPGA程序進(jìn)行編譯、下載和運(yùn)行,檢查是否有語法錯(cuò)誤或邏輯錯(cuò)誤。使用斷點(diǎn)、單步執(zhí)行、變量監(jiān)視等功能觀察程序運(yùn)行狀態(tài)和數(shù)據(jù)流向,驗(yàn)證程序功能是否符合設(shè)計(jì)要求。

2.控制系統(tǒng)硬件檢查

在目標(biāo)平臺(tái)上連接STM32F103單片機(jī)、LAN9252芯片、FPGA芯片和88E1111 PHY芯片等硬件設(shè)備,檢查電源電壓、信號(hào)線連接、接口匹配等是否正常。使用示波器或邏輯分析儀等工具觀察各個(gè)總線或接口上的信號(hào)波形是否正確。

3.應(yīng)用程序在線調(diào)試

在目標(biāo)平臺(tái)上使用JTAG或SWD等接口對(duì)STM32F103單片機(jī)進(jìn)行在線調(diào)試,使用USB Blaster或JTAG等接口對(duì)FPGA芯片進(jìn)行在線調(diào)試,使用網(wǎng)線或無線網(wǎng)卡與工控機(jī)端進(jìn)行通信。使用調(diào)試工具或打印日志等方式檢查程序運(yùn)行情況和通信效果,排除可能存在的錯(cuò)誤或異常。

4.現(xiàn)場(chǎng)調(diào)試

在實(shí)際應(yīng)用場(chǎng)景中對(duì)系統(tǒng)進(jìn)行測(cè)試,模擬各種正常或異常的輸入輸出條件,觀察系統(tǒng)的響應(yīng)和輸出結(jié)果,評(píng)估系統(tǒng)的性能和穩(wěn)定性,優(yōu)化系統(tǒng)的參數(shù)和配置,解決可能出現(xiàn)的問題或故障。

在完成系統(tǒng)調(diào)試后,對(duì)調(diào)試過程中發(fā)現(xiàn)和解決的問題進(jìn)行總結(jié)和歸納,記錄調(diào)試過程中使用的工具和方法,撰寫調(diào)試報(bào)告和文檔,為后續(xù)的維護(hù)和改進(jìn)提供參考。

四、結(jié)束語

綜上所述,設(shè)置EtherCAT從站的通信周期為1ms,輸入/輸出分別為64字節(jié)、16字節(jié),在數(shù)據(jù)中添加遞增序列號(hào),通過一段時(shí)間的測(cè)試觀察序列號(hào)的變化,EtherCAT從站與UDP通信沒有丟包或通信中斷現(xiàn)象,具有較高的通信可靠性。

作者單位:殷偉 浙江寧廣有視網(wǎng)絡(luò)工程有限公司

參? 考? 文? 獻(xiàn)

[1]左振領(lǐng),何方,李霄.基于STM32的EtherCAT從站的設(shè)計(jì)與實(shí)現(xiàn).組合機(jī)床與自動(dòng)化加工技術(shù),2016(7):1-3.

[2]李益,王成杰,史世友,等.基于ZYNQ處理器的EtherCAT從站通信系統(tǒng)設(shè)計(jì)[J].控制與信息技術(shù),2022(1):59-63.

[3]馬保全,姚旺君,劉云龍,等.基于FPGA的EtherCAT從站通信鏈路分析與驗(yàn)證[J].電子技術(shù)應(yīng)用,2017,43(8):95-99.

[4]Ricardo Moraes,F(xiàn)rancisco Borges Carreiro,Paulo Bartolomeu.Enforcingthe timing behavior of real-time stations in legacy bus-based industrialEthernet networks.Computer Standards and Interfaces[J],2011,33(3):5-11.

[5]黨選舉,李帥帥,伍錫如,等.EtherCAT主站與主站通信協(xié)議的研究與實(shí)現(xiàn)[J].組合機(jī)床與自動(dòng)化加工技術(shù),2017(1):98-101.

[6]宋孫浩,鄭天江,張馳,等.輕量一體化機(jī)器人關(guān)節(jié)的SPI通信及EtherCAT通訊研究[J]. 制造業(yè)自動(dòng)化,2019,41(8):41-46.

[7]康存鋒,杜斐斐,馬春敏,等.EtherCAT協(xié)議芯片與單片機(jī)通信系統(tǒng)的研究[J].現(xiàn)代制造工程,2011(7):113-117.

[8]趙世超,左金印,魏驍,等.基于FPGA的萬兆以太網(wǎng)UDP協(xié)議通信接口設(shè)計(jì)[J].電子技術(shù)應(yīng)用,2022,48(10):113-117,122.

[9]李浩,趙晨希,關(guān)冰.基于超時(shí)重傳和多重校驗(yàn)的UDP可靠通信設(shè)計(jì)[J].測(cè)控技術(shù),2022,41(2):105-110.

[10]汪欽臣,方益民.基于Modbus UDP協(xié)議的STM32與PC實(shí)時(shí)通信的實(shí)現(xiàn)[J].儀表技術(shù)與傳感器,2020(7):67-70.

[11]柳青.基于Windows套接字的Ethercat主站協(xié)議棧設(shè)計(jì)與實(shí)現(xiàn)[J].機(jī)電產(chǎn)品開發(fā)與創(chuàng)新,2021,34(5):14-15,18.