面向CMUT的多通道數據采集系統

邢晨茹 韓建寧 藺紅彥 郝國棟

摘 ?要:隨著醫學超聲成像系統的不斷發展,電容式微機械超聲換能器(CMUT)的應用日益增多。為了滿足電容式微機械超聲換能器在超聲采集過程中的實時性、高精度、多通道數據采集需求,基于Altera公司的EP4CE10F17C8型號芯片,結合16位8通道的同步采樣芯片AD7606進行CMUT超聲換能器信號的采集與傳輸,實現CMUT超聲換能器的信號處理、采集、傳輸與顯示一體化。

關鍵詞:CMUT;EP4CE10F1717N;AD7606;多通道數據采集

中圖分類號:TN919.5 ? 文獻標識碼:A ? 文章編號:2096-4706(2023)14-0048-06

Multi-channel Data Acquisition System for CMUT

XING Chenru, HAN Jianning, LIN hongyan, HAO Guodong

(School of Information and Communication Engineering, North University of China, Taiyuan ?030051, China)

Abstract: With the continuous development of medical ultrasound imaging systems, the application of capacitive micro mechanical ultrasound transducers (CMUT) is increasing. In order to meet the real-time, high-precision, and multi-channel data acquisition requirements of capacitive micro mechanical ultrasonic transducers in the ultrasonic acquisition process, based on Altera's EP4CE10F17C8 chip, combined with a 16 bit 8-channel synchronous sampling chip AD7606, the CMUT ultrasonic transducer signal is collected and transmitted, achieving the integration of signal processing, acquisition, transmission, and display of the CMUT ultrasonic transducer.

Keywords: CMUT; EP4CE10F1717N; AD7606; multi-channel data acquisition

0 ?引 ?言

CMUT超聲換能器比壓電超聲波換能器具有更寬的帶寬和更高的靈敏度,并且其結構和加工工藝相對簡單,易于實現陣列化,可以在醫學成像應用中替代壓電超聲換能器[1,2]。我國關于CMUT技術的研究起步較晚,發展緩慢,基于CMUT超聲換能器的超聲成像系統需要逐步突破。針對CMUT超聲換能器信號的檢測以及系統的微型化需求,設計實時性強、精度高、功耗低的數據采集系統。

本文利用16位8通道的同步采樣芯片AD7606,基于Altera公司的EP4CE10F17C8型FPGA控制整體系統邏輯,設計一套高適配性的采集系統,該系統可實現8路模擬輸入信號的同步采樣。因FPGA具有靈活、高速的特性而將其用作處理器,控制模數轉換芯片[3],處理后的采樣數據通過USB控制器從FIFO接口同步傳輸到PC機,可實時接收各通道采集的數據,以供超聲成像系統對接收的數據進行成像分析。

1 ?硬件設計

1.1 ?總體框架

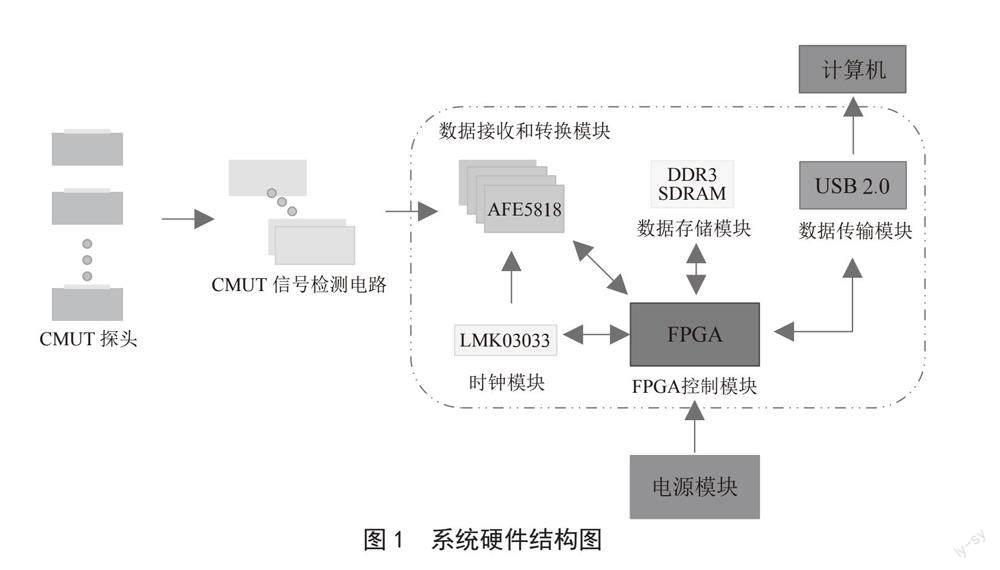

首先要確定面向CMUT超聲換能器的多通道數據采集電路的整體設計方案。為了有效檢測和接收CMUT超聲換能器的信號,需要構建一個全新的多通道數據采集電路。該電路中包含一個低噪放大模塊(用于降低系統的噪音),同時,FPGA可以根據不同的情況調節超聲回波的增益,從而在下一級傳輸時獲得更適合的信號幅度。同時接收的超聲換能器信號為模擬信號[4],通過模數轉換電路轉換為數字信號,進而實現超聲成像系統的數字化。模數轉換電路的采樣率由超聲探頭的頻率決定。再將數據由數據的發送端傳至數據的接收端,為CMUT超聲成像系統提供數據支撐。

CMUT信號采集系統的硬件主板由FPGA核心板和擴展板構成,子板為ADC數據采集板。主板主要負責控制采集狀態,接收ADC發送的模數轉換數據,將采集到的數據信號在FPGA的控制下存入FIFO緩存器進行鎖存,并通過USB接口發送給上位機;擴展板采用USB 2.0芯片,與PC機進行數據通信;AD7606芯片作為同步多路數據采集板的核心,負責將采集到的超聲模擬信號進行模數轉換,并將數字信號傳輸到FPGA。因此,整個系統是將通過檢測電路的待采集信號傳送至AD模塊進行采樣,經FPGA處理后數據通過USB接口發送給PC端,最后進行數據顯示[5]。

系統硬件整體框圖如圖1所示。

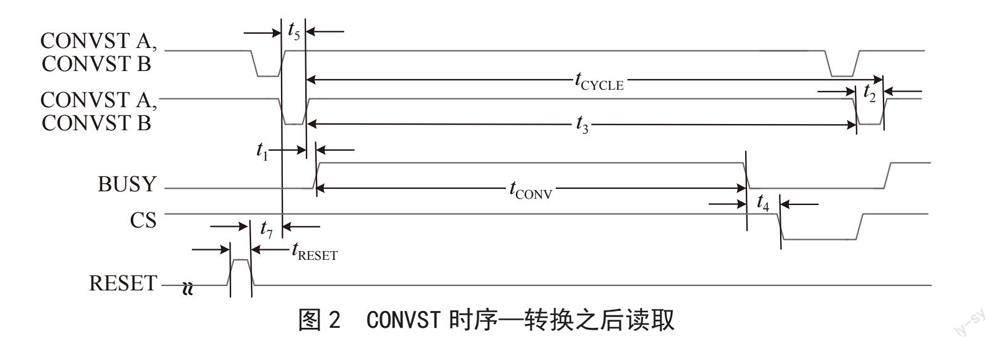

1.2 ?采集模塊設計

超聲模擬信號采集電路是超聲成像系統設計的基礎,AD7606是ADI公司生產的高性能ADC,其采用iCMOS處理技術,可以實現8通道16位逐次逼近采樣,每個通道高達200 kp/s。與傳統的逐次逼近ADC不同,AD7606芯片具有內部集成的信號調理電路,還具有低噪聲和高輸入阻抗[6,7]。此外,該芯片使用單個+5 V電源供電。當8信道信號被同步采樣時,CONVSTA和CONVSTB將被鏈接。在轉換過程中,BUSY信號變為“1”,當它下降時,8通道信號被完全轉換,數據被鎖存到輸出數據寄存器中[8]。在本設計中,芯片以串行接口模式工作,在CS信號拉低后,SCLK給出16×4 = 64個時鐘,分別讀取DOUTA輸出和采集到的通道1~4上的數據以及DOUTB輸出和采集到的通道5~8上的數據。在讀取通道1時,FRSTDATA信號拉高。時序關系如圖2所示。

1.3 ?輸入輸出接口

輸入輸出接口模塊主要是負責FPGA控制系統與上位機的數據交互。硬件接口電路對整個數據采集系統的數據傳輸速率和運行速度發揮關鍵作用,所以,本設計采用Cypress公司的EZ-USBFX2芯片,通過USB 2.0接口將PC端發送的命令發送到FPGA,實現對數據采集系統的控制;同時也可以將AD7606采集到的數據發送至PC端。該芯片是一款嵌入式USB 2.0的微處理器,其內部包含智能串行接口引擎,能夠自動終止發送和接收USB 2.0協議以及其他基本的USB功能[9]。芯片內部結構如圖3所示。

其中,USB 2.0提供一個與計算機進行數據傳輸的接口。USB 2.0控制器有四個可尋址的FIFO緩沖區,每個緩沖區都連接到單個端點,通過設置地址信號的方式選擇活動端點。FPGA與FX2芯片以FIFO方式通信,實現數據的高速傳輸。在該模式下CPU不再參與傳輸數據的過程,USB芯片在本過程中也只作為一個數據傳輸通道[10]。

2 ?軟件設計

2.1 ?AD數據采集

當CMUT超聲換能器的信號轉換為電壓信號后,需要由通過AD7606設計的信號采集電路進行采集與處理。AD測試程序以Verilog語言編寫,QuartusⅡ編譯器將編譯無誤的.sof文件通過JTAG下載到FPGA中。FRSTDATA是輸出指令信號,當芯片選擇信號CS處于高電平時,FRSTDATA將具有高阻抗,CS的下降沿將激活FRSTDATA信號。一旦可以讀取第一信號,FRSTDATA信號將跳變為高電平。當RD信號處于下降沿時,讀取第一信道信號的轉換數據,FRSTDATA信號下降到低電平,具體的時序圖如圖4所示。FRSTDATA信號僅指示讀取第一個信道信號。當CS信號保持在低電平時,RD脈沖信號可以讀取轉換后的8通道數據。最后,將采集到的數據寫入FPGA的FIFO緩存器中[11]。

本設計采用狀態機實現整個控制,共定義九個狀態進行轉換,通過輸入caiji_flag標志信號開始每次的數據采集,當數據采集結束后,輸出caiji_over結束信號。狀態機轉換流程如圖5所示。

圖5 ?AD數據采集狀態圖

2.2 ?數據存儲

根據如圖5所示的狀態機轉換過程,可以繪制出FPGA硬件程序的設計框圖,如圖6所示。在設計數據傳輸電路模塊時,FPGA負責生成數據地址,并根據地址進行數據的讀取和傳輸,而FIFO緩存器則應用于數據的存儲。當需要向FIFO寫入采集電路中的數據時,需將數據發送給FPGA芯片進行處理,同時在地址信號和控制信號的共同作用下將數據寫入FIFO[12]。如果需要對FIFO中的數據進行讀操作,FPGA控制將FIFO中對應地址的數據進行讀取,并發送給FPGA芯片,FPGA芯片再將讀取到的數據進行處理,便于USB 2.0實現對采樣數據的實時獲取,從而實現連續不斷地采集數據信號,本設計中的數據存儲及傳輸方式在減小資源占用的同時,還提高了系統的運行效率。

圖6 ?FPGA程序設計框圖

具體的執行過程是,AD7606芯片在FPGA的ADC接口控制電路的控制下,把超聲模擬信號轉換成數字信號,并將經由AD采集模塊轉換的數據存入FIFO[13],程序實現的RTL視圖如圖7所示。

2.3 ?數據傳輸

在完成超聲成像系統中數據的存儲后,需要對采集到的數據進行讀取,以便后期方便快捷地處理數據,因此,在超聲成像系統中,將超聲信號數據傳輸至電腦端模塊也是至關重要的。

FX2芯片在SlaveFIFO模式下工作時,FPGA控制模塊按照SlaveFIFO模式下的時序與上位機進行高速數據通信。如圖8所示為從設備FIFO接口與外部FPGA連接的系統框圖。此時芯片內部4 KB的FIFO存儲器將作為端點緩存,結合USB 2.0協議可配置4個端點,分別為EP2、EP4、EP6、EP8,通過改變USB固件的設置來修改其大小及緩沖倍數[14]。FPGA控制模塊輸出SlaveFIFO模式的傳輸時序,實現對端點的數據讀、寫操作,其中FX2芯片只作為FPGA與上位機數據交互的通道。

在傳輸過程中,FPGA的USB接口控制邏輯會詢問FX2是否處于空閑狀態,如果FX2處于空閑狀態,FPGA的USB接口控制邏輯將通過FPGA內部FIFO緩存將指定通道的選擇性數據發送到FX2內部FIFO。當FIFO的內部容量超過指定范圍時,FX2會打包并將所有信息傳輸至PC端[15]。同時,固件程序將FX2芯片配置為SlaveFIFO模式,在向服務器發送數據的過程中,所有操作均不受FX2內部的CPU干預,因此數據傳輸速率得到保證。

傳輸模塊的固件設計旨在完成對外部設備的初始化,處理驅動程序發送的各種命令,以及接收數據[16]。而驅動程序用于識別USB設備,在連接過程中可在主機PC側與設備側之間建立穩定的通信。

3 ?系統運行效果

在FPGA開發過程中,仿真驗證調試時序是必不可少的步驟,利用QUARTUS軟件,結合Modelsim仿真進行所開發采集系統的仿真實驗。圖9和圖10分別表示AD7606時序邏輯結果與八通道數據輸出結果。圖中可以看出各個時序的周期變化以及通道1~8分別讀取到的輸入數據結果,時序圖與代碼設定一致。

編寫tb仿真代碼,測試數據是否存儲到FPGA的FIFO中,圖11顯示了程序的模擬波形。由仿真波形圖可以看出,wr_data和rd_data交替出現并一直循環下去,wr_flag數據有效標志信號與wr_data一一對應,rd_data在讀請求信號時rd_req為高時輸出。同時還可以看到empty和full在不同的位置均有拉高的脈沖。

采集卡時序邏輯設計涵蓋USB接口控制模塊和采集卡控制模塊。先對USB接口控制模塊的程序進行測試,此時的硬件狀態為不加載采集板卡,僅控制板卡工作。在FPGA程序內部以累加器的形式替代采集數據的輸入,采用cypress公司的ControlCenter軟件,先選擇端點EP2,發送啟動采集指令使得采集卡開始工作,再從端點EP6內部讀取累加器的數據,由圖12可知,該USB 2.0接口控制模塊的程序設計有效可行。

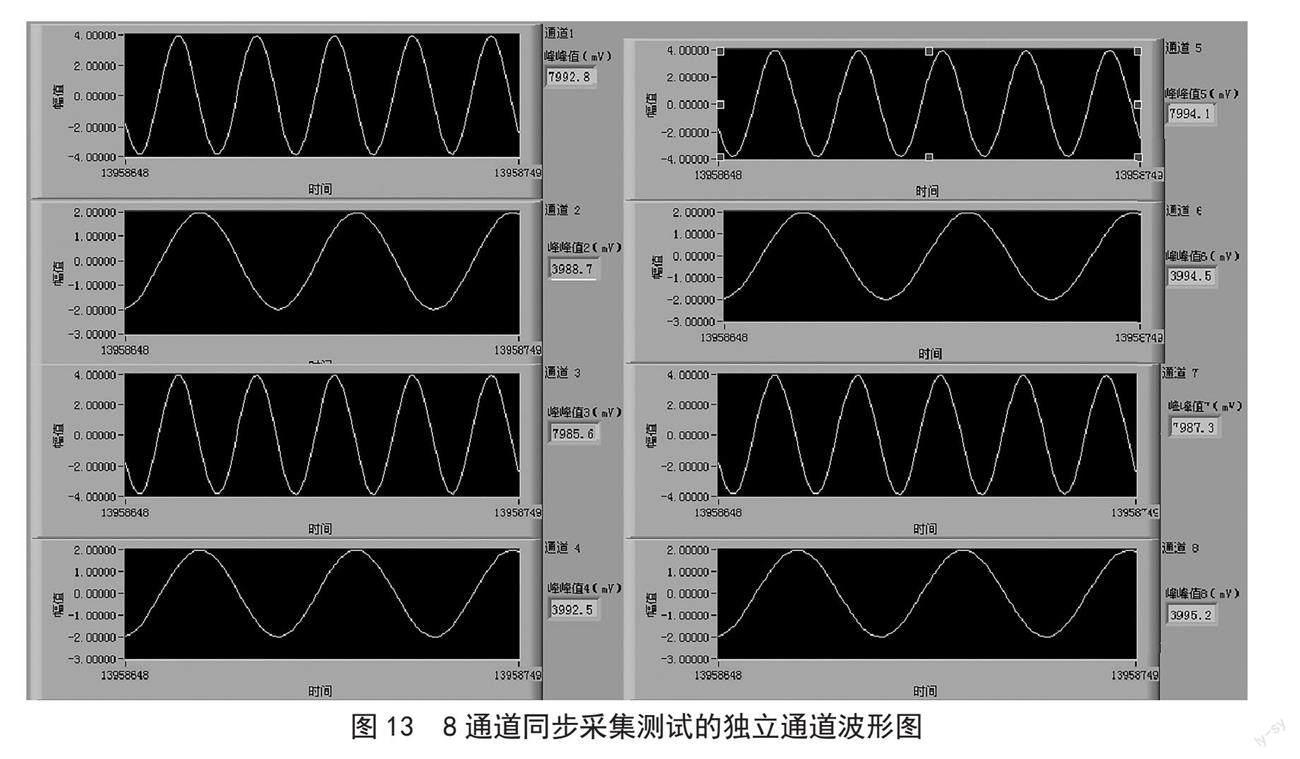

本測試選用外部信號發生器作為采集卡的模擬輸入,信號發生器的CHA通道向采集卡的1、3、5、7四個通道輸出頻率為10 kHz的標準正弦波,峰值為8 V;CHB通道向采集卡的2、4、6、8四個通道輸出頻率為5 kHz的標準正弦波,峰值為4 V。圖13顯示了Labview軟件中分別顯示的8通道同步采集的界面波形圖。

圖12 ?USB接口控制模塊的FPGA程序測試

為保證測試結果的準確性而進行了多次試驗,最終實驗結果是:8通道同步采集時,通道的最大采樣精度為0.075%,能滿足采樣精度預期指標0.1%;同時也驗證了用戶應用軟件的波形顯示功能正常。

4 ?結 ?論

隨著醫學超聲成像技術的快速發展,CMUT超聲換能器憑借其寬頻帶、高靈敏度、高機電轉換效率、微型化等優點業已成為壓電超聲換能器的有效替代。通過ADC將超聲模擬輸入信號轉換為數字信號,隨后數據將按順序存儲在FPGA的隨機存取存儲器(FIFO)中,再通過USB 2.0接口進行數據傳輸,實現與PC端的實時通信。在FPGA內部,利用VHDL語言設計了FIFO和狀態機時序控制器,實現了與USB控制器的高速數據傳輸。此外,FPGA還用于轉換和存儲數據,可以較好地控制多通道同步采集系統。通過搭建測試平臺,驗證了多通道數據采集電路的電路性能,實驗結果表明,面向CMUT的多通道高速實時數據采集系統可以實現既定功能。

參考文獻:

[1] 孟亞楠.面向CMUT的多通道數據采集電路設計與分析 [D].太原:中北大學,2022.

[2] 張澤芳,任勇峰,何常德.基于CMUT的超聲波信號檢測及放大電路設計 [J].儀表技術與傳感器,2020,445(2):37-40.

[3] 趙歡,李東偉,朱倩,等.FPGA仿真驗證工具及前沿技術綜述 [J].電子測試,2020,442(13):100-103.

[4] 賴泉青,盧露,許才彬,等.一種新型自發自收式雙頻超聲換能器 [J].電子器件,2022,45(6):1517-1522.

[5] 白曉,尹俊,鄭洋德,等.基于FPGA和LabVIEW的多通道數據采集系統設計 [J].核電子學與探測技術,2018,38(30):319-325.

[6] SHE X,XIONG J. Multi-channel electrical power data acquisition system based on AD7606 and NIOSII [C]//2011 International Conference on Electrical and Control Engineering.Yichang:IEEE,2011:1625-1627.

[7] WANG B J,MIAOL,DONG H Y,et al. Designofdynamicsynchronousmulti-channeldataacquisitionsystemforlungsoundbasedonFPGA [C]//2012 IEEE International Conference on Information and Automation. Shenyang:IEEE,2012:768-771.

[8] 田慧,管雪元,姜博文.基于Zynq的數據采集系統的研究與設計 [J].電子測量技術,2019,42(2):135-141.

[9] 郭艷.USB2.0接口多通道數據采集系統的設計 [D].西安:西安理工大學,2018.

[10] 朱瑩.基于FPGA與USB2.0的數據采集系統的設計 [J].科技資訊,2015,13(22):17-19.

[11] 肖李歡,黃元峰,代文澤,等.基于AD7606的高精度數據采集系統的實現 [J].電腦知識與技術,2017,13(20):210-211+214.

[12] MROCZEK K. USB FIFO interface for FPGA based DAQ applications [C] //2015 IEEE 8th International Conference on Intelligent Data Acquisition and Advanced Computing Systems: Technology and Applications (IDAACS).Warsaw:IEEE,2015:666-671.

[13] 李朋勃,張洪平.基于FPGA和USB2.0的高速數據采集系統 [J].單片機與嵌入式系統應用,2009,35(10):109-112.

[14] 蔣思宇,王斌,余龍海,等.基于FPGA+AD7606的多通道數據采樣系統設計與實現 [J].電子設計工程,2022,30(22):103-107.

[15] 莊洪毅.一種基于FX2與FPGA聯用實現USB2.0通信協議的方法 [J].電子測量技術,2017,40(4):78-81.

[16] 陳柯勛,王振田,王飛.基于FPGA和USB2.0的數據采集系統 [J].工業技術創新,2017,4(5):12-15.

作者簡介:邢晨茹(1999.12—),女,漢族,山西運城人,碩士研究生在讀,研究方向:多通道采集。