積分映射法I/F轉換電路的設計與實現

馮濟琴, 鄒勁松, 陳 程, 朱青松, 劉 杰, 白仲熠

(1.重慶理工大學 機械檢測技術與裝備教育部工程研究中心,重慶 400054;2.重慶工業職業技術學院, 重慶 401120;3.時柵傳感及先進檢測技術重慶市重點實驗室, 重慶 400054)

0 引言

在捷聯慣性導航系統(strapdown inertial navigation system,SINS)中,加速度計是重要的慣性元器件,其輸出的模擬電流信號需要進行前端模數轉換后再接入后端數字處理。常規的模數轉換方式有A/D轉換,V/F轉換和I/F轉換。A/D轉換的本質為間斷采樣,會造成采樣數據的丟失,實現高精度則依賴于A/D芯片的高位數,粗略估計需要24位AD芯片才能達到10-6g量級的轉換精度[1]。V/F轉換中,運算放大器的失調電壓將限制電路線性度的提高,同時溫度系數較大[2-3]。I/F轉換基于電荷平衡的原理,對加速度計輸出的電流做積分并通過模數邏輯處理通入恒定電流進行反向積分。I/F轉換不受積分失調電壓的影響,具有較高的轉換精度,一般能達到10-5g量級,適用于中高精度慣性導航系統[4]。

傳統的I/F轉換電路包括積分、門限比較、邏輯控制、開關、恒流源等眾多電路模塊。其中,門限比較模塊需要高性能雙極性輸入比較器,再適配特定阻值的高精密電阻才能實現對比較器電壓閾值的設定[5]。電路模塊眾多和高性能元器件要求對I/F轉換電路的轉換速度、穩定性、成本提出了挑戰[6]。因此,在保證I/F轉換電路基本指標的前提下,設計一種簡單穩定且不依賴于高性能元器件的I/F轉換電路十分必要。

1 I/F轉換電路原理

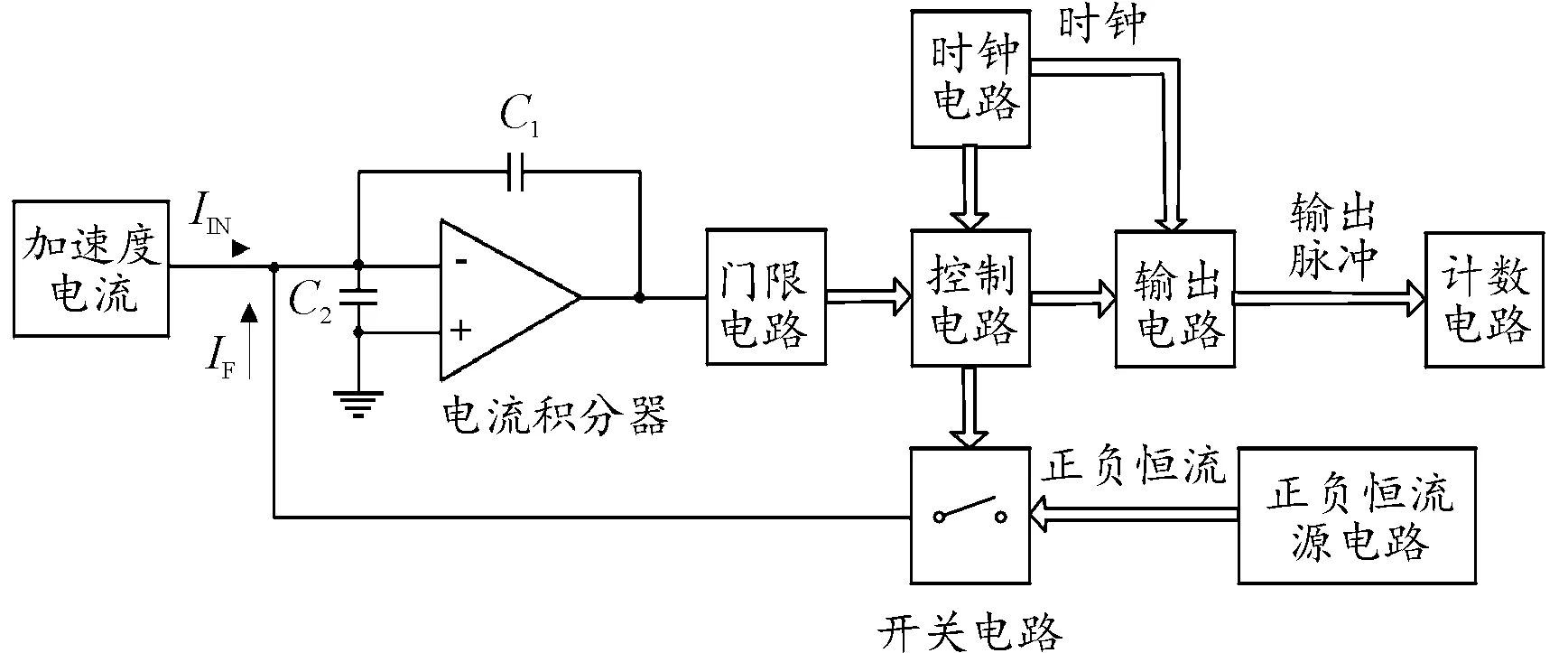

1.1 傳統I/F轉換電路原理

傳統I/F轉換原理如圖1所示。實現方式:加速度計電流信號經電流積分器轉換為電壓模擬量,將該模擬量與已設定電壓閾值的門限比較器進行比較,輸出數字比較結果再進入數字控制電路進行數字邏輯運算。輸出轉換脈沖數量和數字邏輯控制信號,通過控制補償電流的反向積分使整個模塊在一個周期內達到電荷平衡,從而實現加速度模擬量到數字量的轉換。

圖1 傳統I/F轉換原理示意圖

1.2 基于積分映射法I/F轉換電路原理

基于積分映射法I/F轉換電路的關鍵在于積分映射電路。該電路的功能是將第一級積分電壓按照所設計的放大系數映射到控制芯片的TTL標準電壓內。其中,放大系數通過推挽電路加適配負載來實現系數設定。積分映射電路的設計取決于控制芯片的選型、電路分辨率要求、電路整體功耗要求等。通過積分電壓值的放大映射,在硬件層面上利用控制芯片IO腳電壓識別特性,在邏輯上實現了控制芯片同時進行比較、邏輯控制兩功能。

I/F轉換電路基于電荷平衡原理[7-10]。基于積分映射法I/F轉換電路原理如圖2所示。

圖2 積分映射I/F轉換電路原理示意圖

電流積分器對輸入電流IIN與反饋平衡電流IF的差值在一定時間內通過積分電容C1進行積分取樣,并將取樣結果與設定的正(或負)門限電平進行同步比較。對于不平衡的比較結果,控制電路控制開關電路接通對應的正(或負)反饋恒流源,以形成若干個持續時間均為一個工作時鐘周期T的反饋單位電荷對原取樣結果進行再平衡。與此同時,控制電路輸出相應數量且與輸入電流極性對應的脈沖。對于平衡的比較結果,控制開關電路關斷反饋恒流源和脈沖輸出。上述過程在每個工作時鐘周期T內同步進行1次,使電流積分器的輸出電壓保持在設定的正/負門限電平之內,即電路保持平衡。此時:

QIN=QF

(1)

在t時間內IIN累積的電荷量為

QIN=IIN×t

(2)

(3)

由式(3)可得輸入電流IIN為

(4)

其中:F為單位時間內的輸出脈沖數(pulse/s)。

由式(4)可知,只要保證恒流源I與工作時鐘頻率f為常值,在忽略各種誤差的情況下,輸入電流IIN就與單位時間內的輸出脈沖數F成正比[11]。根據單位時間內的輸出脈沖數,利用函數關系式(4)即可得出輸入電流IIN的值。

2 電路模塊及程序設計

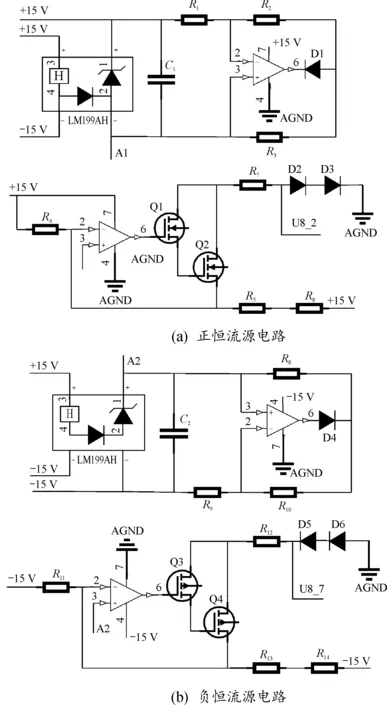

2.1 恒流源電路設計

由I/F轉換電荷平衡原理可知,恒流源電路為反向積分提供電流基準,直接影響脈沖計數的精確性。設計高精度、高穩定性和高對稱性的恒流源模塊是保證I/F轉換電路精度的根本保障。溫度是影響恒流源模塊穩定性的主要因素,當溫度變化時會影響PN結的穿透電流,使得恒流源電流發生變化。在實際應用中,為了促進精度的提升,需要基于恒壓器件進行恒流源模塊的設計[12-13]。

基于恒壓源(LM199AH)的壓控來提升恒流源精度。 LM199AH采用次表面隱埋技術,穩定性高、噪音低、受溫度影響小[14]。參數如下:電壓值為6.8~7.1 V,溫度系數為3×10-7~1×10-5,長期穩定性典型值是2×10-5/1 000 h。在恒流源模塊電壓端設計時,把采樣電阻的供電電壓與運算放大器的基準電壓統一,防止產生信號流對地電壓不足的問題。對于電路中運放的選擇,用場效應管來替代傳統的晶體管,使得放大倍數、驅動能力和基極電流得到有效提升。詳細電路如圖3所示(A1、A2標號相同處表示實際物理連接)。

圖3 恒流源電路圖

2.2 積分映射電路設計

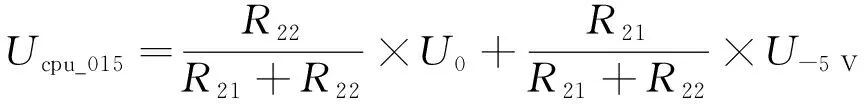

積分映射電路的功能是將第一級積分后的模擬電壓值經推挽電路通過適配不同電阻對,定比例放大到CPLD芯片引腳識別的TTL標準內,實現積分電壓值的定比例轉換。通過這種積分電壓映射設計,TTL比較的數字結果直接進入CPLD進行數字邏輯解算,CPLD實現了比較、邏輯解算兩大功能。相較于傳統I/F轉換電路需要專用比較器輸出數字比較結果、再進入CPLD進行數字邏輯解算,本設計可節約一個環節的信號處理時間,降低一個環節帶入的誤差量,減少一個環節的電路元器件數量,提高電路可靠性,實現快速比較。本設計基于I/F轉換電路分辨率要求、線性度要求,在CPLD芯片選型之后再選擇不同阻值的電阻對來實現設計目標。

根據CPLD(EPM7064SLC44-10N)的TTL標準芯片手冊可知:輸入電壓大于2 V識別為高電平,輸入電壓小于0.8 V識別為低電平。積分映射電路如圖4所示。

圖4 積分映射電路圖

X1接加速度計信號輸出端,U5_2接恒流源電路,cpu_013、cpu_015接CPLD芯片輸入引腳。電路工作過程為:當沒有加速度電流信號時,即X1輸入為0 mA。經過運算放大器U1反向積分,U1的輸出電壓為0 V(U0)。推挽電路負載電阻值依次為R19=R20=R21=3 kΩ,R22=30 kΩ。因此,0輸入時:

(5)

(6)

Ucpu _013=2.5 V,Ucpu_015=-0.455 V。

Ucpu_013=2.5 V,電壓值大于1.7 V,根據CPLD的引腳TTL標準,cpu_013對應的CPLD輸入端(標記為CPLD_13)被識別為高電平。同理,Ucpu_015=-0.455 V,電壓值小于0.8 V,cpu_015對應的CPLD輸入引腳端(標記為CPLD_15)被識別為低電平。

當X1端輸入正電流信號時,經過運算放大器U1進行反向積分,輸出為負電壓,即U0<0 V。再由式(5)和式(6)計算得到cpu_013、cpu_015的電壓值,根據CPLD的TTL標準就可以比較出對應的輸入電平信號。輸入正電流信號持續反向積分時,運算放大器U1輸出端U0<0 V,且絕對電壓值不斷增加。由式(5)可知,cpu_013端電壓值不斷減小,直到Ucpu_013<1.7 V,CPLD_13引腳被識別為低電平,此時Ucpu_015<0.8 V,整個積分過程中CPLD_15引腳一直被識別為低電平。持續積分直到CPLD_13引腳處發生電平跳轉,CPLD通過邏輯控制接通恒流源補償電路,即U5_2輸入負恒定電流。再通過反向積分,拉高Ucpu_013的電壓值,使CPLD_13引腳回到初始高電平。當小電流輸入時,恒流源補償的頻次低;大電流輸入情況下,恒流源補償頻次高,通過對恒流源通斷進行脈沖計數實現電流與頻率的線性變換。

當X1端輸入負電流信號、運算放大器U1反向積分后,輸出為正電壓。U0電壓值不斷增大,由式(6)可知cpu_015電壓值不斷增大,直到Ucpu_015>0.8 V,CPLD_15引腳被識別為高電平,此時Ucpu_013>1.7 V,CPLD_13引腳一直被識別為高電平。CPLD_15引腳處發生了電平跳轉,通過邏輯控制U5_2輸入正電流進行補償。拉低Ucpu_015的電壓值,使CPLD_15回到初始電平狀態,頻率計數方式同上。

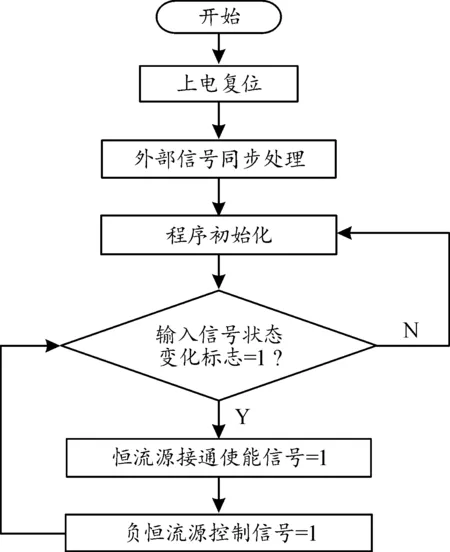

2.3 CPLD程序設計

CPLD程序設計包括用Verilog HDL語言描述FPGA邏輯過程,再經過Modlesim時序仿真,考慮布局布線延時后是否能實現邏輯功能。

CPLD對六路加速度信號進行數字邏輯并行處理,每路信號實現如圖5所示。CPLD芯片系統斷電后程序不丟失,上電復位后,首先進行外部信號同步處理,避免后續邏輯判斷過程中產生亞穩態,然后進行初始化程序[15]。

圖5 加速度計信號處理流程

3 功能仿真與實驗驗證

3.1 功能仿真

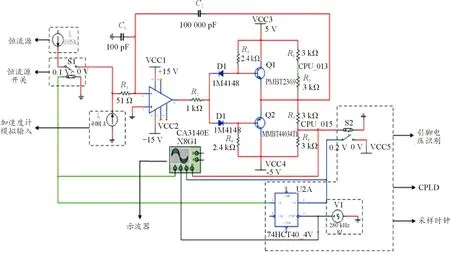

用Multisim搭建積分映射電路功能仿真模型,如圖6所示,仿真模擬-1 mA的加速度計模擬信號輸入,實際工作過程中該電流信號是連續不斷變化的。對積分定映射電路中的元器件進行模型化處理:用DC-Current直流電源模擬恒流源;積分電路的運算放大器選取5端運放器件CA3140E;壓控開關S2模擬CPLD芯片管腳電壓識別過程,即引腳電壓超過該壓控開關觸發電壓時,開關狀態跳轉,接通或關斷恒流源電路;D觸發器74HC740模擬CPLD芯片數字信號邏輯解算;電壓源Clock Voltage Source用來模擬CPLD不同的采樣頻率。最后用示波器XSC1抓取cpu_015的電壓與壓控開關S2的通斷狀態。仿真結果如圖7所示。

圖6 積分映射電路仿真模型

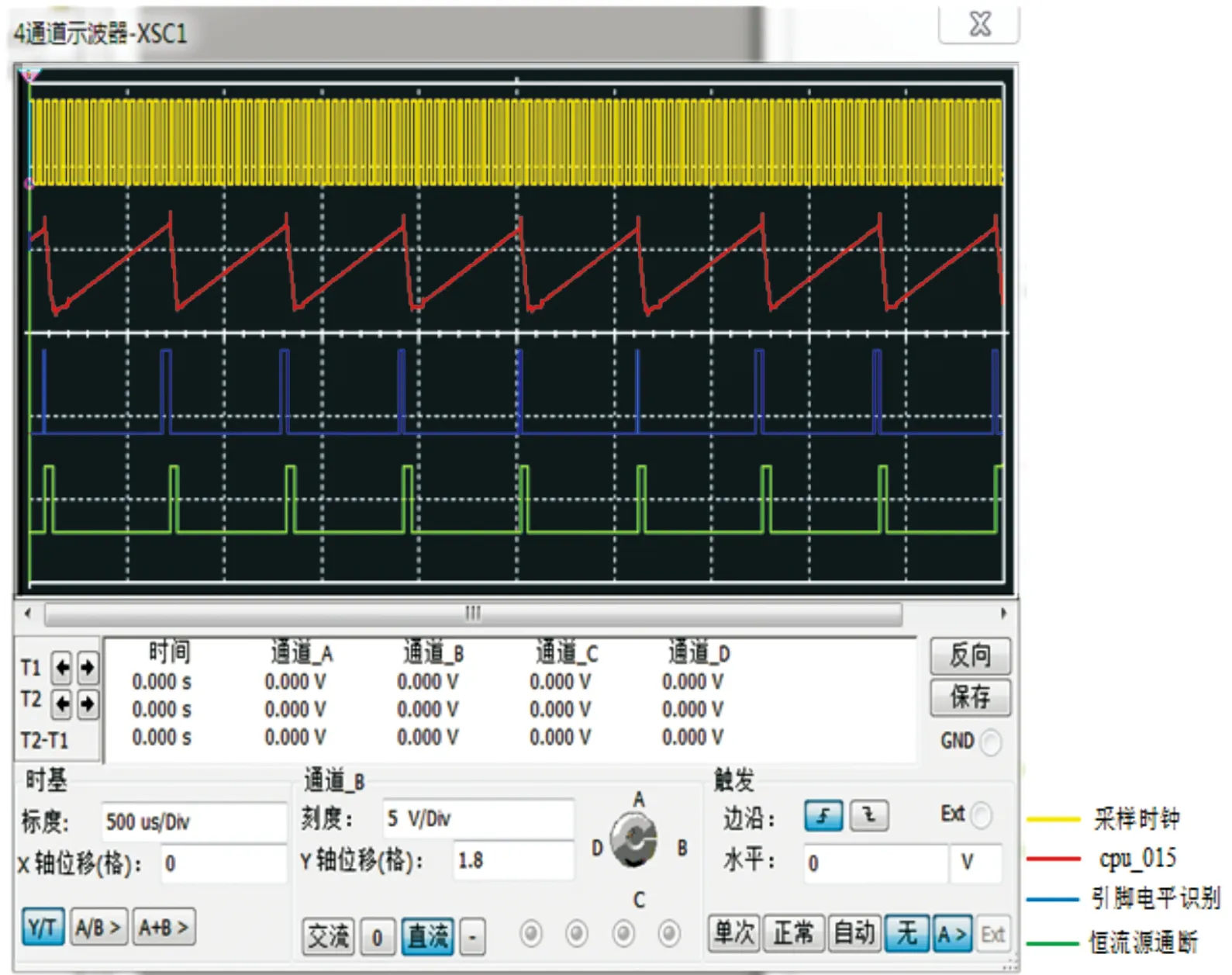

圖7 XSC1示波器界面

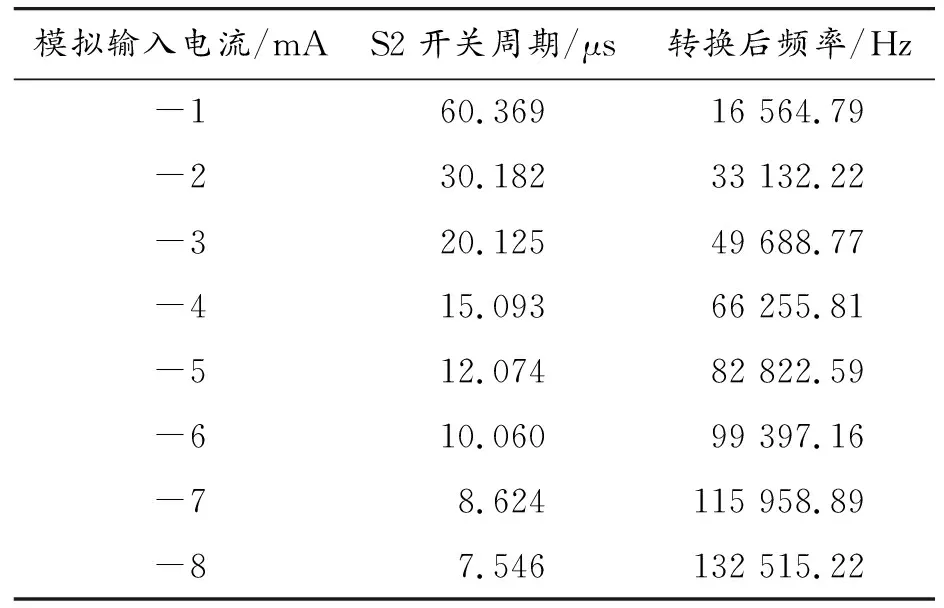

從圖7可得,當cpu_015電壓積分到壓控開關S2的觸發電壓時,壓控開關接通,通入對應的恒流源進行補償,下拉電壓值。1個時鐘周期后,開關斷開,繼續進行原積分過程。由仿真波形可知,恒定電流輸入時,I/F轉換電路的工作過程與預期相符。進一步仿真輸入不同電流信號時的電路工作情況,同時記錄壓控開關S2接通的周期,得到表1。

表1 不同模擬輸入的仿真結果

由表1可以看出,模擬輸入的電流越大,壓控開關開通的頻率越快。輸入電流和轉換后頻率為正比關系,通過計數器檢測壓控開關的通斷頻率,即可求出輸入電流信號的值。

3.2 實驗驗證

3.2.1實驗系統

實驗系統如圖8所示,超穩定高精度恒流源提供測試電流模擬加速度計任意電流輸入,用自制高精度、低噪聲的I/F電源板給I/F轉換電路供電,用示波器抓取電路信號進行功能檢測,最后通過上位機軟件保存分析數據[16]。實驗系統實物見圖8。

圖8 實驗系統實物

3.2.2零位和零位穩定性測試

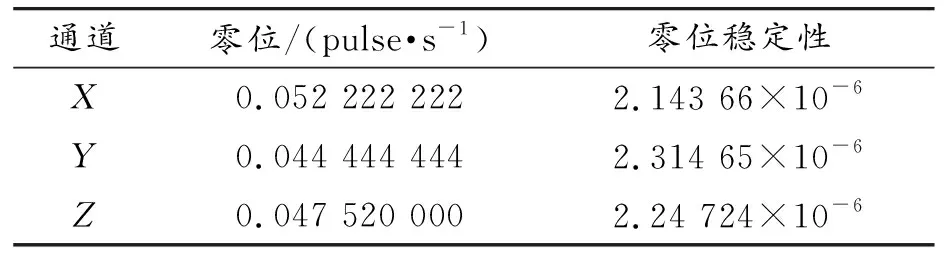

將I/F轉換電路置于恒溫25 ℃條件下,對電路的零位、刻度因數和線性度等參數進行測試。啟動電路30 min后對電路進行測試,令輸入電流為IIN=0 mA (輸入接地),每隔ΔT=20 s記錄計數器的脈沖數,持續1 h,共記錄n=180個零位數據Ni,三通道零位數據如圖9所示。

圖9 三通道零位數據曲線

(7)

(8)

由式(7)和式(8)的計算結果,得到三路I/F電路零位和零位穩定性如表2所示。

表2 三路I/F電路零位和零位穩定性

從表2可知,設計的I/F轉換電路3個通道的零位均值優于0.04 pulse/s,零位穩定性優于2.143 66×10-6。

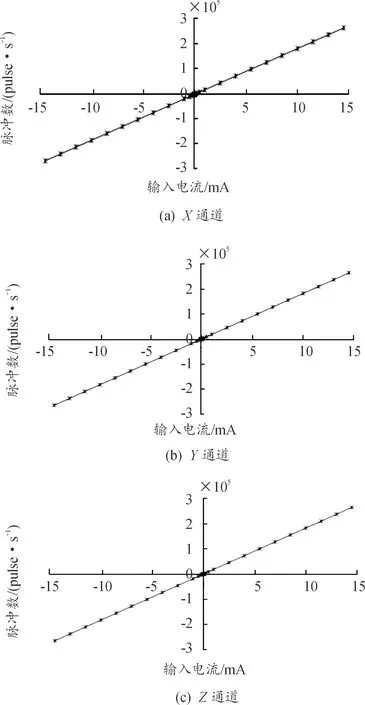

3.2.3刻度因數和線性度測試

啟動電路30 min后,打開高精度電流源給X、Y、Z三個通道輸入不同大小的電流量,采樣時間ΔT=1 s,記錄恒流源開關通斷的脈沖次數,得到輸入電流與脈沖關系如圖10所示。輸入負電流信號時,將脈沖數記為負。

圖10 輸入電流與脈沖關系曲線

(9)

由式(9)計算得到設計的I/F電路的刻度因數和線性度結果如表3所示。

表3 本方案I/F電路的刻度因數和線性度

由表3可以得出所設計的I/F轉換電路的刻度因數為18 250 Hz/mA,線性度小于10個ppm。

4 結論

所設的I/F轉換電路計電路零位穩定性優于2.143 66×10-6,線性度小于10個ppm,實現了I/F 轉換電路的高線性度和高零位穩定性,可應用于中高精度捷聯慣導系統加速度計信號處理。所提出的積分映射方法在特定積分信號處理領域具有應用價值。