基于FPGA的簡(jiǎn)易計(jì)算器的設(shè)計(jì)與實(shí)現(xiàn)

李強(qiáng) 房雅文 黃蕾 李雪 王世龍 陳初俠

關(guān)鍵詞:簡(jiǎn)易計(jì)算器;FPGA;Verilog HDL;Quartus II

中圖分類號(hào):TP29 文獻(xiàn)標(biāo)識(shí)碼:A

文章編號(hào):1009-3044(2024)03-0046-04

0 引言

計(jì)算器作為一種簡(jiǎn)單而實(shí)用的計(jì)算工具,在日常生活中被廣泛使用,如今市場(chǎng)上的計(jì)算器種類豐富且功能多樣,但功能過(guò)多的計(jì)算器價(jià)格昂貴且大多數(shù)功能可能還用不上,所以設(shè)計(jì)一款簡(jiǎn)單而實(shí)用的計(jì)算器具有較好的現(xiàn)實(shí)意義[1]。本文基于Quartus II 13.1軟件和Verilog HDL語(yǔ)言設(shè)計(jì)了一款簡(jiǎn)易計(jì)算器,主控芯片采用Altera公司Cyclone Ⅳ E系列的FPGA芯片EP4CE6E22C8[2]。所設(shè)計(jì)的簡(jiǎn)易計(jì)算器具有加減乘除四則運(yùn)算功能,輸入的兩個(gè)操作數(shù)采用撥碼開(kāi)關(guān)來(lái)實(shí)現(xiàn),輸出結(jié)果用數(shù)碼管進(jìn)行顯示。

1 簡(jiǎn)易計(jì)算器設(shè)計(jì)要求

簡(jiǎn)易計(jì)算器設(shè)計(jì)要求如下:

1) 能實(shí)現(xiàn)操作數(shù)0至15的加減乘除四則運(yùn)算。

2) 具有復(fù)位功能,當(dāng)復(fù)位時(shí)運(yùn)算結(jié)果為0。

3) 輸入數(shù)據(jù)用四位二進(jìn)制表示,通過(guò)8個(gè)撥碼開(kāi)關(guān)來(lái)實(shí)現(xiàn)。

4) 輸入數(shù)據(jù)和計(jì)算結(jié)果采用8個(gè)共陽(yáng)極八段數(shù)碼管顯示。

5) 四則運(yùn)算的選擇通過(guò)4個(gè)獨(dú)立按鍵來(lái)實(shí)現(xiàn)。

6) 具有LED點(diǎn)亮功能,當(dāng)選擇不同的運(yùn)算時(shí)會(huì)有與之對(duì)應(yīng)的LED燈被點(diǎn)亮。

7) 減法運(yùn)算時(shí),若被減數(shù)小于減數(shù),運(yùn)算結(jié)果能顯示負(fù)號(hào)“-”。

8) 除法運(yùn)算時(shí),運(yùn)算結(jié)果要保留一位小數(shù),當(dāng)除數(shù)為零時(shí),顯示的運(yùn)算結(jié)果為“EE.E”。

2 簡(jiǎn)易計(jì)算器設(shè)計(jì)方案

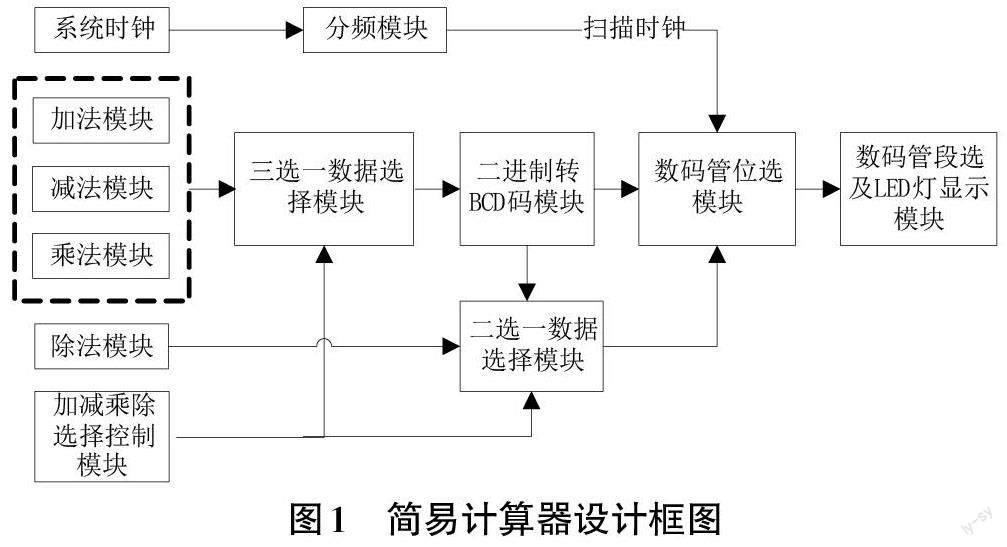

簡(jiǎn)易計(jì)算器設(shè)計(jì)框圖如圖1所示,根據(jù)設(shè)計(jì)要求,簡(jiǎn)易計(jì)算器電路分為六部分,分別是分頻、運(yùn)算、選擇控制、數(shù)據(jù)選擇、碼制轉(zhuǎn)換和顯示。分頻是將高頻率的系統(tǒng)時(shí)鐘50MHz轉(zhuǎn)為用于數(shù)碼管動(dòng)態(tài)掃描的較低頻率時(shí)鐘10KHz;運(yùn)算包括加減乘除運(yùn)算四個(gè)模塊,實(shí)現(xiàn)四則運(yùn)算功能;選擇控制用于選擇不同的獨(dú)立按鍵實(shí)現(xiàn)加減乘除四種運(yùn)算操作;數(shù)據(jù)選擇包括三選一和二選一數(shù)據(jù)選擇模塊,三選一數(shù)據(jù)選擇模塊實(shí)現(xiàn)對(duì)加法、減法、乘法運(yùn)算結(jié)果的選擇,二選一數(shù)據(jù)選擇模塊實(shí)現(xiàn)除法運(yùn)算結(jié)果和加減乘運(yùn)算結(jié)果的選擇;碼制轉(zhuǎn)換是把加減乘運(yùn)算結(jié)果的二進(jìn)制數(shù)據(jù)轉(zhuǎn)換為8421BCD碼,便于后面數(shù)碼管的顯示;顯示包含數(shù)碼管的位選、段選和LED顯示,用于展示運(yùn)算結(jié)果。

3 簡(jiǎn)易計(jì)算器設(shè)計(jì)本設(shè)計(jì)

采用層次化的設(shè)計(jì)方法,即先設(shè)計(jì)底層電路再設(shè)計(jì)頂層電路。底層電路用Verilog HDL語(yǔ)言來(lái)實(shí)現(xiàn),頂層電路通過(guò)調(diào)用底層電路用原理圖方式來(lái)實(shí)現(xiàn)[3]。

3.1 底層電路設(shè)計(jì)

底層電路有11個(gè)模塊,分別是5000分頻模塊、加法模塊、減法模塊、乘法模塊、除法模塊、加減乘除選擇控制模塊、三選一數(shù)據(jù)選擇模塊、二選一數(shù)據(jù)選擇模塊、二進(jìn)制轉(zhuǎn)8421BCD碼模塊、數(shù)碼管位選模塊和數(shù)碼管段選及LED燈顯示模塊。下面對(duì)它們進(jìn)行分別介紹。

3.1.1 5000分頻模塊

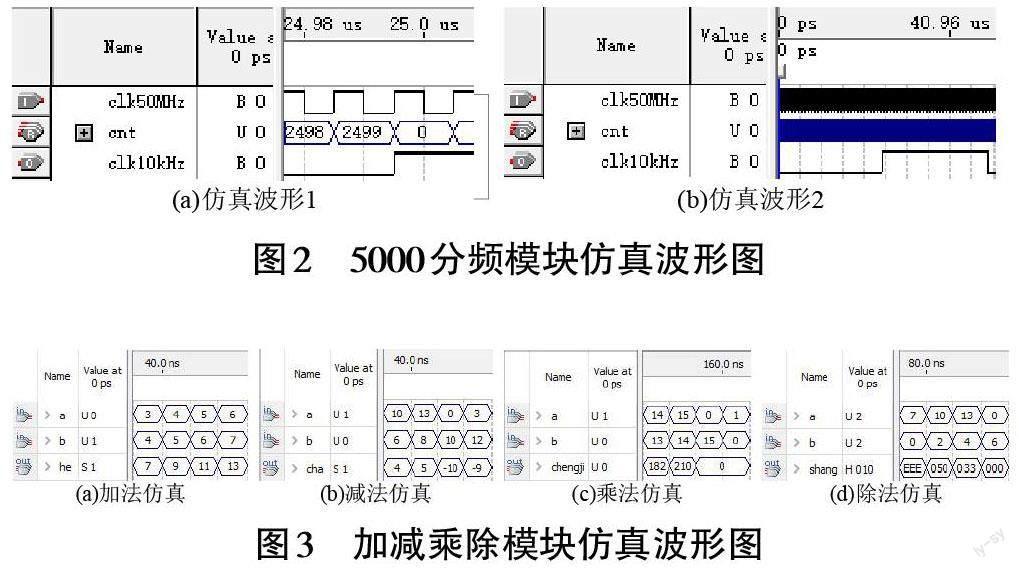

5000 分頻模塊是實(shí)現(xiàn)50MHz 系統(tǒng)時(shí)鐘分頻為10KHz時(shí)鐘,用于數(shù)碼管的動(dòng)態(tài)掃描[4]。圖2為5000 分頻模塊仿真波形圖,從圖2(a)可以看出,對(duì)于輸入時(shí)鐘clk50MHz,每來(lái)一個(gè)上升沿就計(jì)數(shù)一次,當(dāng)計(jì)到2499時(shí),輸出時(shí)鐘clk10KHz進(jìn)行翻轉(zhuǎn)。也就是說(shuō)計(jì)數(shù)5000次,輸出時(shí)鐘有一半是低電平有一半是高電平,實(shí)現(xiàn)了1 比1 的5000 分頻時(shí)鐘信號(hào),如圖2(b) 所示。

3.1.2 加減乘除模塊

加減乘除模塊輸入的2個(gè)操作數(shù)為四位二進(jìn)制數(shù)據(jù),加減乘運(yùn)算輸出結(jié)果用八位二進(jìn)制數(shù)據(jù)表示,除法運(yùn)算輸出結(jié)果用12位8421BCD碼顯示。圖3為加減乘除模塊的仿真波形圖,輸入數(shù)據(jù)都設(shè)為無(wú)符號(hào)十進(jìn)制數(shù),輸出結(jié)果加法和減法設(shè)為有符號(hào)十進(jìn)制數(shù)、乘法設(shè)為無(wú)符號(hào)十進(jìn)制數(shù),除法設(shè)為十六進(jìn)制數(shù)。由圖3(a)(b)(c)可以看出,加法運(yùn)算、減法運(yùn)算、乘法運(yùn)算,運(yùn)算結(jié)果均正確。對(duì)于除法運(yùn)算,當(dāng)除數(shù)為0時(shí),運(yùn)算結(jié)果為無(wú)窮大,結(jié)果顯示為EEE;當(dāng)除數(shù)不為0時(shí),運(yùn)算結(jié)果保留到小數(shù)點(diǎn)后一位,例如13除以4,運(yùn)算結(jié)果為3.3,顯示值用033表示。

3.1.3 加減乘除選擇控制模塊

加減乘除選擇控制模塊通過(guò)選擇不同的獨(dú)立按鍵,使輸入的兩個(gè)操作數(shù)進(jìn)行對(duì)應(yīng)的四則運(yùn)算,在無(wú)獨(dú)立按鍵按下時(shí),默認(rèn)輸出為加法運(yùn)算結(jié)果。圖4為加減乘除選擇控制模塊仿真波形圖,輸入信號(hào)s0、s1、s2、s3代表四個(gè)獨(dú)立按鍵,輸出信號(hào)m為加減乘除運(yùn)算控制信號(hào),當(dāng)m 為“1000”時(shí)代表加法運(yùn)算,為“0100”時(shí)代表減法運(yùn)算,為“0010”時(shí)代表乘法運(yùn)算,為“0001”時(shí)為除法運(yùn)算。因?yàn)楠?dú)立按鍵正常情況是彈起狀態(tài),所以彈起時(shí)用高電平表示,按下用低電平表示。可以看出,當(dāng)s0、s1、s2、s3分別為X、1、1、1時(shí)(X 代表0或1) ,m為“1000”;當(dāng)s0、s1、s2、s3分別為1、0、1、1時(shí),m為“0100”;當(dāng)s0、s1、s2、s3分別為1、1、0、1 時(shí),m為“0010”;當(dāng)s0、s1、s2、s3分別為1、1、1、0時(shí),m 為“0001”。

3.1.4 三選一數(shù)據(jù)選擇模塊

三選一數(shù)據(jù)選擇模塊是在選擇控制信號(hào)m的驅(qū)動(dòng)下,對(duì)加減乘三種運(yùn)算的結(jié)果進(jìn)行選擇輸出,輸入信號(hào)有加法運(yùn)算結(jié)果he、減法運(yùn)算結(jié)果cha、乘法運(yùn)算結(jié)果chengji、選擇控制信號(hào)m;輸出信號(hào)為out,它的數(shù)值為he、cha、chengji中的一個(gè)。圖5為三選一數(shù)據(jù)選擇模塊仿真波形圖,可以看出,當(dāng)m為“1000”時(shí),out 的數(shù)值和he相同;當(dāng)m為“0100”時(shí),out的數(shù)值和cha 相同;當(dāng)m為“0010”時(shí),out的數(shù)值和chengji相同。

3.1.5 二選一數(shù)據(jù)選擇模塊

二選一數(shù)據(jù)選擇模塊是在控制信號(hào)m的作用下,從二進(jìn)制轉(zhuǎn)8421BCD碼模塊輸出信號(hào)out_bcd和除法結(jié)果shang中選一個(gè)進(jìn)行輸出。輸入信號(hào)有8421BCD 碼out_bcd、除法運(yùn)算結(jié)果shang、選擇控制信號(hào)m;輸出信號(hào)為運(yùn)算結(jié)果jieguo。當(dāng)m為“0000”或“1000”或“0100”或“0010”時(shí),jieguo為out_bcd的數(shù)值;當(dāng)m為“0001”時(shí),jieguo為shang的數(shù)值。

3.1.6 二進(jìn)制轉(zhuǎn)8421BCD 碼模塊

二進(jìn)制轉(zhuǎn)8421BCD 碼模塊是利用二進(jìn)制數(shù)轉(zhuǎn)8421BCD碼原理[5],將四位二進(jìn)制輸入信號(hào)轉(zhuǎn)為八位BCD碼,將八位二進(jìn)制輸入信號(hào)轉(zhuǎn)為十二位BCD碼數(shù)。輸入信號(hào)有操作數(shù)a和b、加減乘運(yùn)算結(jié)果out;輸出信號(hào)有8421BCD 碼a_bcd、b_bcd 和out_bcd。圖6 為二進(jìn)制轉(zhuǎn)8421BCD碼模塊仿真波形圖,可以看出,輸入的a、b、out二進(jìn)制數(shù)據(jù)經(jīng)過(guò)轉(zhuǎn)換后得到的BCD碼正確。例如當(dāng)b為二進(jìn)制數(shù)據(jù)“1111”時(shí),其十進(jìn)制數(shù)為15,BCD碼為“00010101”,與仿真結(jié)果一致;當(dāng)out 為二進(jìn)制數(shù)據(jù)“00110100”時(shí),其十進(jìn)制數(shù)為52,BCD 碼為“000001010010”,與仿真結(jié)果一致。

3.1.7 數(shù)碼管位選模塊

數(shù)碼管位選模塊采用動(dòng)態(tài)掃描的方式用八個(gè)數(shù)碼管來(lái)表示輸出,從左邊數(shù)起前面四個(gè)數(shù)碼管顯示操作數(shù)a和b,第五個(gè)數(shù)碼管顯示符號(hào)“=”,最后三個(gè)數(shù)碼管顯示運(yùn)算結(jié)果。輸入信號(hào)有動(dòng)態(tài)掃描復(fù)位信號(hào)reset,掃描時(shí)鐘clk10KHZ,操作數(shù)a和b,8421BCD碼a_bcd、b_bcd、out_bcd,選擇控制信號(hào)m;輸出信號(hào)有位選控制信號(hào)sel和輸出數(shù)據(jù)dataout。

圖7 為數(shù)碼管位選模塊仿真波形圖,此時(shí)m 為“0100”,實(shí)現(xiàn)的是減法運(yùn)算。被減數(shù)a_bcd為十進(jìn)制數(shù)5(BCD碼為00000101) ,減數(shù)b_bcd為十進(jìn)制數(shù)3(BCD 碼為00000011) ,差out_bcd 為十進(jìn)制數(shù)2(BCD 碼為000000000010) 。理論上數(shù)碼管從左至右顯示應(yīng)為“0503=002”,即5減3等于2。因?yàn)閿?shù)碼管顯示采用的是動(dòng)態(tài)掃描的方式,所以每一時(shí)刻只有一個(gè)數(shù)碼管被點(diǎn)亮,例如當(dāng)sel為“10000000”時(shí),表示最左邊的數(shù)碼管點(diǎn)亮;sel為“01000000”時(shí),表示從左邊數(shù)起第二個(gè)數(shù)碼管點(diǎn)亮;sel為“00100000”時(shí),表示第三個(gè)數(shù)碼管點(diǎn)亮等。

dataout為數(shù)碼管顯示的數(shù)值,可以看到,當(dāng)sel為“10000000”時(shí),dataout 顯示的是第一個(gè)數(shù)碼管的值0;當(dāng)sel 為“01000000”時(shí),dataout顯示的是第二個(gè)數(shù)碼管的值5;當(dāng)sel為“00100000”時(shí),dataout顯示的是第三個(gè)數(shù)碼管的值0;當(dāng)sel 為“00010000”時(shí),dataout顯示的是第四個(gè)數(shù)碼管的值3;當(dāng)sel為“00001000”時(shí),dataout顯示的是第五個(gè)數(shù)碼管的值“=”(編碼用十進(jìn)制數(shù)10 表示);當(dāng)sel 為“00000100”時(shí),dataout顯示的是第六個(gè)數(shù)碼管的值0;當(dāng)sel為“00000010”時(shí),dataout顯示的是第七個(gè)數(shù)碼管的值0;當(dāng)sel 為“00000001”時(shí),dataout顯示的是第八個(gè)數(shù)碼管的值2。這一仿真結(jié)果與理論數(shù)值一致。

3.1.8 數(shù)碼管段選及LED 燈顯示模塊

數(shù)碼管段選及LED燈顯示模塊中,輸入數(shù)據(jù)da?tain為數(shù)碼管顯示的數(shù)值,為了顯示除法運(yùn)算的結(jié)果(除法運(yùn)算結(jié)果帶小數(shù)點(diǎn)),輸入信號(hào)加入了數(shù)碼管位選信號(hào)sel和運(yùn)算控制信號(hào)m,輸出信號(hào)有數(shù)碼管段選信號(hào)seg和LED燈顯示信號(hào)led。

圖8為數(shù)碼管段選及LED燈顯示模塊仿真波形圖,輸入數(shù)據(jù)datain 為3,數(shù)碼管采用的是共陽(yáng)極顯示,理論上顯示“3”時(shí)段選信號(hào)seg 輸出編碼為10110000,若顯示“3.”(帶小數(shù)點(diǎn))時(shí)則編碼為“00110000”。從仿真波形可以看出,當(dāng)m為加法運(yùn)算(1000) 、減法運(yùn)算(0100) 和乘法運(yùn)算(0010) 時(shí),運(yùn)算結(jié)果都不會(huì)有小數(shù)點(diǎn),且seg輸出正確;當(dāng)m為減法運(yùn)算(0001) 時(shí),只有倒數(shù)第二個(gè)數(shù)碼管顯示會(huì)帶小數(shù)點(diǎn),seg輸出結(jié)果與理論一致。另外,進(jìn)行加減乘除運(yùn)算時(shí),led都有三個(gè)燈點(diǎn)亮,仿真結(jié)果與設(shè)想一致。

3.2 頂層電路設(shè)計(jì)

簡(jiǎn)易計(jì)算器頂層電路是用原理圖設(shè)計(jì)方式進(jìn)行設(shè)計(jì),通過(guò)調(diào)用已生成的各底層模塊元件符號(hào),并將它們連接就可實(shí)現(xiàn)頂層電路,如圖9所示。

4 簡(jiǎn)易計(jì)算器的硬件實(shí)現(xiàn)

本設(shè)計(jì)采用小梅哥AC101-EDA 開(kāi)發(fā)板作為硬件驗(yàn)證平臺(tái),在設(shè)計(jì)好頂層電路的基礎(chǔ)上,進(jìn)行管腳鎖定,編譯并將生成的文件下載到FPGA開(kāi)發(fā)版上進(jìn)行硬件驗(yàn)證。硬件驗(yàn)證現(xiàn)象如圖10所示,(a)、(b)、(c)、(d)分別為加減乘除運(yùn)算及其顯示結(jié)果,可以看出,顯示的運(yùn)算結(jié)果與理論數(shù)值一致,并且在進(jìn)行不同的運(yùn)算時(shí)相應(yīng)的LED燈會(huì)被點(diǎn)亮,這說(shuō)明所設(shè)計(jì)的電路完全實(shí)現(xiàn)了簡(jiǎn)易計(jì)算器的設(shè)計(jì)要求。

5 結(jié)束語(yǔ)

本文通過(guò)Quartus II 13.1軟件和小梅哥AC101-EDA開(kāi)發(fā)板設(shè)計(jì)了一款簡(jiǎn)易計(jì)算器。首先,通過(guò)對(duì)功能需求的分析,將設(shè)計(jì)分為六部分,包含11個(gè)底層電路模塊;然后在Quartus II 13.1軟件上通過(guò)Verilog HDL語(yǔ)言和原理圖相結(jié)合的方式設(shè)計(jì)了底層電路和頂層電路;最后把頂層電路下載到FPGA開(kāi)發(fā)板中進(jìn)行了硬件測(cè)試,結(jié)果表明,所設(shè)計(jì)的簡(jiǎn)易計(jì)算器能實(shí)現(xiàn)設(shè)計(jì)要求的所有功能,具有一定的實(shí)用價(jià)值。

【通聯(lián)編輯:朱寶貴】

- 電腦知識(shí)與技術(shù)的其它文章

- 基于學(xué)習(xí)通平臺(tái)的計(jì)算機(jī)專業(yè)混合式教學(xué)實(shí)踐探索

- 學(xué)科競(jìng)賽驅(qū)動(dòng)的數(shù)據(jù)結(jié)構(gòu)教學(xué)改革研究

- 基于虛擬現(xiàn)實(shí)技術(shù)的三維動(dòng)畫(huà)課程教學(xué)設(shè)計(jì)

- 面向?qū)ο蟪绦蛟O(shè)計(jì)課程教學(xué)改革與實(shí)踐研究

- 基于OBE理念的高職Python程序設(shè)計(jì)課程專創(chuàng)融合教學(xué)改革研究

- 融合SPOC模式的分層教學(xué)法在本科教學(xué)中的應(yīng)用