基于FPGA 的高精度振動(dòng)采集傳輸系統(tǒng)?

李東星 榮 剛 穆克強(qiáng) 任勇峰 賈興中

(1.北京航天長(zhǎng)征飛行器研究所 北京 100048)(2.中國(guó)運(yùn)載火箭技術(shù)研究院 北京 100071)(3.中北大學(xué)儀器科學(xué)與動(dòng)態(tài)測(cè)試教育部重點(diǎn)實(shí)驗(yàn)室 太原 030051)

1 引言

在航天飛行測(cè)試中,由于發(fā)動(dòng)機(jī)或風(fēng)阻等的影響在飛行器各個(gè)地方會(huì)產(chǎn)生不同頻率的振動(dòng)[1~2],若振動(dòng)在艙內(nèi)關(guān)鍵部位發(fā)生諧振會(huì)成為重大的安全隱患。對(duì)于這類振動(dòng)的準(zhǔn)確測(cè)量能夠判斷飛行過(guò)程中的異常、排除故障,進(jìn)而為飛行器的可靠性與穩(wěn)定性改進(jìn)提供有力的依據(jù)[3~4]。因此,需要設(shè)計(jì)一個(gè)高精度的多路振動(dòng)采集傳輸系統(tǒng),使得飛行器上多處測(cè)點(diǎn)的振動(dòng)信能夠被精確地采集并存儲(chǔ),便于故障的發(fā)現(xiàn)、排除[5]。

本文提出一種由電荷前置處理、抗飽和電荷放大、抗混疊低通濾波、ADG706 模擬開關(guān)、16 位ADC等組成的振動(dòng)信號(hào)采集電路,由FPGA 作為主控制芯片控制采集過(guò)程,將采集的數(shù)字量編幀、打包、緩存,并通過(guò)以太網(wǎng)發(fā)送至防護(hù)存儲(chǔ)器進(jìn)行數(shù)據(jù)存儲(chǔ)。實(shí)測(cè)表明,本文基于FPGA 的高精度振動(dòng)采集傳輸系統(tǒng),在單路采樣率為20kSPS、測(cè)量范圍為±2000g 時(shí),振動(dòng)信號(hào)的采集精度可達(dá)到±0.5%,滿足實(shí)際測(cè)量需求。

2 總體方案設(shè)計(jì)

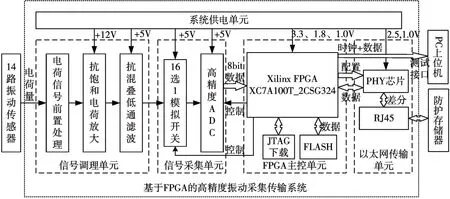

振動(dòng)信號(hào)采集傳輸系統(tǒng)的總體方案如圖1 所示,系統(tǒng)主要由信號(hào)調(diào)理單元、信號(hào)采集單元、FPGA主控單元、以太網(wǎng)傳輸單元、系統(tǒng)供電單元等模塊組成。信號(hào)調(diào)理單元將振動(dòng)傳感器輸出的電荷信號(hào)通過(guò)前置處理、抗飽和電荷放大及抗混疊低通濾波等電路進(jìn)行調(diào)理。信號(hào)采集單元通過(guò)模擬開關(guān)選通需要采集的通道,同時(shí)利用ADC 把該通道調(diào)理后的模擬電壓轉(zhuǎn)換為16 位數(shù)字信號(hào),F(xiàn)PGA 主控單元讀取ROM 表控制通道選擇、AD 轉(zhuǎn)換時(shí)序,將16 位數(shù)字量通過(guò)8 位數(shù)據(jù)線分時(shí)接收并緩存入內(nèi)部FIFO。以太網(wǎng)傳輸單元將FPGA 打包好的數(shù)據(jù)傳輸至防護(hù)存儲(chǔ)器,在測(cè)試階段PC 上位機(jī)可通過(guò)以太網(wǎng)接口接收數(shù)據(jù)并做分析。系統(tǒng)供電單元通過(guò)LDO 線性電源將輸入的15V 電壓轉(zhuǎn)換為12V,通過(guò)DC-DC 開關(guān)電源將輸入的5V 電壓轉(zhuǎn)換為3.3V、2.5V、1.8V、1.0V 為各模塊提供可靠穩(wěn)定的電源。

圖1 系統(tǒng)整體框架圖

3 硬件電路設(shè)計(jì)

3.1 振動(dòng)信號(hào)調(diào)理電路設(shè)計(jì)

本文采用PCB 公司的壓電式加速度傳感器357B03,量程為±2000g,靈敏度為10pC/g,則產(chǎn)生的電荷量為

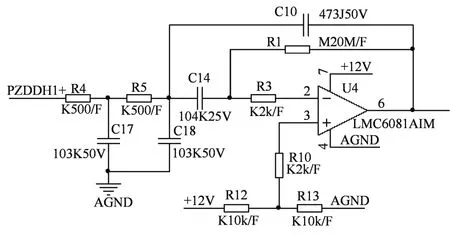

為了保證10 倍超量程不發(fā)生零漂現(xiàn)象,考慮冗余設(shè)計(jì),電荷量按200000pC 計(jì)算[6]。抗飽和電荷放大電路如圖2 所示,選用低輸入偏置電流的精密放大器LMC6081AIM,減少電荷的損失[7],該放大器使用+12V 供電,在正輸入端用兩個(gè)100kΩ電阻分壓,輸入+6V直流偏置。

圖2 抗飽和電荷放大電路

綜合考慮電荷放大電路的噪聲、漂移和下限頻率,選取電阻R1值為20MΩ,反饋電容C10選用容值穩(wěn)定性高的多層片式瓷介電容,電容值選為47nF[8]。

在采集過(guò)程中,如果噪聲信號(hào)頻率f大于等于振動(dòng)信號(hào)采樣頻率fS的一半,噪聲信號(hào)就會(huì)混疊到振動(dòng)信號(hào)中[9]。為了避免混疊現(xiàn)象的發(fā)生,本文使用八階抗混疊濾波芯片MAX7400。

MAX7400 可選擇用外部或內(nèi)部時(shí)鐘來(lái)驅(qū)動(dòng)電路,本設(shè)計(jì)采用內(nèi)部時(shí)鐘驅(qū)動(dòng),電路如圖3 所示,通過(guò)設(shè)置連接CLK 引腳的電容C21和C16的容值,將截止頻率設(shè)置為6.66kHz。截止頻率和電容容值的關(guān)系如下:

圖3 抗混疊低通濾波電路

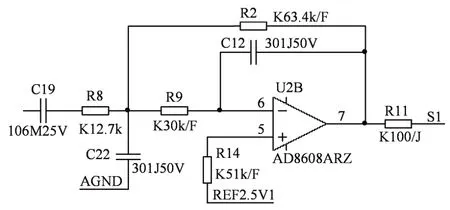

在調(diào)理電路末端使用二階無(wú)限增益多路反饋低通濾波電路,目的是平滑開關(guān)濾波同時(shí)實(shí)現(xiàn)電壓放大。如圖4所示,通過(guò)調(diào)整電阻R2與R8的比值來(lái)設(shè)置信號(hào)的放大倍數(shù),運(yùn)放AD8608 的偏置電壓設(shè)計(jì)為2.5V,放大后的交流信號(hào)幅值約為±2.08V,調(diào)理電路最終輸出為0.42V~4.58V。

圖4 二階無(wú)限增益多路反饋低通濾波電路

3.2 AD轉(zhuǎn)換電路設(shè)計(jì)

AD轉(zhuǎn)換芯片選用ADI公司的S AR型模數(shù)轉(zhuǎn)換器AD7667,該芯片是一款高速16 位分辨率的ADC,最高采樣率為1MSPS[10]。AD7667 模數(shù)轉(zhuǎn)換電路如圖5 所示,由于AD7667 模擬輸入電壓變化范圍為0~2.5V,而調(diào)理后的振動(dòng)信號(hào)為0.42V~4.58V,所以在輸入端電阻R183和R185分壓將信號(hào)幅值調(diào)至0.21V~2.29V。

圖5 AD7667模數(shù)轉(zhuǎn)換電路

為了快速補(bǔ)充模數(shù)轉(zhuǎn)換時(shí)消耗的能量,在ADC輸入引腳與參考地之間加入電容C210,容值為2.7nF;同時(shí)為了避免電容在充放電過(guò)程中引起的信號(hào)振蕩,設(shè)置電阻R184進(jìn)行隔離,阻值設(shè)置為15Ω。C210與R184構(gòu)成一階低通濾波器,截止頻率f0=1/2πRC=3.99MHz,能夠抑制帶外高頻噪聲,保證AD7667的高信噪比。

FPGA 通過(guò)驅(qū)動(dòng)CNVST 引腳來(lái)啟動(dòng)AD 轉(zhuǎn)換,驅(qū)動(dòng)CS 和RD 來(lái)使能總線接口,驅(qū)動(dòng)BYTE 來(lái)控制高低8 位字節(jié)的輸出,通過(guò)字節(jié)的分時(shí)輸出可以簡(jiǎn)化線路。

3.3 以太網(wǎng)接口電路設(shè)計(jì)

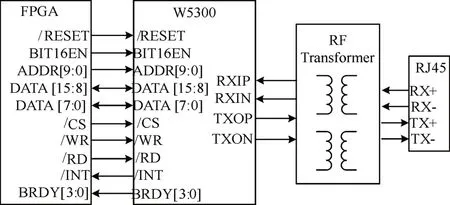

以太網(wǎng)接口用于將FPGA 編幀打包后的數(shù)據(jù)傳輸至防護(hù)存儲(chǔ)器或上位機(jī)進(jìn)行儲(chǔ)存。設(shè)計(jì)選用W5300 百兆以太網(wǎng)芯片,如圖6 所示,F(xiàn)PGA 的I/O口分別與W5300 的16 位數(shù)據(jù)接口、10 位地址接口及控制接口相連接,F(xiàn)PGA 通過(guò)寄存器尋址方式訪問(wèn)W5300。

圖6 以太網(wǎng)接口電路框圖

在RJ45接口與W5300信號(hào)輸出端之間增加隔離變壓器,可將W5300 發(fā)送的差分信號(hào)進(jìn)行線圈耦合濾波后,起到增強(qiáng)信號(hào)的作用,同時(shí)能夠抑制阻帶信號(hào)的傳輸,增強(qiáng)抗干擾能力[11]。

4 FPGA關(guān)鍵邏輯設(shè)計(jì)

4.1 FPGA頂層邏輯設(shè)計(jì)

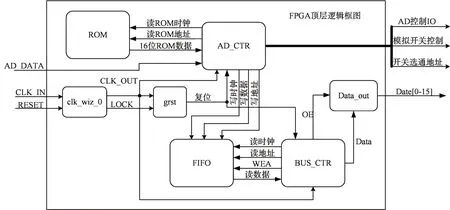

如圖7 所示,F(xiàn)PGA 內(nèi)部主要由AD 控制模塊、總線控制模塊、時(shí)鐘模塊、ROM、異步FIFO 等組成。輸入端為時(shí)鐘、AD采集數(shù)據(jù)以及復(fù)位,輸出端為16位數(shù)據(jù)輸出、AD控制IO、模擬開關(guān)控制IO、開關(guān)選通地址。

圖7 采集傳輸系統(tǒng)FPGA邏輯框圖

時(shí)鐘模塊使用FPGA 內(nèi)部IP 核Clocking wizard,時(shí)鐘模塊配置為MMCM(混合模式時(shí)鐘管理)模式,有效對(duì)外部輸入的40M 時(shí)鐘進(jìn)行去抖動(dòng)、去偏斜。ROM 和異步FIFO 均使用IP 核Block Memory Generator 實(shí)現(xiàn),其中ROM 設(shè)置為單端口ROM、寬度8 位、深度1024,加載入預(yù)先寫好的初始化文件;異步FIFO 設(shè)置為雙端口、寬度8 位、深度2048,這里讀速度>寫速度,F(xiàn)IFO 達(dá)到半滿狀態(tài)數(shù)據(jù)被讀走。

在采集時(shí)序的設(shè)定下,AD 控制模塊向ROM 發(fā)送讀時(shí)鐘、讀地址,依次循環(huán)讀取ROM 中數(shù)據(jù),讀取的16 位數(shù)據(jù)賦值給AD 轉(zhuǎn)換器控制引腳、模擬開關(guān)控制引腳、模擬開關(guān)選通地址來(lái)控制AD 轉(zhuǎn)換器和模擬開關(guān)完成所有通道振動(dòng)數(shù)據(jù)的采集。同時(shí),AD 控制模塊將AD 轉(zhuǎn)換后的數(shù)據(jù)寫入異步FIFO,并將寫地址發(fā)送至總線控制模塊,作為總線控制模塊判斷FIFO 半滿的依據(jù)。總線控制模塊將寫地址與讀地址做差,若差值?≥1024 達(dá)到半滿狀態(tài),則開始以1MB/s 的速率讀出數(shù)據(jù),將數(shù)據(jù)傳輸至數(shù)據(jù)總線。

4.2 采樣時(shí)序設(shè)計(jì)

數(shù)據(jù)采集過(guò)程的可靠性,需要設(shè)計(jì)合理的幀格式及采集時(shí)序,采集過(guò)程要嚴(yán)格按照幀格式和采集時(shí)序規(guī)定的順序?qū)斎胄盘?hào)進(jìn)行均勻采樣。

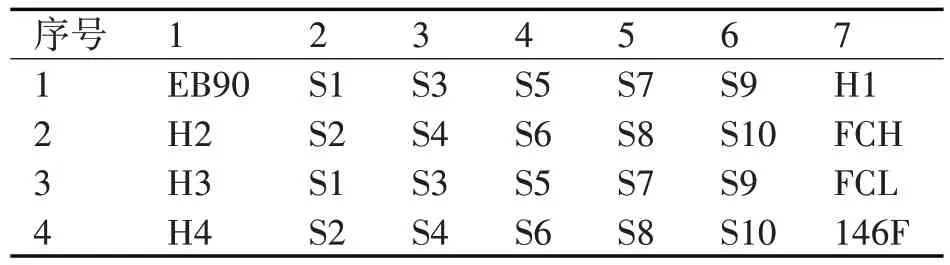

本文的采集系統(tǒng)共對(duì)14 路振動(dòng)信號(hào)進(jìn)行采集,S1~S10 為10 路采樣率為20kHz 的高頻振動(dòng),H1~H4 為4 路采樣率為10kHz 熱顫振。14 路采樣通道的總采樣率為240kSPS,由于數(shù)據(jù)幀需要添加幀頭幀尾以及幀計(jì)數(shù),所以采集系統(tǒng)的總采樣率為280kSPS。數(shù)據(jù)幀格式如表1 所示,可以看出在幀頭EB90 與幀尾146F 之間,每個(gè)采樣通道的采樣點(diǎn)都是均勻分布的,實(shí)現(xiàn)了對(duì)各通道均勻采樣。采樣通道的切換通過(guò)讀取ROM 表的方式,按照幀格式將切換邏輯進(jìn)行16進(jìn)制編碼后存儲(chǔ)于ROM中,F(xiàn)PGA控制讀地址遞增依次讀取ROM表中的值。

表1 采集數(shù)據(jù)幀格式

采集系統(tǒng)總采樣率為280kSPS,則每個(gè)通道的最大采樣時(shí)間為

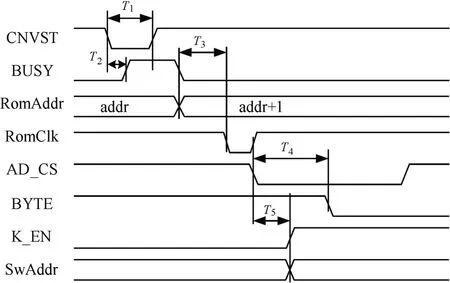

如圖8 所示為采樣控制邏輯時(shí)序圖。在一個(gè)采集周期中,CNVST 信號(hào)首先拉低啟動(dòng)模數(shù)轉(zhuǎn)換,保持T1(≥10ns)時(shí)間后拉高[12],在CNVST 拉低延遲T2時(shí)間后BUSY 信號(hào)拉高表示數(shù)據(jù)正在被處理。當(dāng)檢測(cè)到BUSY 信號(hào)的下降沿時(shí),表明數(shù)據(jù)已轉(zhuǎn)換完成發(fā)送至輸出端口寄存器,同時(shí)ROM 讀地址加1,為下一次轉(zhuǎn)換做準(zhǔn)備。

圖8 采樣控制邏輯時(shí)序圖

RomAddr 保持T3時(shí)間后,ROM 讀時(shí)鐘拉低將該地址存放的數(shù)據(jù)讀走,F(xiàn)PGA 將部分?jǐn)?shù)據(jù)位賦值給AD_CS完成AD轉(zhuǎn)換器片選,間隔T5時(shí)間后模擬開關(guān)使能信號(hào)K_EN 以及切換地址SwAddr 被賦值。BYTE 初始為高電平在AD_CS 拉低T4時(shí)間后變?yōu)榈碗娖剑ㄟ^(guò)高低電平的切換控制AD 轉(zhuǎn)換器輸出高8位與低8位數(shù)據(jù)。

5 測(cè)試結(jié)果

5.1 采集精度測(cè)試

為了測(cè)試系統(tǒng)采樣的精度,本測(cè)試使用高精度電荷源向輸入頻率1kHz、不同幅值的正弦電荷信號(hào),將某一路采集數(shù)據(jù)的分層值與電荷量進(jìn)行最小二乘法數(shù)據(jù)擬合,如圖9所示為數(shù)據(jù)擬合曲線。

圖9 數(shù)據(jù)擬合曲線

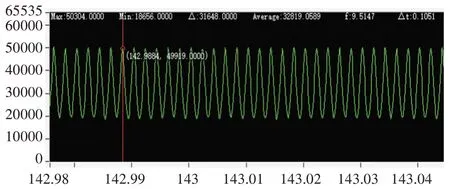

擬合公式為Y=AX+B,其中X 為數(shù)字量分層值,Y 為電荷量,將擬合后得到的斜率A=0.30179、截距B=-10302 輸入上位機(jī)繪圖軟件。如圖10 所示,軟件依據(jù)采集數(shù)據(jù)分層值可得振動(dòng)波形圖。

圖10 振動(dòng)波形圖

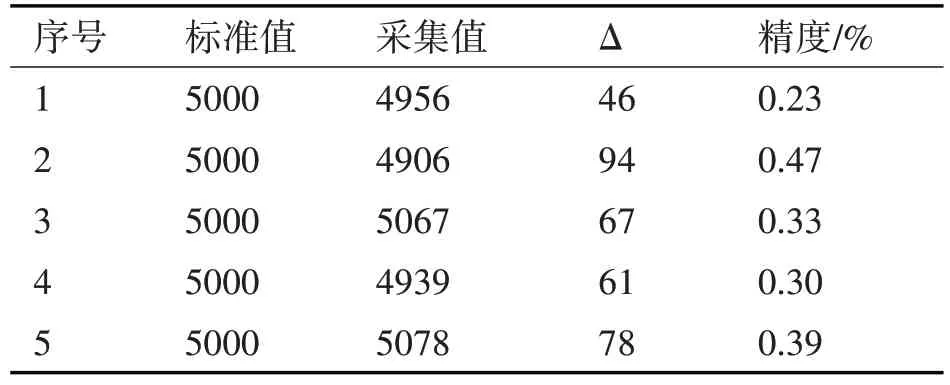

選取振動(dòng)波形圖中5 個(gè)波峰值,分別與標(biāo)準(zhǔn)輸入波峰值作差為Δ,如表2所示,選取最大的Δ值,根據(jù)式(3)計(jì)算得振動(dòng)2000g 滿量程情況下采集精度在±0.5%之內(nèi),優(yōu)于設(shè)計(jì)要求。

表2 振動(dòng)信號(hào)采集數(shù)據(jù)

5.2 數(shù)據(jù)可靠性驗(yàn)證

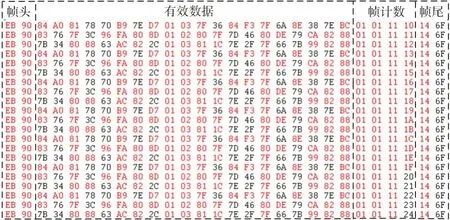

數(shù)據(jù)幀的可靠性是采集系統(tǒng)穩(wěn)定可靠的關(guān)鍵,為了確保數(shù)據(jù)在編幀、打包、傳輸各環(huán)節(jié)的正確性,需對(duì)數(shù)據(jù)進(jìn)行幀格式驗(yàn)證、誤碼率檢查。圖11 為采集系統(tǒng)解包后的部分?jǐn)?shù)據(jù)幀結(jié)構(gòu)。

圖11 解包后數(shù)據(jù)幀結(jié)構(gòu)

由圖11 原始數(shù)據(jù)可知,幀頭標(biāo)識(shí)為EB90、幀尾標(biāo)識(shí)為146F、幀計(jì)數(shù)逐一遞增、有效數(shù)據(jù)位數(shù)正確,通過(guò)調(diào)整數(shù)據(jù)幀的顯示參數(shù),使幀頭對(duì)齊可以快速判斷是否存在多數(shù)與少數(shù)的情況。此外,通過(guò)上位機(jī)軟件數(shù)據(jù)校驗(yàn)未發(fā)現(xiàn)多數(shù)與少數(shù)。

FPGA 內(nèi)部產(chǎn)生遞增數(shù)并向外發(fā)送,通過(guò)上位機(jī)接收并檢驗(yàn)遞增數(shù)的正確性來(lái)判斷。

6 結(jié)語(yǔ)

為了滿足飛行器飛行過(guò)程中的振動(dòng)監(jiān)測(cè)需求,本文設(shè)計(jì)了一種基于FPGA 的高精度振動(dòng)采集傳輸系統(tǒng),完成了14 路振動(dòng)信號(hào)的采集。在采樣率20kSPS、滿量程±2000g 條件下,采集精度優(yōu)于±0.5%,并對(duì)數(shù)據(jù)的可靠性進(jìn)行了驗(yàn)證。目前,該系統(tǒng)已成功應(yīng)用于某飛行器飛行試驗(yàn),工作性能穩(wěn)定。