基于SDR 的FPGA 加速MⅠMO 通信系統設計

全清華

(中車株洲電力機車研究所有限公司,湖南 株洲 412000)

0 引 言

在當今日益發展的通信領域,多進多出(Multiple-Input and Multiple-Output,MIMO)技術作為一種有效提高通信系統性能的手段,引起廣泛關注[1-2]。為滿足高容量、高速率、低時延等通信需求,研究者們不斷研究與優化MIMO 系統。軟件定義無線電(Software Defined Radio,SDR)技術作為一種靈活、可配置的通信平臺,為MIMO 系統的設計與實現提供全新的可能性[3-4]。該背景下,文章聚焦于基于SDR的現場可編程門陣列(Field Programmable Gate Array,FPGA)加速的MIMO 通信系統設計,以探討其在提高通信系統性能方面的潛在優勢。

1 系統架構

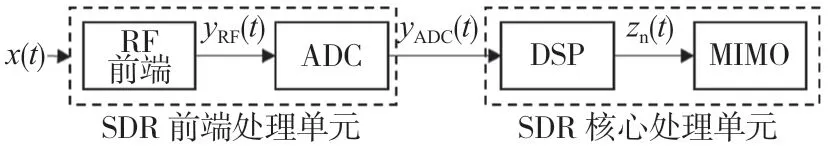

文章設計的基于SDR 的FPGA 加速的MIMO 通信系統的總體結構,如圖1 所示。圖1 結構包括SDR 前端處理單元、SDR 核心處理單元、FPGA 加速單元以及MIMO 后端處理單元[5]。SDR 前端處理單元負責射頻信號的接收和發射,通過模擬數字轉換器(Analog to Digital Converter,ADC)或數字模擬轉換器(Digital to Analog Converter,DAC)將射頻信號轉換為數字信號或從中頻信號還原為射頻信號。SDR 核心處理單元包括數字信號處理(Digital Signal Processing,DSP)和MIMO 信號處理算法,用于信號的處理、濾波、解調,并實施MIMO 技術。FPGA 加速單元包括MIMO 算法加速器和并行計算單元,通過硬件加速提高系統的實時性和處理速度。MIMO 后端處理單元包括DAC/RF 后端和射頻后端,負責將數字信號轉換為模擬信號,并進行射頻信號調制和解調,與其他通信設備無縫連接。

圖1 系統架構設計

2 基于SDR 的信號轉換與處理方法

SDR 前端處理單元和SDR 核心處理單元在射頻信號接收、數字信號處理及MIMO 信號處理方面的交互關系如圖2 所示。

圖2 SDR 的基本原理

設射頻信號為x(t),經過RF 前端后為yRF(t),經過ADC 轉換得到數字信號為yADC(t),該過程用公式表示為

SDR 核心處理單元包括DSP 和MIMO 信號處理算法,其數學描述如下:設數字信號為y(n),DSP 模塊進行信號處理、濾波及解調,得到處理后的信號z(n)。同時,MIMO 信號處理算法處理輸入信號,包括信號分離、合并等操作,得到MIMO 系統的輸出信號為

3 基于FPGA 的MIMO 系統設計

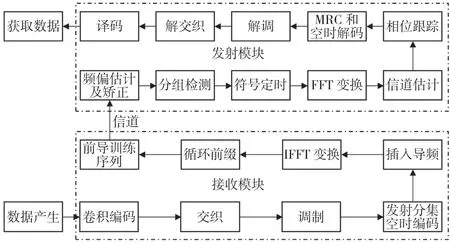

文章設計的基于FPGA的MIMO系統如圖3所示,由發射模塊和接收模塊2 個部分組成。

圖3 MⅠMO 通信系統

發射機中,數據產生模塊對原始數據進行編碼,編碼后的數據通過卷積模塊進行卷積,生成發送天線的調制符號。調制符號經交織模塊進行交織,以提升系統的抗干擾性。交織后的調制符號經空時編碼模塊進行空時編碼,以提高系統的空間復用增益。空時編碼后的調制符號經發射分集模塊進行發射分集,以提升系統的抗衰落性。發射分集后的調制符號經快速傅里葉逆變換模塊進行快速傅里葉逆變換,生成射頻信號。射頻信號通過加前導訓練序列模塊插入前導訓練序列,協助接收機進行信道估計。

接收機中,接收天線接收射頻信號后,信道模塊進行信道估計。信道估計后的信號經快速傅里葉變換模塊進行快速傅里葉變換,分離導頻和數據符號。導頻和數據符號經過頻偏估計模塊進行頻偏估計,消除信號在信道中的頻偏。頻偏估計后的數據符號通過定時估計模塊確定數據符號的采樣時刻后,再經解交織模塊進行解交織。解交織后的數據符號通過解調模塊進行解調,恢復為原始數據,再通過接收分集模塊進行接收分集,提升系統的抗衰落性。接收分集后的原始數據通過空時解碼模塊進行空時解碼,提高系統的空間復用增益。空時解碼后的原始數據通過譯碼模塊進行譯碼,消除編碼過程中引入的錯誤。

在具體技術實現方面,發射機采用D-BLAST技術,接收機應用最大比合并(Maximum Ratio Combining,MRC)技術。在信道估計方面,采用基于最小均方算法(Least Mean Square,LMS)算法的方法。

D-BLAST 技術是一種基于層次分解的空時編碼技術。其核心思想是通過分層處理,將多個天線的信號分解為多個獨立的數據流,從而提高系統的空間復用增益。設有Nt個天線的發射機,對應的信號向量為,通過空時編碼矩陣進行編碼,產生Nt個獨立的調制符號。接收機的信道矩陣為,其中Nr為接收天線數。接收信號向量可表示為

式中:n為加性高斯白噪聲,是與y維度相同的向量。通過使用MRC 技術,接收機可以優化對每個獨立數據流的解調過程。

MRC 技術是一種基于最大似然估計的接收分集技術,其基本原理是最大化接收信號與其估計之間的信噪比。設接收到的信號向量為,對應的發射信號向量為,則通過對信道矩陣hiH和s進行內積運算,可以得到每個天線上的接收信號向量為

式中:hi為接收信號經過第i個天線的信道;ni為對應的噪聲,是與yi維度相同的向量。最終,MRC 技術通過選擇合適的權重系數,將各個天線上的信號合并,從而最大化整體信噪比。

LMS 算法是一種迭代更新權重的算法,用于實現自適應濾波。在信道估計中,假設真實信道矩陣為Htrue,估計信道矩陣為Hest。通過最小化估計誤差的均方誤差,LMS 算法的更新規則可以表示為

式中:μ為步長參數;r(n)為估計誤差向量;sH表示s的共軛轉置。LMS 算法通過迭代優化權重矩陣,逐步逼近真實信道矩陣,從而實現準確的信道估計。

4 系統仿真與分析

為驗證所提方法的正確性,文章在MATLAB 中進行基于SDR 的FPGA 加速的MIMO 通信系統設計仿真,主要包括SDR 硬件支持包的安裝、SDR 設備連接、MATLAB 腳本的編寫、FPGA 加速部分的模擬以及性能評估結果可視化。文章從誤碼率(Symbol Error Rate,SER)的角度評估并對比行基于SDR 的FPGA 加速的MIMO 通信系統(以下簡稱文章設計系統)方法和基于SDR 的MIMO 系統(以下簡稱SDR系統),測試結果如圖4 所示。

圖4 系統仿真結果的誤碼率

圖4 結果表明:在低信噪比(0 ~22 dB)下,文章設計系統和SDR 系統2 條曲線的誤碼率差距相對較小,表明系統在較差的信道條件下仍然能夠提供良好的通信性能;在高信噪比(22 ~30 dB)下,文章設計系統的誤碼率顯著低于SDR 系統,這可能說明文章設計系統中SDR 和FPGA 的結合在高信噪比環境中的確切效益。這種性能差異可能是由于FPGA加速技術在復雜信號處理任務上的優勢所致。由此表明,與SDR 系統相比,文章設計系統在高信噪比下具有更好的性能,誤碼率更低。這種性能差異可能源于系統中引入FPGA 加速技術,提高系統在高信噪比情況下的處理效率和性能。

5 結 論

文章綜合應用SDR 和FPGA 技術,深入研究MIMO 通信系統的設計與優化。在總體架構設計方面,構建通用性系統,可以提高系統的適應性和可維護性。通過SDR 的信號轉換與處理方法,系統能夠有效適應不同信道條件和通信標準。引入FPGA 加速技術后,提升系統的實時性和處理速度。在理論分析方面,對提出的方法進行深入討論,揭示系統的性能優勢。文章的研究為未來MIMO 通信系統設計提供有益的思路和方法,為提高通信系統性能和應對不斷發展的通信需求提供了創新性的解決途徑。