一種面向工程仿真應用的SoC平臺設計

王彬 于哲 趙子龍

摘要: 傳統系統級芯片(system on chip,SoC) 仿真多數基于含有硬核中央處理器(central processingunit,CPU)的現場可編程邏輯門陣列(field programmable gate array,FPGA)平臺,這使得數字芯片設計者在工程設計與仿真過程中缺乏對底層數據邏輯以及與其緊密關聯的系統應用的深刻理解。針對該問題,設計了一種面向工程仿真應用的SoC 平臺。該平臺基于國產CPU 處理器和高級微控制器總線架構(advanced microcontroller bus architecture,AMBA),預留了擴展設計所需的高級高性能總線(advanced highperformance bus,AHB)和外圍總線(advanced peripheral bus,APB)接口,設計了CPU 向通用異步收發器(universal asynchronous receiver/transmitter,UART)寫入串口數據的測試用例。結果表明,該平臺通過了仿真驗證,可滿足數字芯片設計所涉及的嵌入式開發、數字前端設計、模塊功能仿真等工程實踐教研需求。

關鍵詞:SoC;仿真驗證;AMBA 總線;串口

中圖分類號:TN47;TP368 文獻標識碼:A

0 引言

隨著集成電路制造工藝的發展,系統級芯片(system on chip,SoC)能夠集成更多數量和種類的器件。SoC 設計應該是一個軟件和硬件協同設計的過程,然而傳統的集成電路設計方法一般都是將系統分為軟件開發和硬件電路設計兩個部分[1]。目前,SoC 設計相關的工程實踐主要是基于包括硬核處理器在內的現場可編程邏輯門陣列(fieldprogrammable gate array,FPGA)平臺(如XILINX公司的ZYNQ 系列FPGA)的嵌入式開發和數字硬件電路設計,或將含有硬核中央處理器(centralprocessing unit,CPU) 的FPGA 作為原型驗證的平臺進行SoC 的系統驗證[2-5],或基于SoC 芯片開展相關應用設計等[6],這些設計方式導致設計者對底層邏輯電路與上層系統應用的理解不夠系統和深刻。

本文設計了一種面向工程仿真應用的SoC 平臺,該平臺層次清晰、結構完整,支持高級高性能總線(advanced high performance bus,AHB)和外圍總線(advanced peripheral bus,APB) 的模塊擴展,以及基于國產CPU 的系統級嵌入式開發;結合相關電子設計自動化(electronic designautomation,EDA)工具、工藝庫文件,可滿足從前端設計仿真到后端綜合布線、基于SoC 的嵌入式開發等工程實踐需求。

1 平臺架構設計

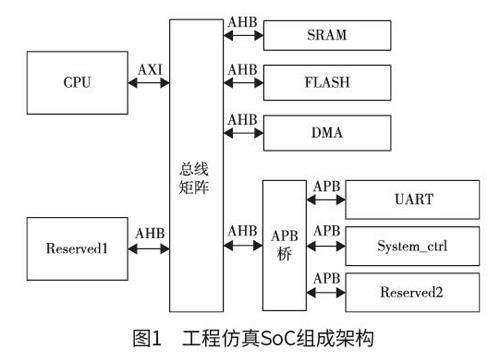

圖1 為工程仿真SoC 組成架構。其中,CPU 通過高級可擴展接口(advanced eXtensible interface,AXI)接入總線矩陣;靜態隨機存取存儲器(staticrandom access memory, SRAM)、閃存(FLASH)、直接內存訪問(direct memory access,DMA)、預留1(Reserved1)和APB 橋通過AHB 接口接入總線矩陣;而通用異步收發器(universal asynchronousreceiver /transmitter,UART )、系統控制(systemcontrol,System_ctrl) 和預留2(Reserved2) 接入APB 橋的APB 接口。

其中,CPU 為國產CPU 處理器IP 核,是SoC的核心處理器;總線矩陣為多個SoC 總線組成的矩陣,包括AXI、AHB、APB 等多種類型的多個接口;SRAM 為系統的運行內存,CPU 可完成對SRAM 的高速讀寫操作,同時為CPU 的高速運行提供高速訪問的存儲空間;FLASH 模塊為FLASH控制器模塊,可以完成對片外FLASH 存儲器的讀寫操作,從而在SoC 啟動階段從FLASH 中讀取BOOTLoader 文件和用戶程序,或是在DMA 控制下從FLASH 中搬移程序到SRAM;DMA 用來執行存儲器與存儲器之間,以及存儲器與模塊之間的數據搬運,以避免因大量數據的搬運而占用過多的CPU 資源;Reserved1、Reserved2 分別為預留的AHB、APB 接口模塊,工程實踐過程中可按需設計相應的功能模塊并接入SoC 系統進行系統級的仿真。

2 地址映射

通過IP 核的復用和相應功能模塊的設計, 可較快地完成SoC 的集成設計。而在各IP 核進行系統集成之前, 還需要完成相應的參數配置和地址分配。該地址分配是需要對SoC 系統架構中各功能模塊進行地址空間分配。例如, System_ctrl 被分配的地址映射范圍為0x0200_0000 ~ 0x0200_0FFF, UART 被分配的地址映射范圍為0x0200_4000 ~ 0x0200_4FFF。CPU可通過對特定地址映射范圍的寄存器進行讀寫訪問,實現對相應功能模塊的控制。

在本設計中,CPU、總線矩陣、SRAM、FLASH、DMA 和APB 橋等模塊均選用現有IP 核,UART 和System_ctrl 為自主設計的功能模塊。通過地址映射空間的分配,完成對上述IP 核以及設計的功能模塊分配地址映射空間。各模塊IP 完成配置后集成到總線矩陣上。編寫CPU 向UART 寫數據的測試用例源文件,將其命名為cpu_write_uart.c文件;該源文件為用戶程序的Main 函數的一個子函數。整個CPU 用戶程序的源函數通過編譯后生成可執行BIN 文件,將該可執行文件作為FLASH模塊讀取的參數文件,CPU 在BOOTLoader 啟動后,即可讀取用戶程序的可執行文件。

3 仿真驗證

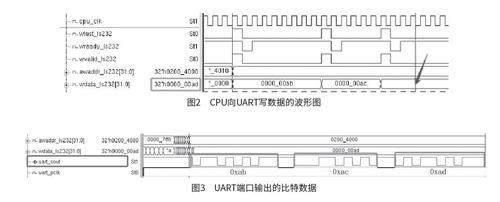

SoC 仿真平臺搭建完成后,進行嵌入式軟件的測試。以CPU 向UART 串口寫3 個字節的數據0xab、0xac、0xad 為例,在基于國產CPU 開發的C 程序的Main 函數中, 添加CPU 寫UART 的函數;然后執行編譯生成可執行文件cpu_write_uart.hex;將上述可執行文件作為Flash 模型讀取參數的目標文件,從而在仿真過程中實現對用戶程序的加載[7-8]。圖2 為CPU 向UART 寫數據的波形圖。其中,CPU 通過AXI 總線向地址為32h0200_4000 的UART 寄存器分別依次寫入了0xab、0xac 和0xad;uart_sout 端口依次輸出了串行比特值0xab、0xac 和0xad。其中,UART 波特率設置為115 200,格式為“起始位‘0+8 位數據+1 位校驗位”,校驗方式為偶校驗,且當字節數據在串行發送比特流時,發送比特的順序是從字節數據的低比特位到高比特位。例如,一個字節寬度的數據DATA[7:0],在UART串口發送時先發送DATA[0] 而最后發送DATA[7]。如圖3 所示,0xab 轉換為二進制是“1010_1011”,轉換為UART 串口發送時,加上起始位“0”和最后的校驗位“1”, 所以轉換為比特流時為“0_1101_0101_1”; 采用同樣的方法可以驗證UART 串口收到的數據為0xac、0xad,與CPU 寫入的數據一致,從而驗證了SoC 設計功能的正確性。

4 結論

本文設計了一種面向工程仿真應用的SoC 平臺,預留了擴展接口,設計了測試用例并通過了仿真驗證。該平臺在工程領域具有代表性,貼近工程實際且相關內容深入淺出,可操作性強,能夠為集成電路工程、微電子等相關領域提供嵌入式設計、數字集成電路(integrated circuit,IC)設計、系統集成與功能仿真等工程實踐平臺與參考樣例,為培養工程實踐能力強的專業人才提供借鑒。

參考文獻

[1] 郭煒,魏繼增,郭箏,等. SoC 設計方法與實現[M].3 版. 北京:電子工業出版社,2017:10-12.

[2] 楊昕欣,姚遠,刁為民,等. 面向工程教育的SoC嵌入式系統實驗平臺設計與教學實踐[J]. 中國現代教育裝備,2018(3):22-24.

[3] 高俊楓,黃樂天,胡慶. 嵌入式系統“FPGA+SoC”實踐教學體系內容重構[J]. 高等工程教育研究,2024(1):73-77.

[4] 張劍賢,吳文華,劉錦輝,等. 基于FPGA 的8 位SoC 微體系結構設計[J]. 計算機教育,2020(3):31-35.

[5] 鄧睿,余宏,莫章潔,等. 基于SOC 技術的微機原理實驗課程教學改革探索[J]. 數字技術與應用,2023, 41(4):21-23.

[6] 江志東, 霍立平, 張弟, 等. 基于SoC 芯片的1553B 總線仿真平臺設計與實現[J]. 電子設計工程,2020,28(24):152-157.

[7] 鄧睿,余宏,莫章潔,等. 基于Cortex_M3 內核的SoC 芯片軟硬件協同驗證平臺設計實現[J]. 數字技術與應用,2023,41(6):197-199.

[8] 朱文波,郭斌林. 一種有效的SOC 系統程序引導方法[J]. 杭州電子科技大學學報,2008,28(1):16-19.