面向多通道冗余系統(tǒng)的FPGA硬件脈沖同步方法研究

摘 要:提出一種基于現(xiàn)場(chǎng)可編程門陣列(FPGA)的硬件脈沖同步方法以保證冗余系統(tǒng)數(shù)據(jù)交互、任務(wù)調(diào)度的可靠性。以三通道冗余系統(tǒng)為例,每個(gè)通道都接收3個(gè)通道的脈沖信號(hào)輸入,對(duì)3個(gè)通道的脈沖信號(hào)進(jìn)行排序,確定主控通道的脈沖同步信號(hào);捕獲主控脈沖的信號(hào)邊沿,計(jì)算與另外兩個(gè)通道的同步偏差;設(shè)置不同粒度的調(diào)整區(qū)間,偏差大進(jìn)行多周期調(diào)整,偏差小則進(jìn)行單周期調(diào)整;建立基于FPGA的硬件脈沖同步仿真平臺(tái)并進(jìn)行測(cè)試分析。仿真結(jié)果表明:脈沖同步精度可達(dá)到20 ns,同步建立時(shí)間不超過470 ms,滿足了多通道冗余系統(tǒng)的同步需求。

關(guān)鍵詞:冗余;多通道;硬件同步;FPGA

中圖分類號(hào):V233.7文獻(xiàn)標(biāo)志碼:A文章編號(hào):1671-5276(2024)03-0010-05

Research on FPGA Hardware Pulse Synchronization Method for Multi-channel Redundant Systems

Abstract:A hardware pulse synchronization method based on field programmable gate array (FPGA) is proposed to ensure the reliability of data interaction and task scheduling of the redundant system. Taking the three-channel redundant system as an example, each channel receives pulse signal inputs from three channels, the pulse signals of the three channels are sorted to determine the pulse synchronization signal of the master channel. The signal edges of the master pulse are captured to compute the synchronization deviation from the other two channels. The adjustment intervals with different granularities are set with large deviations for multi-cycle adjustment and small deviations for single-cycle adjustment.The FPGA-based hardware pulse synchronization simulation platform is established and simulated. The simulation results show that the pulse synchronization accuracy can reach 20 ns, and the synchronization establishment time is no more than 470 ms, which meets the synchronization requirements of multi-channel redundant system.

Keywords:redundancy; multi-channel; hardware synchronization; FPGA

0 引言

冗余是容錯(cuò)控制的一種方法。容錯(cuò)控制的主要目的是當(dāng)系統(tǒng)發(fā)生故障時(shí),仍能保持控制目標(biāo)的能力[1]。容錯(cuò)控制已經(jīng)廣泛應(yīng)用于航空航天等要求高可靠性領(lǐng)域[2]。容錯(cuò)控制的關(guān)鍵因素之一在于冗余[3-4]。根據(jù)冗余信息的不同,冗余可分為硬件冗余和解析冗余[5]。硬件冗余將關(guān)鍵部件和易故障的部件進(jìn)行備份,有些可靠性需求高的系統(tǒng)會(huì)將整個(gè)控制系統(tǒng)都進(jìn)行備份[6]。本文基于硬件冗余進(jìn)行研究。硬件冗余要求硬件設(shè)備有多個(gè)備份,多個(gè)備份即多個(gè)通道,由于時(shí)鐘頻率等誤差導(dǎo)致通道間的行為也會(huì)有所不同。為了保證冗余的可靠性,各通道進(jìn)行切換時(shí)需要保證一定精度的時(shí)間同步,這就對(duì)通道間的同步提出了要求。同步在容錯(cuò)控制中起到重要作用[7]。

通道間同步技術(shù)是各通道在同一時(shí)間進(jìn)行相同任務(wù)調(diào)度的基礎(chǔ)。同步按照實(shí)現(xiàn)平臺(tái)的不同又可以分為軟件同步和硬件同步。LIU等[8]提出基于公共時(shí)鐘產(chǎn)生同步周期信號(hào),進(jìn)行通道數(shù)據(jù)交換比較、時(shí)間裕度計(jì)算完成系統(tǒng)同步和通信同步。ZHOU等[9]通過Petri網(wǎng)絡(luò)描述了三模冗余系統(tǒng)任務(wù)同步的模型,直觀地表達(dá)了任務(wù)同步的機(jī)制及過程。WANG等[10]設(shè)計(jì)了一種應(yīng)用于四余度的“雙握手”軟件同步方法。YANG等[11]提出了用于時(shí)鐘同步的過程彈性容錯(cuò)DLL設(shè)計(jì),采用動(dòng)態(tài)定時(shí)校正時(shí)鐘誤差,使三模冗余系統(tǒng)的時(shí)鐘相位誤差大大降低。

針對(duì)航電系統(tǒng)高同步精度和更短的同步時(shí)間需求,本文提出一種可應(yīng)用于多通道的基于現(xiàn)場(chǎng)可編程門陣列(field programmable gate array,F(xiàn)PGA)的硬件脈沖同步方法,以保證系統(tǒng)可靠性。

1 影響因素分析

本文基于多通道冗余分析同步的影響因素。分析由于FPGA啟動(dòng)時(shí)間、通道間時(shí)鐘不同步、布線時(shí)延問題而產(chǎn)生的通道間不同步。

1.1 上電啟動(dòng)不同步

為了避免共因失效,冗余系統(tǒng)雖然使用相同設(shè)計(jì),但是也會(huì)采用不同硬件,器件的差異導(dǎo)致了上電的不同步[12]。航電系統(tǒng)常用28V直流電源,經(jīng)過濾波、過壓保護(hù)等電路后,經(jīng)二次電源轉(zhuǎn)換為后級(jí)電路提供電源。由于轉(zhuǎn)換器件的差異,表現(xiàn)為上電上升時(shí)間的不同,整個(gè)控制系統(tǒng)的運(yùn)行時(shí)間會(huì)存在一個(gè)初始的偏差。

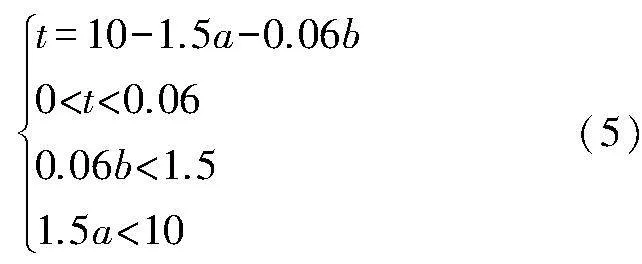

1.2 時(shí)鐘不同步

不同通道間采用相同頻率的不同時(shí)鐘源,由于時(shí)鐘源器件的不同以及本身帶有的誤差,其誤差經(jīng)過系統(tǒng)長(zhǎng)時(shí)間的運(yùn)行而累積成可以對(duì)系統(tǒng)時(shí)鐘造成影響的偏差,從而導(dǎo)致依賴于時(shí)鐘的系統(tǒng)任務(wù)的不同步,如圖1所示。

1.3 布線時(shí)延

電信號(hào)的傳輸速度取決于介質(zhì)的介電常數(shù),信號(hào)在PCB板中以有限的速度傳輸,從發(fā)送傳輸?shù)浇邮斩耍瑐鬏敃r(shí)間的延遲受到速度與走線長(zhǎng)度的影響。

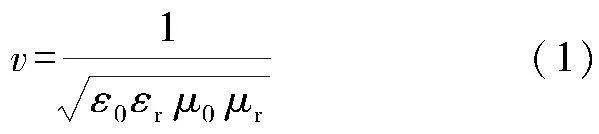

信號(hào)的傳輸速度v可由式(1)計(jì)算:

式中:ε0為自由空間的介電常數(shù),其值為8.89×10-12F/m;εr為材料的相對(duì)介電常數(shù);μ0為自由空間的導(dǎo)磁率,值為4π×10-7H/m;μr為材料的相對(duì)導(dǎo)磁率(幾乎所有的互連材料相對(duì)導(dǎo)磁率都為1)。空氣的相對(duì)介電常數(shù)和相對(duì)導(dǎo)磁率都為1,光在空氣中的速度約為0.304 8 m/ns,則

根據(jù)經(jīng)驗(yàn)法則,大多數(shù)聚合物的介電常數(shù)約為4,估算電路板中信號(hào)傳輸速度約為0.152 4m/ns,取其倒數(shù)作為傳輸時(shí)延的度量,即每米連線的時(shí)延為6.56ns。在信號(hào)遠(yuǎn)距離傳輸時(shí)需要考慮布線時(shí)延,將時(shí)間補(bǔ)償加入到設(shè)計(jì)中。

2 硬件同步方案設(shè)計(jì)及實(shí)現(xiàn)

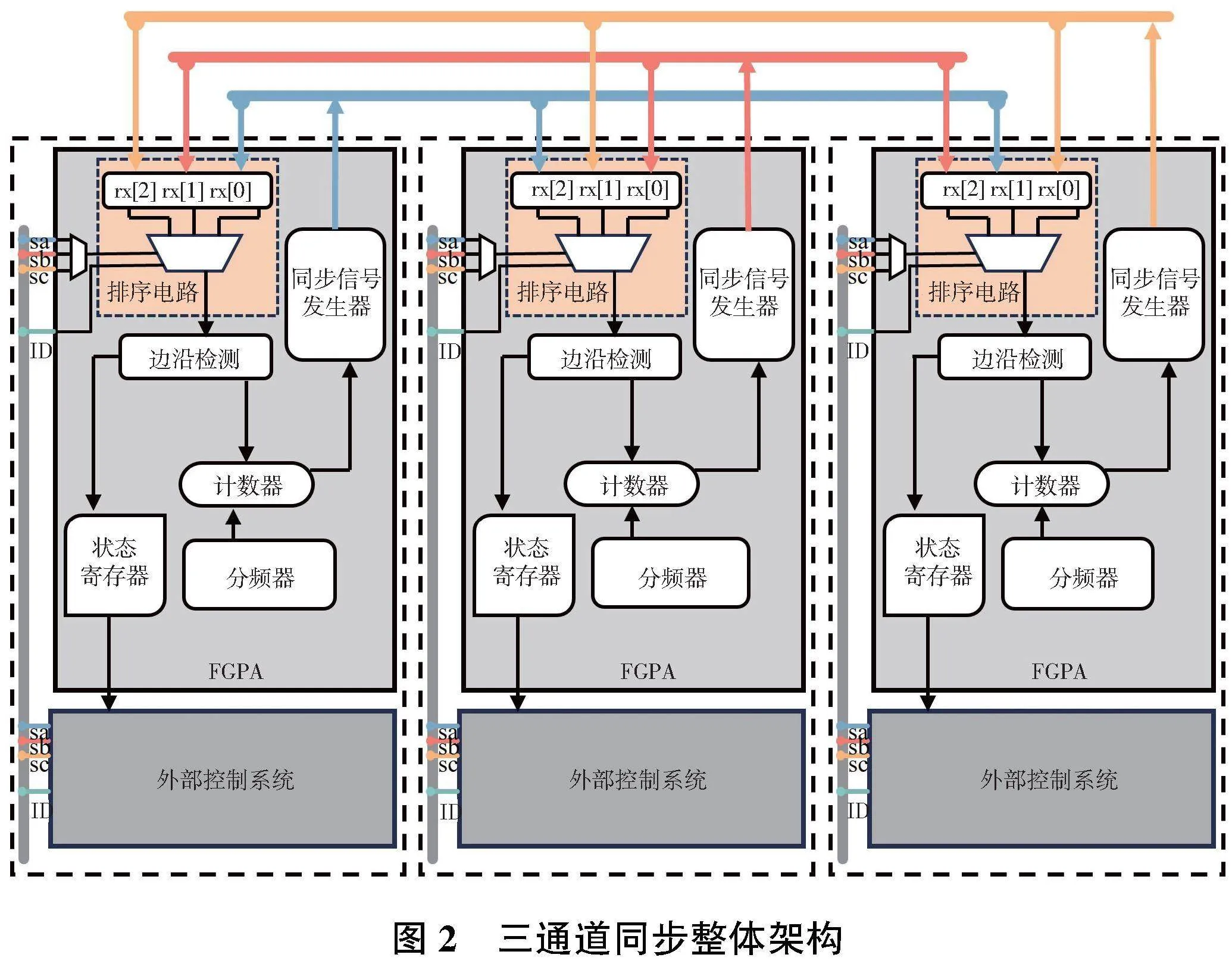

本文同步方案基于三通道進(jìn)行設(shè)計(jì),也可用于多通道系統(tǒng)。本方案A、B、C三通道冗余設(shè)計(jì),功能相同,由FPGA采用硬件的方式實(shí)現(xiàn)通道間任務(wù)的同步。A通道同步信號(hào)為主控時(shí),B通道、C通道同步信號(hào)跟隨A通道進(jìn)行同步校正;當(dāng)A通道出現(xiàn)故障時(shí),同步信號(hào)進(jìn)行切換,以B通道為主控,C通道跟隨B通道的同步信號(hào)。FPGA產(chǎn)生以同步周期為周期的中斷信號(hào)給外部控制系統(tǒng),實(shí)現(xiàn)三通道的同步功能,中斷信號(hào)的同步通過調(diào)整脈沖信號(hào)對(duì)齊來完成。

2.1 整體架構(gòu)

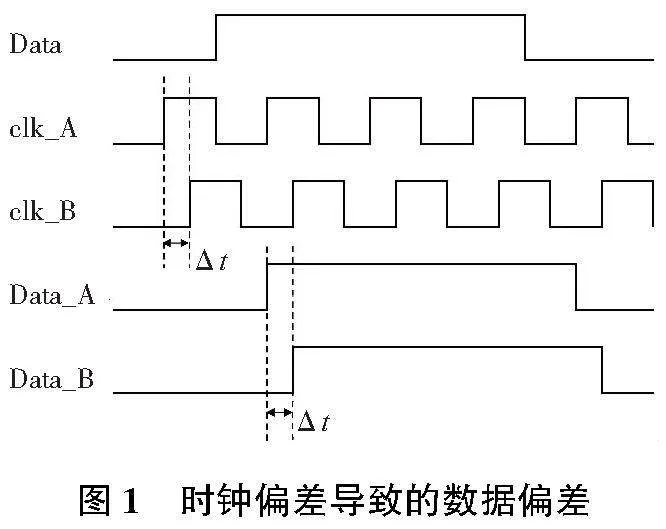

本方案的硬件同步電路及同步方法由FPGA實(shí)現(xiàn),架構(gòu)如圖2所示。通道內(nèi)FPGA包含排序電路、同步信號(hào)發(fā)生器、輸入處理、分頻器、計(jì)數(shù)器、狀態(tài)寄存器、中斷信號(hào)發(fā)生器,主要外部接口如表1所示。接口有3個(gè)同步脈沖輸入,包含了另外2個(gè)通道的同步脈沖以及本通道的脈沖信號(hào)返回輸入,返回輸入是為了能用更簡(jiǎn)潔的邏輯實(shí)現(xiàn)同步脈沖輸入的排序。

2.2 同步方案實(shí)現(xiàn)

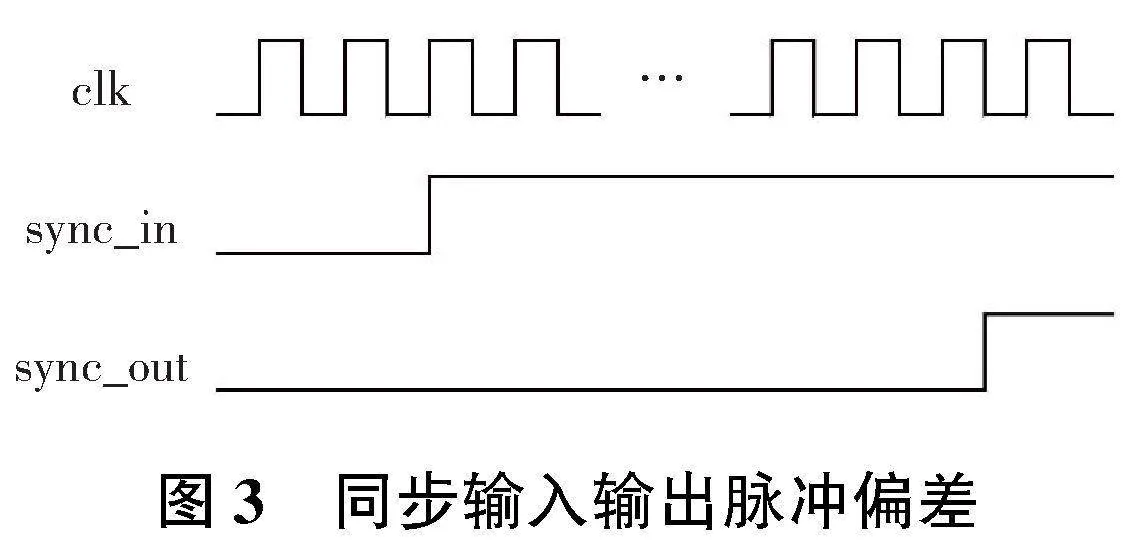

設(shè)定同步脈沖基準(zhǔn)周期50ms,采用周期調(diào)節(jié)方式,本通道同步脈沖落后于主控脈沖時(shí),增加本通道同步脈沖的周期(每周期的增加幅度取決于脈沖偏差),超前時(shí)減小周期。主控脈沖信號(hào)輸入本通道,與本通道輸出脈沖有偏差,如圖3所示。相位相差較大時(shí)采用多周期調(diào)節(jié),相位相差較小時(shí),采用單周期調(diào)節(jié)。調(diào)整范圍及周期取決于同步脈沖周期等,根據(jù)實(shí)際需求設(shè)定其值。

1)同步脈沖排序及主控脈沖獲取

當(dāng)B通道作為主控時(shí),A通道接收B通道的同步脈沖輸出并跟隨,在3個(gè)同步脈沖輸入f_sync_rx[0]、f_sync_rx[1]、f_sync_rx[2]中需要判斷出哪個(gè)信號(hào)來自于B通道。三輸入脈沖的連接順序如圖2中排序電路所示,本通道輸出脈沖返回硬線連接順序?yàn)?,即連接到f_sync_rx[0]對(duì)應(yīng)的引腳,按照1~N的數(shù)字順序循環(huán)連接,如本通道為B通道時(shí),f_sync_rx[0]連接本通道同步脈沖輸出返回,f_sync_rx[1] 連接C通道同步脈沖,按照循環(huán)順序連接,則f_sync_rx[2]連接A通道同步脈沖。然后將f_sync_rx[2∶0]根據(jù)通道標(biāo)識(shí)chnl_id按照實(shí)際的通道順序A、B、C進(jìn)行重排序,緩沖一級(jí),得到順序的同步脈沖輸入。

經(jīng)過排序后,還需要根據(jù)主/被控狀態(tài)信號(hào)判斷本通道的控制狀態(tài)以及主控通道號(hào),根據(jù)本通道ID確定主控同步信號(hào)的序號(hào)。

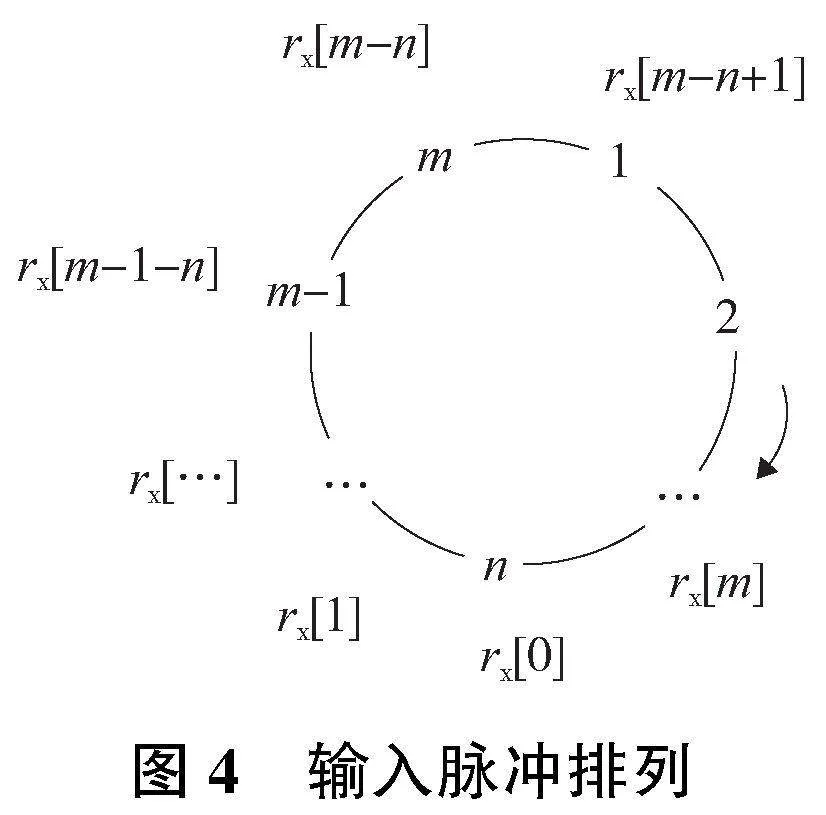

進(jìn)行通道擴(kuò)展時(shí),每通道輸入脈沖數(shù)量與通道數(shù)一致,輸入順序與上述三通道原理一致,本通道輸入脈沖硬線連接rx[0],正序排列,設(shè)共m個(gè)通道,本通道序號(hào)n,則本通道輸入脈沖連接rx[i]的順序如圖4所示。

2)方案實(shí)現(xiàn)

整個(gè)同步過程包括輸入處理、計(jì)數(shù)、狀態(tài)判斷、同步脈沖輸出等,具體實(shí)現(xiàn)如下。

a)sa、sb、sc確定主控/被控設(shè)備。

b)sa、sb、sc、chnl_id組合邏輯判斷同步使能信號(hào),當(dāng)沒有主控設(shè)備時(shí),同步不使能。

c)同步脈沖信號(hào)與本設(shè)備脈沖信號(hào)周期、寬度相同。同步脈沖信號(hào)在接收到本通道時(shí)需要進(jìn)行同步打拍、濾波、邊沿采集才能捕獲有效邊沿,本通道同步脈沖輸出時(shí)要把上述捕獲時(shí)間計(jì)算在內(nèi),這樣才可以保證捕獲的有效邊沿與發(fā)送通道起始相位一致,也可以避免毛刺信號(hào)和跨時(shí)鐘域帶來的亞穩(wěn)態(tài)。

d)脈沖同步實(shí)現(xiàn)。當(dāng)主/被設(shè)備同步脈沖上升沿時(shí)差滿足調(diào)整精度時(shí),判定主/被設(shè)備同步。否則,被控設(shè)備應(yīng)判斷與主設(shè)備之間的相位關(guān)系并通過漸進(jìn)式調(diào)節(jié)實(shí)現(xiàn)與主設(shè)備的同步。兩通道脈沖偏差應(yīng)保持在一定范圍內(nèi),若偏差過大,則認(rèn)為主/被控設(shè)備出現(xiàn)故障,不同步。

e)相位偏差計(jì)算。設(shè)A通道為主控通道,B通道為隨動(dòng)通道。A、B通道同步脈沖信號(hào)的偏差為

式中:l0為同步脈沖初始偏差;dB、dA為B、A通道的脈沖周期;dB每個(gè)周期會(huì)進(jìn)行調(diào)整,調(diào)整方式如下:

式中:dB[0]為B通道同步脈沖初始周期;sign(·)為符號(hào)函數(shù);lstep為每周期調(diào)節(jié)步長(zhǎng)。

接收主控脈沖時(shí),由于傳輸路徑和輸入處理,還需要將同步打拍、濾波等補(bǔ)償?shù)难舆t時(shí)間計(jì)算在內(nèi),且布線較長(zhǎng)時(shí),也要計(jì)算將布線時(shí)延。

f)調(diào)整策略。設(shè)置脈沖周期基準(zhǔn)為20ms,每個(gè)脈沖周期含有25個(gè)調(diào)整周期,則調(diào)整周期的基準(zhǔn)為0.8ms。調(diào)整單元是調(diào)整周期的基本組成單元,調(diào)整單元由時(shí)鐘分頻得到,分頻后時(shí)鐘頻率50MHz,則每個(gè)調(diào)整周期的調(diào)整精度為20ns。在本通道脈沖初始周期開始2個(gè)計(jì)數(shù)器分別計(jì)數(shù),單元計(jì)數(shù)器以50MHz為單位計(jì)數(shù),周期計(jì)數(shù)器以調(diào)整周期計(jì)數(shù),在檢測(cè)到同步源邊沿時(shí)2個(gè)計(jì)數(shù)器清零。根據(jù)檢測(cè)的邊沿所在的調(diào)整區(qū)間,將調(diào)整策略劃分為多周期調(diào)整、單周期調(diào)整和單元調(diào)整,多周期調(diào)整策略增加或減小每個(gè)周期時(shí)間,單周期策略增加或減小1個(gè)周期時(shí)間。單元調(diào)整在檢測(cè)邊沿處于最后一個(gè)調(diào)整周期時(shí)發(fā)揮作用,當(dāng)監(jiān)測(cè)到邊沿慢于本通道輸出時(shí),立即將計(jì)數(shù)器清零,在下一個(gè)周期完成同步;當(dāng)監(jiān)測(cè)到邊沿快于本通道輸出時(shí),同樣立即將計(jì)數(shù)器清零,這時(shí)輸出脈沖寬度變小,在本周期完成同步。

3 驗(yàn)證及分析

3.1 仿真測(cè)試

建立仿真測(cè)試平臺(tái),仿真環(huán)境Questasim10.5e。另外兩個(gè)通道同步脈沖的產(chǎn)生采用與本通道相同的方法,頻率一致,仿真時(shí)使用不同的起始復(fù)位時(shí)間以模擬通道間不同步。由圖5可知,測(cè)試設(shè)定本通道ID為00,即A通道,主控信號(hào)高電平有效,即B通道為主控通道。f_sync_rx為進(jìn)入本通道的B通道同步脈沖及經(jīng)過組合邏輯和排序選擇并緩存后的主控同步脈沖sync_in。

圖6(a)為兩通道的同步脈沖位于多周期調(diào)整范圍,sync_in為緩沖后的主控通道脈沖,將計(jì)數(shù)器數(shù)值以模擬量顯示,單元計(jì)數(shù)器miframe_cnt在每個(gè)調(diào)整周期都被增加了。圖6(b)為經(jīng)過多周期調(diào)整后,進(jìn)入單周期調(diào)整,單元計(jì)數(shù)器miframe_cnt只在最后一個(gè)周期被增加。圖6(c)進(jìn)入單元調(diào)整,脈沖偏差小于單周期調(diào)整增加的時(shí)間。圖6(d)為單元調(diào)整放大的主被控脈沖,調(diào)整后完成同步(脈沖與計(jì)數(shù)器清零邊沿的偏差是同步打拍、濾波等補(bǔ)償?shù)难舆t時(shí)間)。圖7中sync_set_up是以調(diào)整周期為單位計(jì)數(shù)的同步建立時(shí)間,從0計(jì)數(shù),計(jì)數(shù)399時(shí)建立同步,同步時(shí)間為320ms,同步誤差為一個(gè)分頻時(shí)鐘周期,理論同步精度為所使用的分頻時(shí)鐘周期。

3.2 同步建立時(shí)間分析

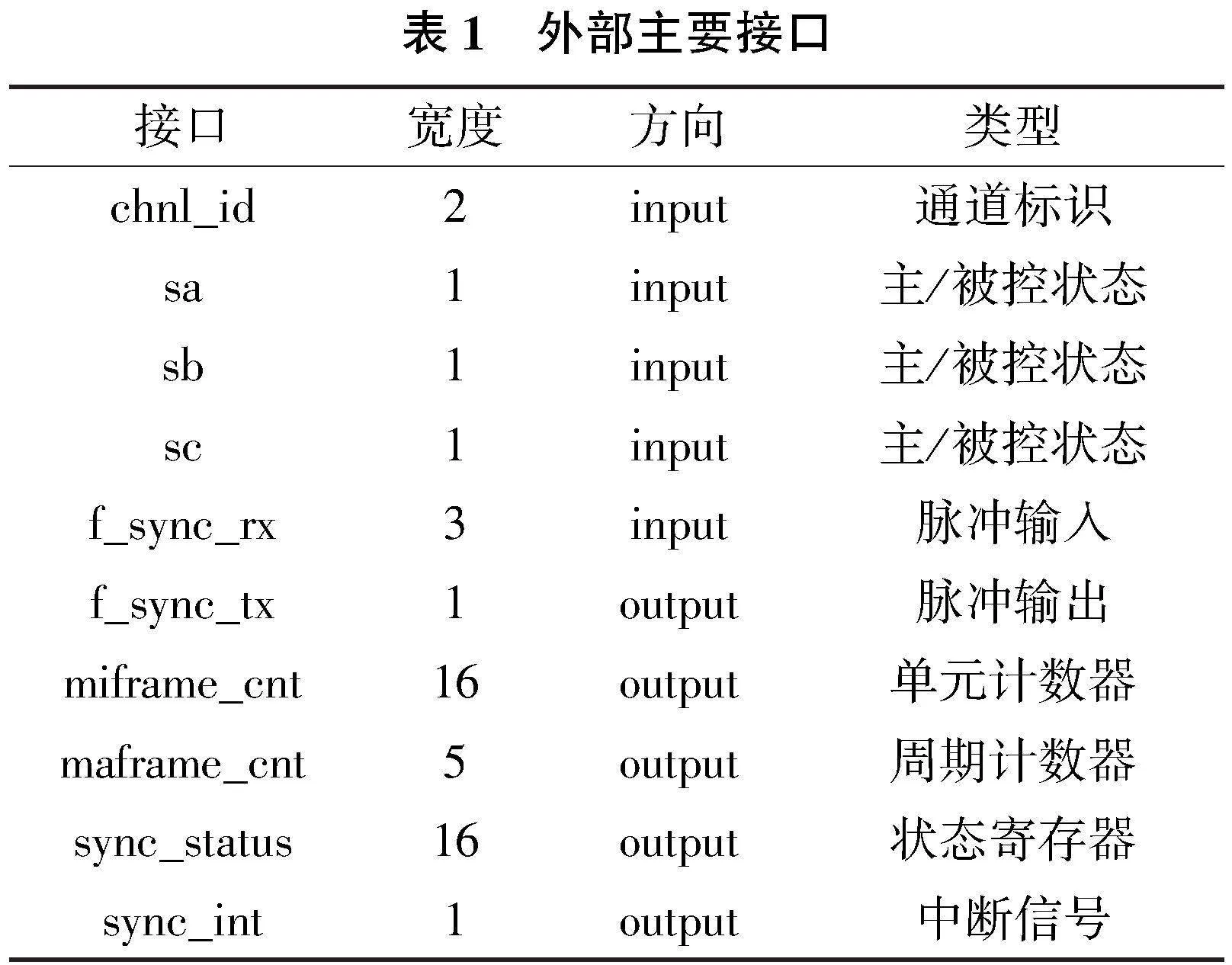

被控脈沖不同步時(shí)只有超前或滯后于主控脈沖兩種情況。這兩種情況對(duì)應(yīng)調(diào)整方案為脈沖周期增加或減少,增加或減少時(shí)最大同步建立時(shí)間相同。本節(jié)分析基于被控脈沖超前時(shí),計(jì)算同步建立時(shí)間。

脈沖同步周期為20ms,則超前最大時(shí)間為同步周期的一半,10ms。本方案采用的多周期調(diào)整增加1.5ms,單周期增加0.06ms,單元調(diào)整范圍為0~0.06ms,單元調(diào)整只需1次,則

式中:a為多周期調(diào)整次數(shù); b為單周期調(diào)整次數(shù),且都為整數(shù);t為單元調(diào)整時(shí)間,同步建立時(shí)間Tsetup為

Tsetup=21.5a+20.06b+(20+t)(6)

使建立時(shí)間最大的a、b取值為6、16,最大同步建立時(shí)間Tsetup=470ms。

4 結(jié)語

1)針對(duì)冗余系統(tǒng)的同步需求,提出一種基于FPGA的硬件同步方法。經(jīng)過排序后獲得主控脈沖,同步過程劃分為多周期調(diào)整、單周期調(diào)整、單元調(diào)整,以主控脈沖為基準(zhǔn)調(diào)整同步偏差。

2)仿真結(jié)果表明,同步精度達(dá)到20ns,最大同步時(shí)間不超過470ms,保證了多通道冗余系統(tǒng)的同步需求。

參考文獻(xiàn):

[1] CHEMASHKIN F Y,ZHILENKOV A. Fault tolerance control in cyber-physical systems[C]. [S.I.]:IEEE,2019.

[2] 高桂軍,王友仁,姚睿. 系統(tǒng)異構(gòu)冗余容錯(cuò)設(shè)計(jì)研究[J]. 傳感器與微系統(tǒng),2007,26(10):25-28.

[3] 毛海杰,李煒,馮小林. 非線性系統(tǒng)主動(dòng)容錯(cuò)控制綜述[J]. 傳感器與微系統(tǒng),2014,33(4):6-9,13.

[4] 簡(jiǎn)榮坤,李冰冰,韓誠(chéng). 智能傳感器故障診斷系統(tǒng)數(shù)據(jù)預(yù)處理方法[J]. 傳感器與微系統(tǒng),2016,35(9):27-29,32.

[5] 馬立偉,王俊雷,林尚飛. 基于FMECA分析的無人收放控制系統(tǒng)冗余策略研究[J]. 機(jī)電工程技術(shù),2022,51(6):92-95.

[6] HAZRA N K,NANDA A K. Component redundancy versus system redundancy in different stochastic orderings[J]. IEEE Transactions on Reliability,2014,63(2):567-582.

[7] LIU X Z,WU C. Fault-tolerant synchronization for nonlinear switching systems with time-varying delay[J]. Nonlinear Analysis:Hybrid Systems,2017,23:91-110.

[8] LIU B,YANG M F,WANG Y,et al. A lightweight data-voting strategy for triple-modular redundant control computers[J]. Science China Technological Sciences,2022,65(2):419-431.

[9] ZHOU S,XIONG G P. Modeling and analysis of task synchronization process based on Petri Net[C]//World Automation Congress. Puerto Vallarta,Mexico:IEEE,2012:267-271.

[10] WANG Y,JIA Z Q,ZHANG M. Research on the computer synchronization of the fault-tolerant system[C]//2020 3rd International Conference on Intelligent Robotic and Control Engineering (IRCE). Oxford,UK:IEEE,2020:18-22.

[11] YANG J Y,HUANG S Y. Process-resilient fault-tolerant delay-locked loop using TMR with dynamic timing correction[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,2022,41(5):1563-1572.

[12] 宋征宇. 運(yùn)載火箭冗余設(shè)計(jì)中的同步控制技術(shù)[J]. 載人航天,2013,19(2):11-16,37.