電化學沉積WS3薄膜及其憶阻特性研究

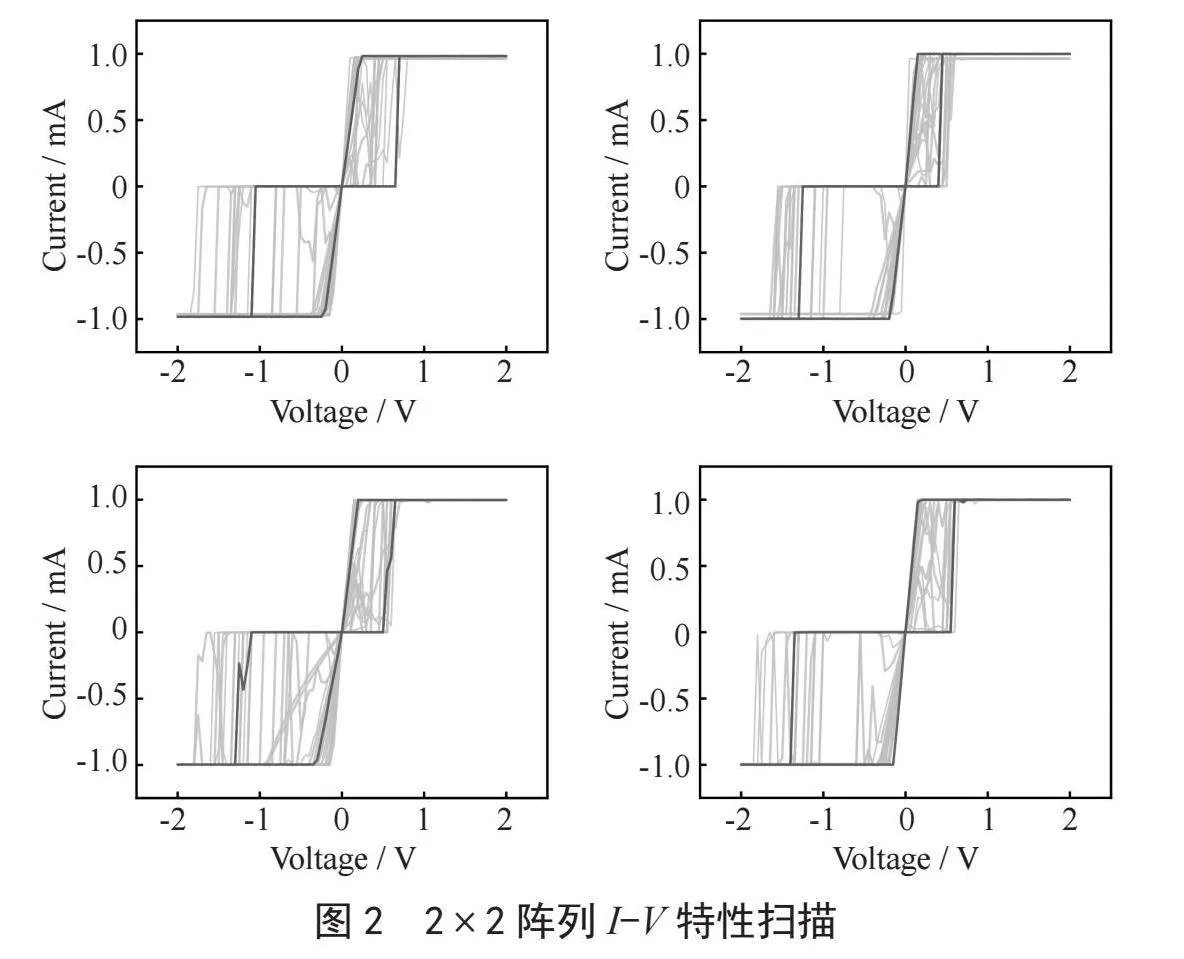

摘 要:對基于二維材料的垂直陣列憶阻器進行了研究。面對二維材料生長窗口狹窄,難以制備大面積單晶等挑戰,通過可控電化學沉積沉積了大面積WS3薄膜。基于WS3薄膜制備了垂直陣列結構憶阻器件。對2×2的4個憶阻器單元進行I-V特性掃描,均展現出了雙極性憶阻特性。開關壽命達1.5×104次,對于仿神經訓練脈沖信號有著明顯的響應。大面積二維材料的制備與穩定的憶阻性能為高集成度憶阻器件提供了關鍵的電學參數與廣闊的應用前景。

關鍵詞:憶阻器;WS3薄膜;陣列;脈沖

中圖分類號:TP212 文獻標識碼:A 文章編號:2096-4706(2024)15-0024-04

Research on Electrochemical Deposition and Memristor Properties of WS3 Thin Film

DUAN Yaoyu, WAN Xi

(Engineering Research Center of the Ministry of Education of IoT Technology Application, Jiangnan University, Wuxi 214122, China)

Abstract: This paper researches a vertical array memristor based on two-dimensional materials. To address challenges like the narrow growth window of two-dimensional materials and the difficulty of producing large-area single crystals, large-area WS3 thin films are deposited through controlled electrochemical deposition. The I-V characteristics of four 2×2 memristor units are scanned, and all of them show bipolar memristor characteristics. The switch life of these devices reach up to 1.5×104 times, and they exhibit a clear response to simulated neural training pulse signals. The achievement of large area two-dimensional materials and the stable performance of the memristor offer crucial electrical parameters and promising application prospect for highly integrated memristor devices.

Keywords: memristor; WS3 thin film; array; pulse

0 引 言

憶阻器在1971年由蔡少棠教授基于電路理論邏輯關系的對稱性提出[1]。由六種不同的數學關系聯系著四個基本的電路變量:電壓v、電流i、電荷q和磁通量φ,并將磁通量與電荷量相關聯,認為憶阻器是除了電阻、電容、電感外的第四個基本電子元件。憶阻器與電阻有著相同的量綱,在特定的電學信號的刺激下,會產生周期性穩定的電阻水平的變換,而目前對憶阻器的研究中,分為高電阻狀態(High resistance state, HRS)和低電阻狀態(Low resistance state, LRS),HRS和LRS又被稱之為關閉狀態(Off State)和開啟狀態(On State)。當LRS不穩定時,復位過程會在電信號刺激關閉時自動發生。當LRS不穩定時,復位過程會在電信號刺激關閉時自動發生。這兩種不同的狀態可以在數字邏輯中表示不同的邏輯狀態,即數字二進制中的0和1,這種有趣的特性使得憶阻器在電子存儲[2-3]、開關器件[4]和人工神經網絡[5-7]等方面產生了廣闊的應用場景。

起初憶阻器都是由三維材料制成的立體結構器件。近年來,二維材料由于其諸多優異的性質逐漸興起,兩者的結合也引起了眾多研究者的關注。然而,對于生長窗口的把握和如何大面積制備二維材料仍然是所面臨的問題之一。本文中,采用電化學沉積的方法沉積了大面積WS3薄膜,并基于WS3薄膜制備了垂直陣列結構憶阻器,具有優異的憶阻性能,為大面積高集成度憶阻器的制備提供了可行性。

1 憶阻器制備

目前半導體行業對于憶阻器最常規的選擇是垂直MIM(Metal/Insulator/Metal)的交叉陣列結構的憶阻器。本實驗采用Ag / WS3 / Ag垂直陣列結構的憶阻器,如圖1所示為MIM憶阻器結構示意圖。底部為一層Ag底電極,中間層為WS3薄膜,頂部為Ag制備的陣列結構頂電極。

切割大小約為1.5 cm×1.5 cm的Si / SiO2襯底。對Si / SiO2襯底進行清洗,將襯底在丙酮溶液中浸泡并進行超聲波清洗,時間為10 min。撈出襯底后將其浸入異丙醇溶液并進行超聲波清洗以去除殘余的丙酮溶液,時間為10 min。取出襯底后使用去離子水沖洗殘余的異丙醇溶液,最后使用氮氣槍吹干。

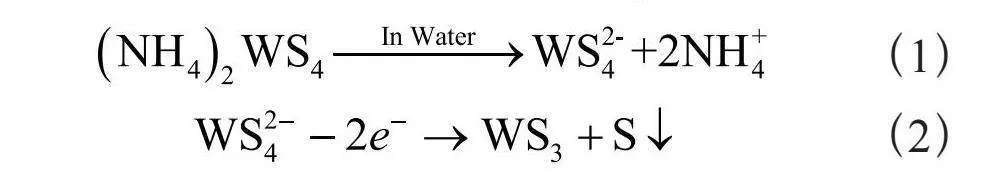

在清洗過后的Si / SiO2襯底上熱蒸發一層約100 nm厚Ag薄膜,Ag具有優異的導電性,可以作為電化學沉積制備WS3薄膜的襯底,同時在垂直憶阻器結構中充當器件的底電極。電化學沉積過程中,使用碳棒作為陰極,Ag襯底作為陽極,將兩個電極同時浸入濃度為10 mg/mL的四硫代鎢酸銨((NH4)2WS4,Sigma-Aldrih,純度為99.9%)水溶液中。選擇電化學工作站的計時電位測定法(Chronopotentiometry, CP)。在水溶液中會發生如式(1)和式(2)所示的化學反應式。通過反應式可以看出,在導電性優異的Ag襯底上可以沉積一定厚度且大面積的WS3薄膜[8]。

(1)

(2)

選擇陽極通入電流密度為500 μA / cm2的直流電流,沉積時間為180 s的WS3薄膜來制備Ag / WS3 / Ag憶阻器。通過掩膜在WS3薄膜上熱蒸發厚度約為100 nm的Ag,用作憶阻器的頂電極,形狀為如圖1所示的方形陣列結構,大小為0.3 mm×0.3 mm,間距為0.3 mm。完成Ag / WS3 / Ag垂直陣列結構憶阻器的制備。

2 測試結果和分析

2.1 憶阻器I-V特性測試

在室溫下對憶阻器2×2陣列的4個憶阻器單元進行0 V→2 V→-2 V→0 V的I-V特性曲線掃描,測試結果如圖2所示。在測試的過程中,施加斜坡電壓應力(Ramped Voltage Stresses, RVS)[9],將電壓刺激信號施加在了頂層Ag電極上。其中每個憶阻器單元進行了20次左右的循環掃描測試。可以看出Ag / WS3 / Ag憶阻器經歷了20次循環操作后依然能表現出良好的雙極型阻變行為。Ag / WS3 / Ag憶阻器的初始狀態為高阻態,將電壓從0 V掃描至+2 V,過程中,器件的電流先是以一個緩慢的狀態線性增加,直至電壓到達某一閾值后,電流突然急劇增加,這是期間內部的導電通道已然形成,憶阻器的電阻狀態由高阻態轉換至低阻態,實現了置位(Set)過程。當電壓從0 V掃描至-2 V時,與置位過程相似,在某一個電壓閾值處,器件的電流驟減,憶阻器的電阻狀態由低阻態轉換至高阻態,實現了復位(Reset)過程。需要注意的是,憶阻器在進行首次I-V特性掃描的時候,需要設置一個比常規測試電壓更大電壓大的電信號來對憶阻器進行寫入,也稱作Forming Voltege。

對數十條Ag / WS3 / Ag憶阻器的捏滯回線進行觀測統計,可以大概得出Ag / WS3 / Ag憶阻器的置位電壓約為0.6 V,復位電壓約為-1.3 V,表明了憶阻器擁有較為穩定的運行電壓,且功耗較低。

為了防止電流過大而燒損器件,在憶阻器的測試進行限流是十分必要的。本實驗的I-V特性測試中使用了Keithley 4200-SCS參數分析儀的SMU源測量單元,自帶限流功能。圖1中所示的4個憶阻器單元中,對器件均限制了1 mA的飽和電流。本實驗中選擇了制備面積相對較大的電極,測試結果表現,在Ag /WS3 / Ag憶阻器中,中間層所采用電化學沉積的WS3薄膜具有很好的均勻度,大面積的制備與較低的功耗,使得Ag / WS3 / Ag憶阻器在后續的低功耗、高集成度器件中有著可觀的前景。

2.2 憶阻器耐久性與穩定性測試

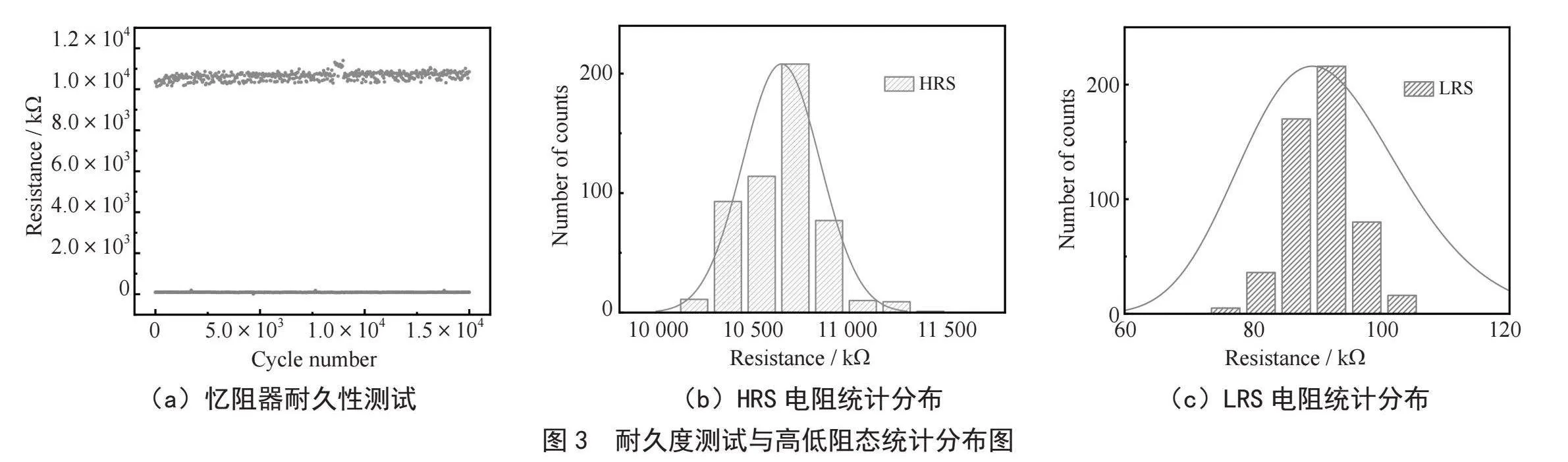

穩定性與耐久性通常表現為憶阻器最關鍵的性質之一,憶阻器穩定性與耐久性的測試中,可以通過施加脈沖電壓應力(Pluse Voltage Stresses, PVS)來對憶阻器進行高阻態與低阻態的切換。通常采用比置位電壓(Set Voltage)與復位電壓(Reset Voltage)更大的脈沖電壓應力來激勵憶阻器進行高低阻態的狀態切換,對憶阻器施加正脈沖電壓應力時,憶阻器發生置位過程,進入低阻態。對憶阻器施加負脈沖電壓應力時,憶阻器發生復位過程,狀態切換回高阻態。在施加的脈沖電壓應力后面插入更小的讀取電壓來讀取憶阻器的阻值狀態。將讀取電壓與過程中讀取電流的值相除,則可以得出憶阻器在不同阻態的阻值,此過程一般由測試設備自動計算。通常測試中都采用矩形PVS來對憶阻器進行測試。

如圖3所示為對憶阻器進行長期增強與長期抑制測試,對Ag / WS3 / Ag憶阻器施加了2 V與-2 V的脈沖電壓應力,脈沖信號的幅值大于上文中統計所得的0.6 V的置位電壓與-1.3 V的復位電壓,確保Ag / WS3 / Ag憶阻器能在脈沖電壓應力的激勵下進行高阻態與低阻態的切換。施加的脈沖信號脈沖寬度為50 ms。在每30個脈沖后加入一個讀取脈沖,讀取脈沖幅值為0.1 V,脈沖寬度為50 ms,進行500次循環。以此對Ag / WS3 / Ag憶阻器施加15 000個脈沖電壓應力后,憶阻器仍能保持穩定的開關狀態。對Ag / WS3 / Ag憶阻器15 000次脈沖序列測試中高阻態的阻值與低阻態的阻值進行統計分布,可以得出Ag / WS3 / Ag憶阻器在高阻態時的阻值約為1.08×107 Ω,在低阻態時的阻值約為9×104 Ω。開關比高達120左右。表明Ag / WS3 / Ag憶阻器具有優異的穩定性與耐久性。

2.3 憶阻器脈沖特性測試

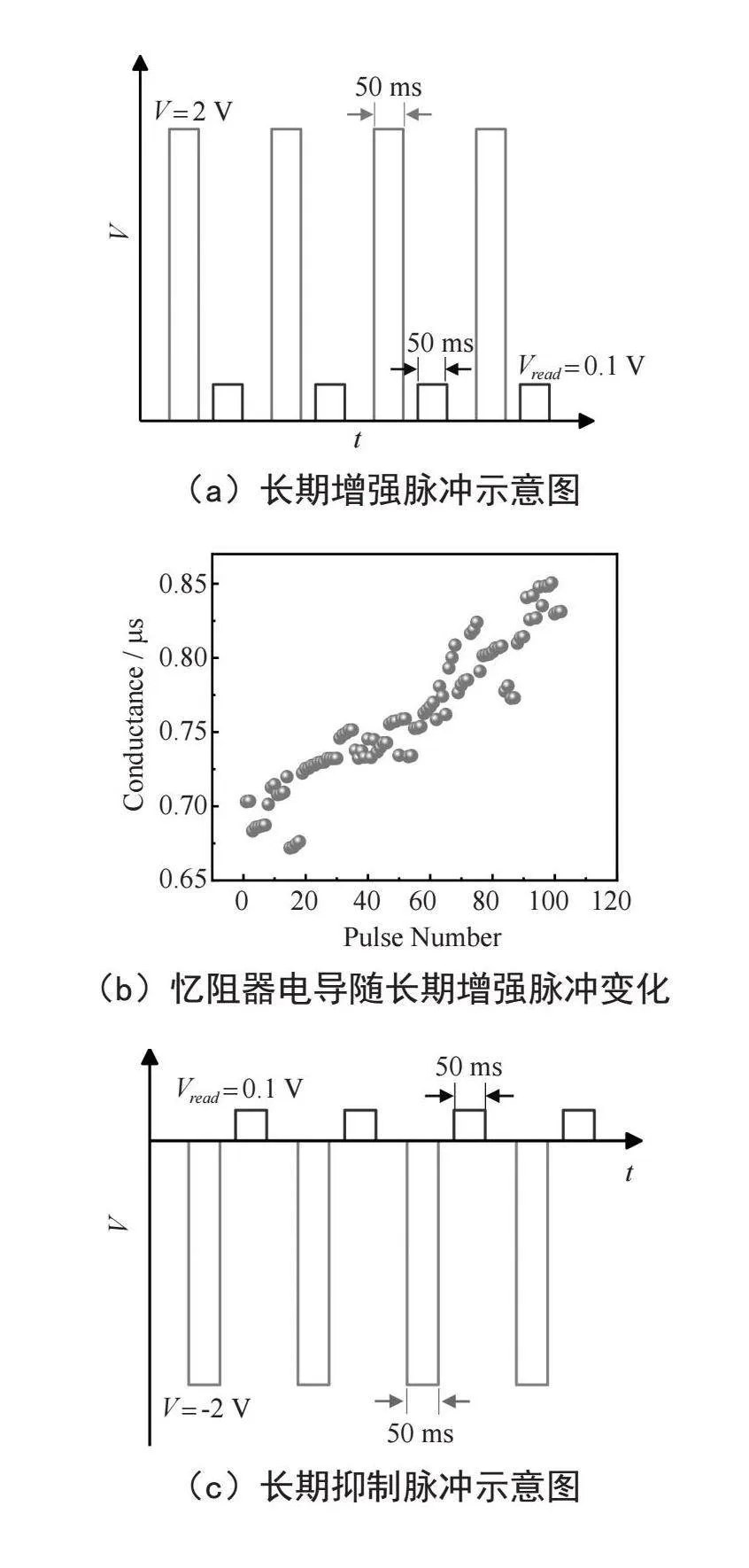

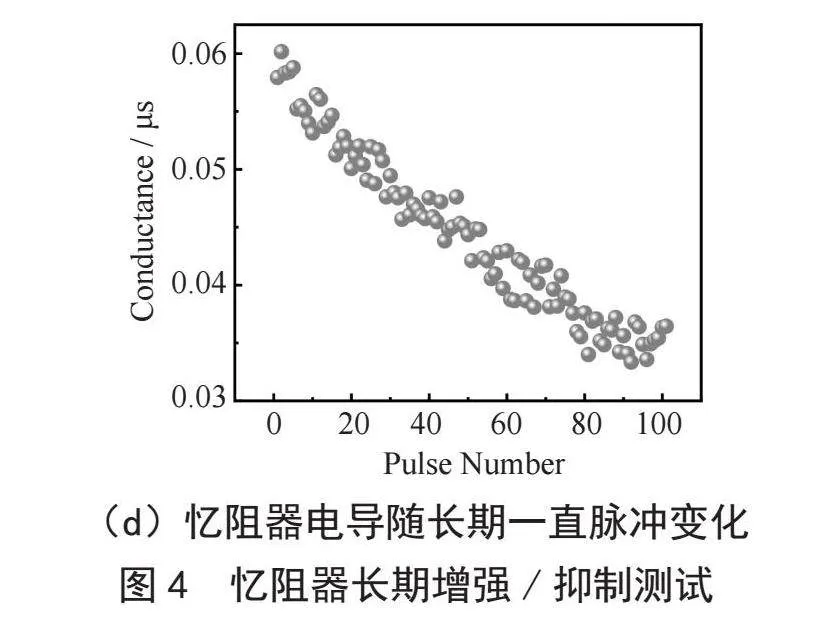

憶阻器對脈沖有著特殊的響應且可以制作為垂直陣列結構,作為仿人工突觸型器件。長期增強(Long-Term Potentiation, LTP)和長期抑制(Long-Term Depression, LTD)之間的對稱突出權重更新特性是設計仿人工突觸器件的關鍵特性,可以直接影響神經形態計算與的學習精度[10]。可以通過編程脈沖幅值、脈沖寬度和脈沖數量等PVS的參數,來測量憶阻器的長期可塑性。

圖4(a)為編程的正脈沖序列示意圖。脈沖幅值為2 V,脈沖寬度為50 ms,在每個脈沖信號后跟隨一個讀取脈沖,幅值為0.1 V,脈沖寬度為50 ms。圖4(c)為編程的負脈沖序列示意圖。脈沖幅值為-2 V,脈沖寬度為50 ms,在每個脈沖信號后跟隨一個讀取脈沖,幅值為0.1V,脈沖寬度為50 ms。每個增強和抑制脈沖各施加100個循環。Ag / WS3 / Ag憶阻器在雙向脈沖的刺激下獲得了雙向開關的行為。如圖8(b)所示,長期增強脈沖會逐漸增加憶阻器電導,器件被置位為低阻態,電導被設置為由0.65 μs逐漸增強至0.85 μs的導通狀態。如圖8(d)所示,長期抑制脈沖會逐漸減小憶阻器電導,器件被重置為高阻態,電導被設置為由0.06 μs逐漸降低至0.04 μs的導通狀態。表明由Ag / WS3 / Ag結構制成的憶阻器可以支持重要的神經突觸功能,與神經元通過離子流來調節突觸權重高度相似。

3 結 論

本研究采用電化學沉積技術,在導電Ag襯底上沉積了厘米級別面積的WS3薄膜,制備了垂直結構陣列憶阻器。對2×2的4個憶阻器單元進行了測試。每個憶阻器單元均表現出了良好的憶阻特性與穩定性。其置位電壓約為0.6 V,復位電壓約為-1.3 V,器件開關運行穩定且具有較低的功耗。在正負脈沖應力的刺激下,器件的高低阻態切換次數可高達1.5×104次,開關比高達120。對憶阻器施加連續增強和連續抑制的脈沖信號來調控器件的電導,器件展現出了明顯的響應。Ag / WS3 / Ag憶阻器擁有良好的憶阻性能、耐久性以及神經突觸響應。大面積的二維材料制備與垂直陣列結構使其在超高集成度的電子開關、神經網絡與仿人工突觸器件等方面有著廣闊的發展前景。

參考文獻:

[1] CHUA L. Memristor-the Missing Circuit Element [J].IEEE Transactions on Circuit Theory,1971,18(5):507-519.

[2] 蔡振揚,劉苡萌,徐紅梅.一種基于憶阻器的2T2M存儲陣列的設計研究 [J].延邊大學學報:自然科學版,2023,49(3):257-261.

[3] 吳磊.基于氧化物憶阻器的阻變存儲與神經突觸特性研究 [D].西安:西安電子科技大學,2020.

[4] KIM M,PALLECCHI E,GE R,et al. Analogue Switches Made from Boron Nitride Monolayers for Application in 5G and Terahertz Communication Systems [J].Nature Electronics,2020,3(8):479-485.

[5] 毛成烈,高小玉,南海燕.二維TMC憶阻器在神經形態計算中的研究進展 [J].半導體技術,2024,49(2):109-122.

[6] WEI W,SUN H,DONG X,et al. A Neotype Self-Rectifying Cu3SnS4-MoO3 Synaptic Memristor for Neuromorphic Applications [J/OL].Chemical Engineering Journal,2024,482:148848(2024-02-15).https://doi.org/10.1016/j.cej.2024.148848.

[7] 黃鶴鳴.基于過渡金屬氧化物憶阻器的人工突觸、人工神經元及人工神經網絡 [D].武漢:華中科技大學,2021.

[8] WAN X,CHEN K,CHEN Z,et al. Controlled Electrochemical Deposition of Large-Area MoS2 on Graphene for High-Responsivity Photodetectors [J/OL].Advanced Functional Materials,2017,27(19):1603998(2017-01-11).https://doi.org/10.1002/adfm.201603998.

[9] LANZA M,WASER R,IELMINI D,et al. Standards for the Characterization of Endurance in Resistive Switching Devices [J].ACS Nano,2021,15(11):17214-17231.

[10] KIM M,YOO K,JEON S P,et al. The Effect of Multi-Layer Stacking Sequence of TiO(x) Active Layers on the Resistive-Switching Characteristics of Memristor Devices [J/OL].Micromachines(Basel),2020,11(2):154(2020-01-30).https://doi.org/10.3390/mi11020154.

作者簡介:段堯禹(1995.07—),男,漢族,吉林白山人,碩士在讀,研究方向:二維材料;通訊作者:萬茜(1985.10—),男,漢族,江蘇無錫人,副教授,博士,研究方向:二維材料。